Problems 1-6: Pipelining

Problems 1 and 2 assume that instructions for a given program, executed by a pipelined processor, are broken down as follows:

| ADD | BEQ | LW | SW | |

| a. | 40% | 30% | 25% | 5% |

| b. | 60% | 10% | 20% | 10% |

1. Assuming there are no stalls and that 60% of conditional branches are taken, in what percentage of clock cycles does the BEQ actually cause execution to branch?

2. Assuming there are no stalls, in what percentage of all cycles are needed to access data memory?

Problems 3-5 assume a processor with datapath consisting of the following stages and stage latencies:

| IF | ID | EX | MEM | WB | |

| a. | 200ps | 120ps | 150ps | 190ps | 100ps |

| b. | 150ps | 200ps | 200ps | 200ps | 100ps |

3. In the absence of pipelining, what is the cycle time for a single instruction?

4. What is the cycle time for a single stage, if this same datapath were to be pipelined?

5. Assuming no stalls, what is the speedup achieved by pipelining these stages (once the pipeline is full and maximum throughput achieved)?

6. Assume the ID stage stalls 25% of the time. What is the effective CPI?

Problem 7: Cache Design

|

Set

Index |

Set (1 bit) |

Dirty |

Valid |

Tag (20 bits) |

Data |

|

00 |

0 |

0 |

0 |

0x00000 |

0x00000000 0x00000000 0x00000000 0x00000000 |

|

0 |

0 |

0 |

0x00000 |

0x00000000 0x00000000 0x00000000 0x00000000 |

|

|

01 |

0 |

0 |

0 |

0x00000 |

0x00000000 0x00000000 0x00000000 0x00000000 |

|

0 |

0 |

0 |

0x00000 |

0x00000000 0x00000000 0x00000000 0x00000000 |

|

|

… |

… |

… |

… |

… |

… |

|

FF |

0 |

0 |

0 |

0x00000 |

0x00000000 0x00000000 0x00000000 0x00000000 |

|

0 |

0 |

0 |

0x00000 |

0x00000000 0x00000000 0x00000000 0x00000000 |

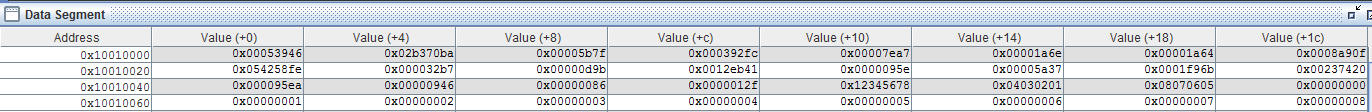

For a 2-way set-associative cache model (above), determine the content of the cache after each of the following instructions are executed (note that you may have to replicate and expand the table to include additional set indices)

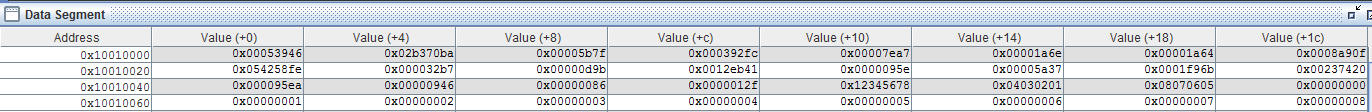

lw $t0, ($t1) #

t1=0x1001 0000

sw $t0, 4($t1)

lw $t0, ($t2) # t2=0x1001 0020

sw $t0, 8($t2)

lw $t0, ($t1) # t1=0x1001 0044

sw $t0, ($t1)

lw $t0, ($t1) # t1=0x1001 0060