Last updated 1/11/21

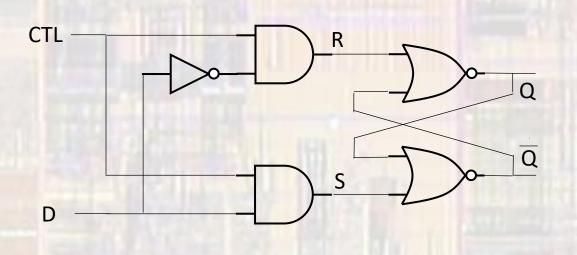

• D Latch (data)

CE 1911

#### **Level Sensitive Latch**

CTL = low → latched CTL = high → Transfer

| D   | Q |

|-----|---|

| Clk |   |

| CTL | D | Q         |

|-----|---|-----------|

| 0   | X | $Q_{old}$ |

| 1   | D | D         |

© tj

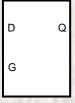

• D Flip-Flop (data)

- Sequential

- Bi-stable circuit

- Synchronous outputs change on a (rising) clk edge

- Output changes limited to specific input conditions

- D Flip-Flop (data)

- Sequential

- Bi-stable circuit

- Synchronous outputs change on a (rising) clk edge

- Output changes limited to specific input conditions

bubble: negative edge triggered (falling)

CE 1911 4 © tj

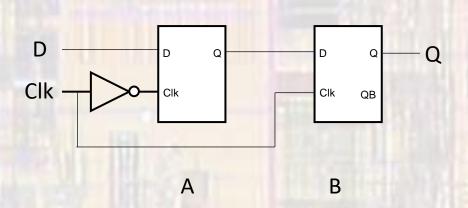

**D-Latch**

| CTL<br>CLK | D | Q         |

|------------|---|-----------|

| 0          | X | $Q_{old}$ |

| 1          | D | D         |

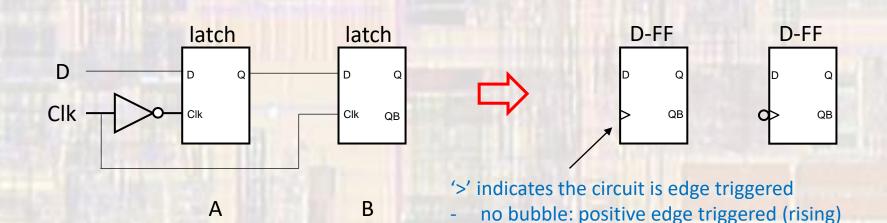

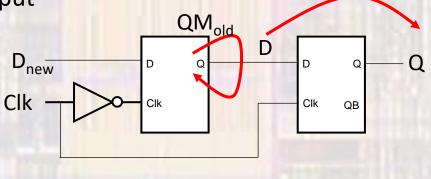

• D Flip-Flop (data)

- Clock low after a short time

- A is enabled and passes D to it's Q output

- B is in latch mode and retains it's state QS<sub>old</sub>

| D | Clk | Q                 |

|---|-----|-------------------|

| Х | 0   | QS <sub>old</sub> |

CE 1911 5 © tj

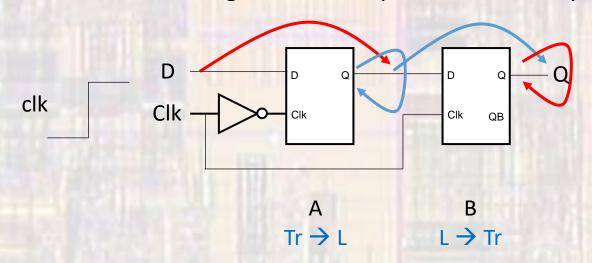

D Flip-Flop (data)

Clock high – after a short time

A is latched and retains it's state – Qm<sub>old</sub> (original value of D)

B is in transfer mode and would have already passed D to it's Q

output

| D | Clk | Q                                        |

|---|-----|------------------------------------------|

| x | 0   | $Q_{old}$                                |

| x | 1   | QM <sub>old</sub><br>(D <sub>old</sub> ) |

A B

latched transfer

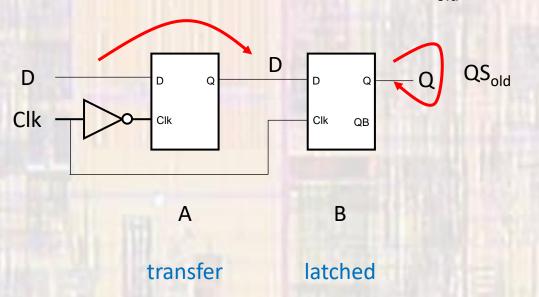

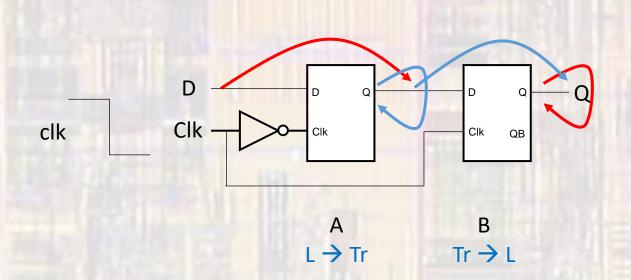

- D Flip-Flop (data)

- Clock Low → High

- D has previously been passed to the intermediate node

- When clk transitions high, the intermediate value (D) is passed to the output while simultaneously the A becomes latched

- Further changes of the D input are blocked by the latched A

| D | Clk        | Q          |

|---|------------|------------|

| X | 0          | $Q_{old}$  |

| X | 1          | $QM_{old}$ |

| D | $\uparrow$ | D          |

D Flip-Flop (data)

- Clock High → Low

- The output is latched by the B

The new D input is allowed to transfer to the intermediate node but

no further

| D | Clk          | Q          |

|---|--------------|------------|

| Х | 0            | $Q_{old}$  |

| X | 1            | $QM_{old}$ |

| D | $\uparrow$   | D          |

| X | $\downarrow$ | $QM_{old}$ |

D Flip-Flop (data)

- Truth Table

- Positive Edge Triggered D Flip-Flop

- (typically, just called a D Flip-flop)

| D | Clk          | Q                  |

|---|--------------|--------------------|

| Х | 0            | $Q_{old}$          |

| X | 1            | $\mathbf{Q}_{old}$ |

| D | $\uparrow$   | D                  |

| Х | $\downarrow$ | $Q_{old}$          |