## CE 1911

## Homework 4

1 – Write behavioral VHDL code for a D-FF with asynchronous resetb and synchronous set. Provide code, test-bench and a simulation 50pts

```

-- created 2/1/2018

-- tj

___

-- rev 0

-- special DFF with synchronous set

_ _

-- Inputs: clk, rstb, din, set

-- Outputs: q

___

library ieee;

use ieee std_logic_1164 all;

entity dffwS is

port (

i_clk : in std_logic;

i_rstb : in std_logic;

i_din : in std_logic;

i_set : in std_logic;

o_q : out std_logic

):

end entity;

architecture behavioral of dffwS is

architecture

~14 lines

```

testbench

-- created: 1/26/18 -- by: johnsontimoj -- rev: 0 Clock process -- testbench for dff with set -- of dffwS.vhdl library ieee; use ieee std\_logic\_1164 all; entity dffwS\_tb is -- no entry - testbench end entity; architecture testbench of dffwS\_tb is Reset process signal CLK: std\_logic; signal RSTB: std\_logic; signal DIN: std\_logic; signal SET: std\_logic; signal Q: std\_logic; -- Run process run: process -- note - no sensitivity constant PER: time := 20 ns; begin \_\_\_\_\_ \_\_\_\_\_ -- Initialize inputs -- Component prototype DIN <= '0'; SET <= '0'; ------COMPONENT dffws PORT wait for 3\*PER; -- wait for reset ( i\_clk : IN STD\_LOGIC; i\_rstb : IN STD\_LOGIC; i\_din : IN STD\_LOGIC; i\_set : IN STD\_LOGIC; o\_q : OUT STD\_LOGIC -- verify normal operation DIN <= '1'; wait for 3\*PER; DIN <= '0'; wait for 3\*PER; DIN <= '1'; wait for 3\*PER; DIN <= '0'; wait for 3\*PER; ); END COMPONENT; -- verify set operation SET <= '1': DIN <= '1'; wait for 3\*PER; DIN <= '0'; wait for 3\*PER; begin ------- Device under test (DUT) -- verify normal operation \_\_\_\_\_ SET <= '0'; SEl <= '1'; wait for 3\*PER; DIN <= '0'; wait for 3\*PER; DIN <= '1'; wait for 3\*PER;</pre> DUT: dffwS port map( i\_clk => CLK, i\_rstb => RSTB, DIN <= '0'; wait for 3\*PER; i\_din => DIN, end process run; i\_set => SET, o\_q ); => 0 \_\_\_\_\_ -- End test processes \_\_\_\_\_ -- Test processes end architecture:

50pts

1 – Write behavioral VHDL code for a D-FF with asynchronous resetb and

synchronous set. Provide code, test-bench and a simulation

1 – Write behavioral VHDL code for a D-FF with asynchronous resetb and synchronous set. Provide code, schematic, test-bench and a simulation 50pts

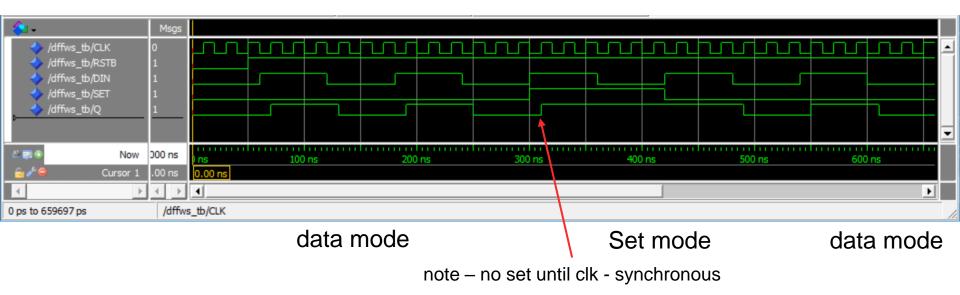

## Simulation Results

2 – Write behavioral VHDL code for a special new FlipFlop you have conceived of – this FlipFlop has a second data input called Toggle(T). When T is low, the DFF operates normally, when T is high, the DFF ignores the D input and synchronously toggles the output. Provide code and a simulation 50pts

> -- created 2/1/2018 -- ti -- rev 0 -- special DFF with toggle mode -- Inputs: clk, rstb, din, t -- Outputs: q library ieee; use ieee std\_logic\_1164 all; entity dffwT is port ( i\_clk : in std\_logic; i\_rstb : in std\_logic; i\_din : in std\_logic; i\_t : in std\_logic; o\_q : out std\_logic ); end entity; architecture behavioral of dffwT is architecture ~14 lines

2 – Write behavioral VHDL code for a special new FlipFlop you have conceived of – this FlipFlop has a second data input called Toggle(T). When T is low, the DFF operates normally, when T is high, the DFF ignores the D input and synchronously toggles the output. Provide code and a simulation 50pts

testbench

```

-- Run process

run: process -- note - no sensitivity list allowed

begin

-- Initialize inputs

DIN <= '0';

T <= '0';

wait for 2*PER; -- wait for reset

-- verify normal operation

DIN <= '1'; wait for 3*PER;

DIN <= '0'; wait for 3*PER;

DIN <= '1'; wait for 3*PER;

DIN <= '0': wait for 3*PER:

-- verify toggle operation

T <= '1';

DIN <= '1'; wait for 4*PER;

DIN <= '0': wait for 4*PER:

-- verify normal operation

T <= '0':

DIN <= '1'; wait for 3*PER;

DIN <= '0'; wait for 3*PER;

DIN <= '1'; wait for 3*PER;

DIN <= '0'; wait for 3*PER;

end process run;

-- End test processes

end architecture:

```

2 – Write behavioral VHDL code for a special new FlipFlop you have conceived of – this FlipFlop has a second data input called Toggle(T). When T is low, the DFF operates normally, when T is high, the DFF ignores the D input and synchronously toggles the output. Provide code and a simulation 50pts

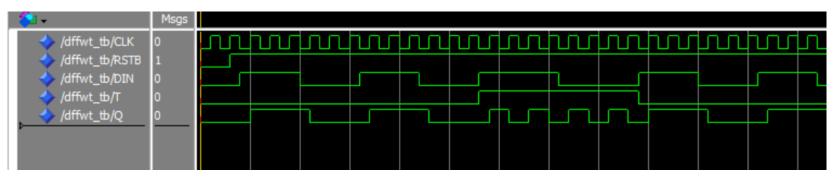

**Simulation Results**

data mode

toggle mode

data mode