## Lab8 - Part2

```

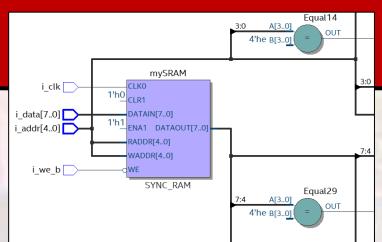

∃entity lab8_part2 is

port(

i_clk:

std_logic;

i we b:

std_logic;

i_addr:

std_logic_vector(4 downto 0);

std_logic_vector(7 downto 0);

o_addr_sseg_A: out

std_logic_vector(6 downto 0);

std_logic_vector(6 downto 0):

o_addr_sseg_B: out

o data ssed E: out

std_logic_vector(6 downto 0);

o_data_sseg_F: out

std_logic_vector(6 downto 0)

end;

```

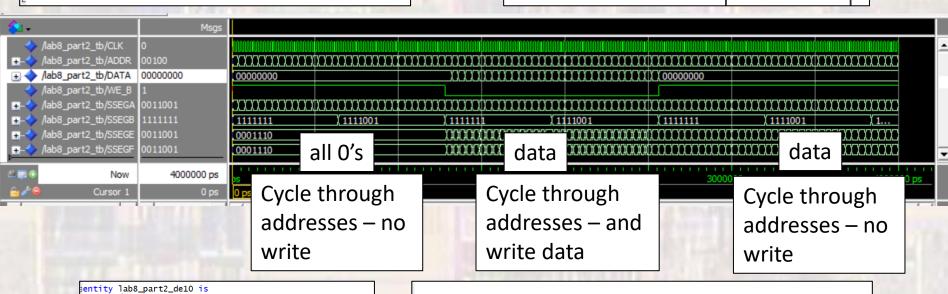

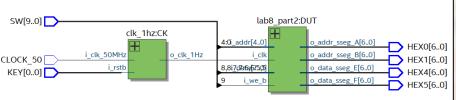

Only 4 data input switches but data is 8 bits wide I doubled up on the input bits b3 b2 b1 b0 to form the data input b3 b3 b2 b1 b1 b0 b0 e.g. if I input 1010, I store 11001100 and read out CC

CE 1911