## Last updated 1/26/21

- Flash Memory Flash, Nand Flash, Nor Flash

- Key Attributes

- Sequential vs. Random Access

- Read only vs. Read/Write imited write

- Static s. Dynamic

- Volatile vs.non-Volatile

- Key Measures

- Density +

- Speed

- Power

- Cost / bit +

- Flash Memory basics

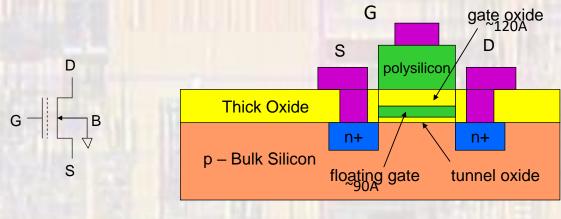

- Memory cell (1 bit) is based on charge stored on a floating capacitor

- The capacitor modifies the threshold voltage of a MOSFET

- with negative charge stored need higher gate voltage to turn on the MOSFET

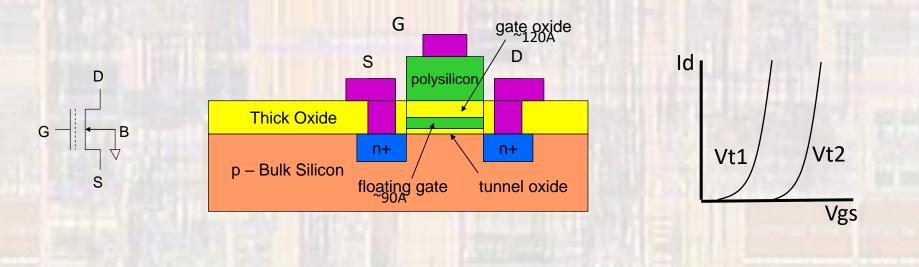

- Creates 2 possible threshold voltages

Different for NOR and NAND

- Flash Memory NOR

- Creates 2 possible threshold voltages

Vth High is required to turn on the MOSFET if charge is stored Vth Low is required to turn on the MOSFET if no charge is stored

- Flash Memory NOR

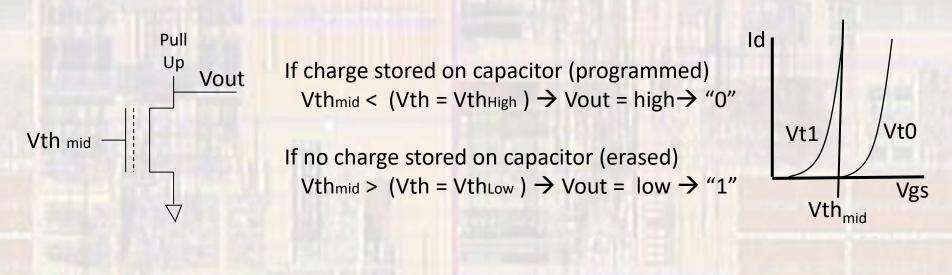

- Cell read

- Place a voltage on the gate midway between Vth High and Vth Low

- Use the circuit to determine if the MOSFET is on or off

- Erased state no charge stored = "1"

- Programmed state charge stored = "0"

- Flash Memory

- Programming

- All cells start out with no charge stored = "1"

- Individual cells can be programmed to "0"

- A block erase is required to change cells from "0" to "1"

- Eg.

byte: 1011 1100 → 1000 1100

byte: 1011 1100 ¥1111 1100

Flash Memory

- NAND Flash

- Page Write

- Block Erase

- More dense

- Fast (required) sequential access

- Used as file storage memory (Flash Drives)

- NOR Flash

- Byte/word Write

- Block Erase

- Less dense

- Fast random access

- Used as program memory

- Flash Memory

- Damage wear out

- The tunneling process damages the oxide layer

- Some electrons get trapped in the oxide

- Physical damage to the lattice

- Limits the number of write/erase cycles

- 10K 1M cycles

- Wear leveling

- Remap the external addresses to new physical blocks on erases

- Dynamic do this as changes occur

- Static do this to little used blocks to make them available

- Allows all blocks to approach their failure limit

- Flash Memory

- Multi-Level Cell

- Instead of just having 2 threshold voltages allow for 4 or 8

- 4  $\rightarrow$  2 bit MLC, 8  $\rightarrow$  3bit MLC

- All aspects of the design get harder (programming, read, wear leveling, speed) → ECC

- Error Correction Coding ECC

- Additional bits are used to detect and correct bit level errors in a word

- Other Technologies

- Phase Change Memory PRAM

- Ferro-Magnetic Ram FeRAM

- Magneto-resistive Ram MRAM