Last updated 1/25/21

- Dynamic Random Access Memory DRAM

- Synchronous DRAM SDRAM

- Key Attributes

- Sequential vs. Random Access

- Read only vs. Read/Write

- Static vs. Dynamic

- Volatile vs. non-Volatile

- Key Measures

- Density +

- Speed

- Power

- Cost / bit +

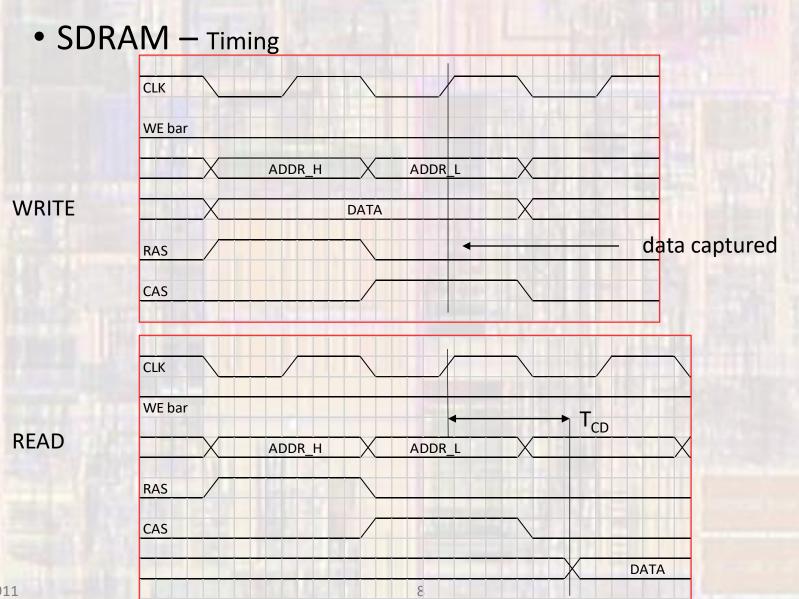

- DRAM/SDRAM Synchronous Dynamic Random Access Memory

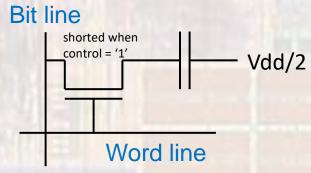

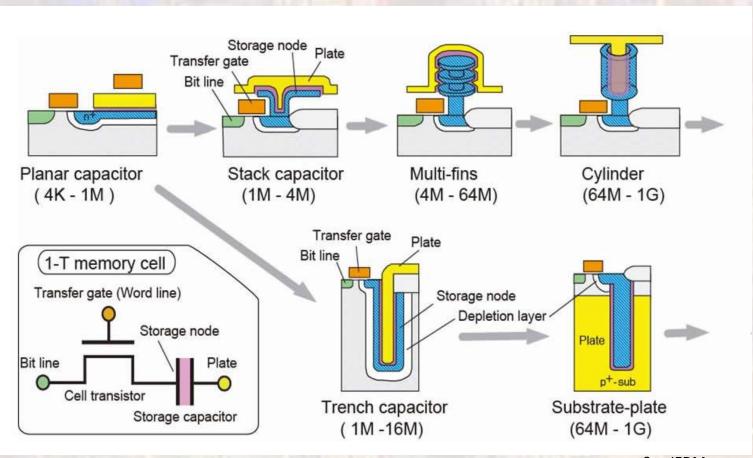

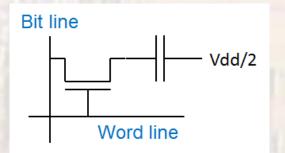

- Memory cell (1 bit) is based on capacitor charge storage

- Bit value decays over time

- must be recharged called a refresh cycle

- Standard SDRAM transfers 1 word each array access

- DDR double data rate transfers 2 words each array access

- DDR2, DDR3, DDR4 transfer 4,8,16 words each array access

- Medium speed

- Highest density

- Used as main memory

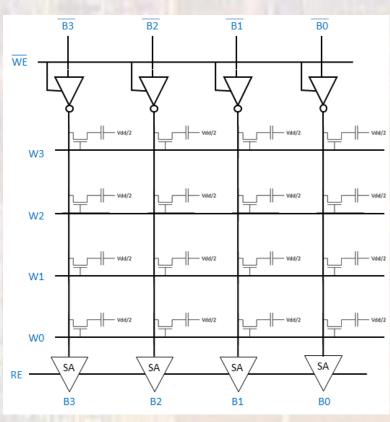

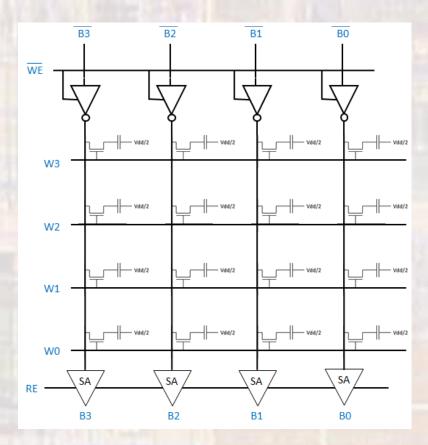

• SDRAM - Cell

CE 1911

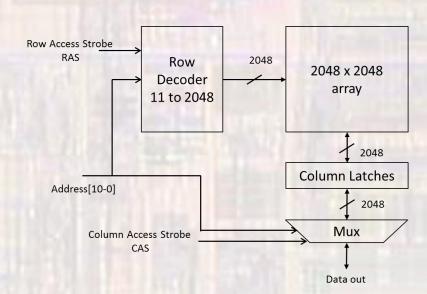

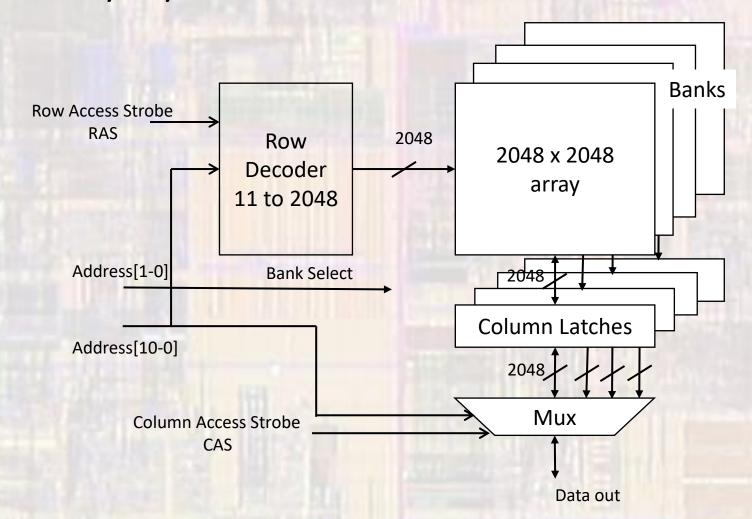

- General Memory Topology

- Reduce I/O by sharing the address inputs between Row addresses and Column addresses

- 22 bit address → 12 bit address + RAS and CAS

- RAS Row Address Strobe (current address is for row decode)

- CAS Column Address Strobe (current address is for column decode) **ADDRESS** 12 12 000 RAS-EN EN 10 CAS

4 bit output

© ti

#### Write

- Read Enable (RE) disabled (low)

- Place B0, B1, B2, B3 on inputs (data in)

- Apply Address (RAS then CAS)

- Select the desired word line (high)

- Select the desired column to input to

- Strobe (clk) write enable bar (WE) low

- Bit lines write to the bit cell capacitors

#### 4 bits of 1 column

#### Read

- Write enable bar (WE) high

- inverters tristated

- Read Enable (RE) high

- Apply Address (RAS then CAS)

- Select the desired word line (high)

- Select the desired column to output

- Sense amplifiers read the value of the capacitors

- Clk to output the value

- The read process is destructive!

- WHY?

#### 4 bits of 1 column

CE 1911

© tj

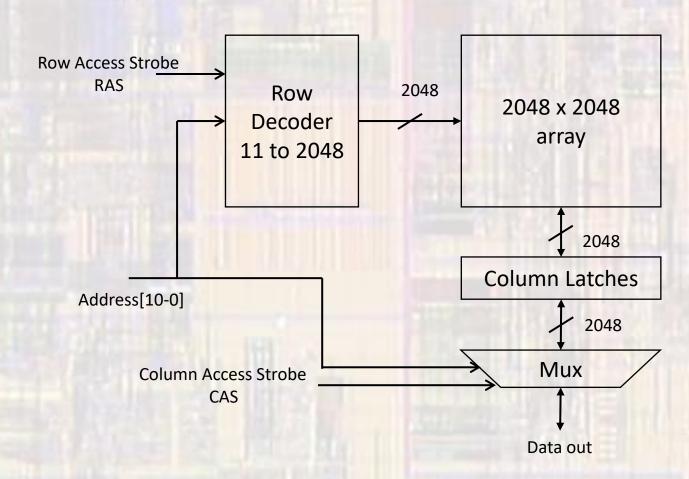

- SDRAM Complex Configuration

- 4Mb in a x1 configuration

- SDRAM Complex Configuration

- Random Access

- 4M bits → 22 address bits

- Operation

- Place upper 11 bits on address bus

- Strobe RAS

- 2048 bits are latched

- Place lower 11 bits on address bus

- Strobe CAS

- Selected bit is fed out

Refresh

- Operation

- Controller selects a row address Read

- 2048 bits are latched

- The read circuit also re-writes the DRAM cells at the same time

- Burst Operation

- 4M bits → 22 address bits

- Operation

- Place upper 11 bits on address bus

- Strobe RAS

- 2048 bits are latched

- Place lower 11 bits on address bus

- Strobe CAS

- Selected bit is fed out

- On-chip Automatically Increment address latch

- Next clock

- Next bit is fed out

- ...

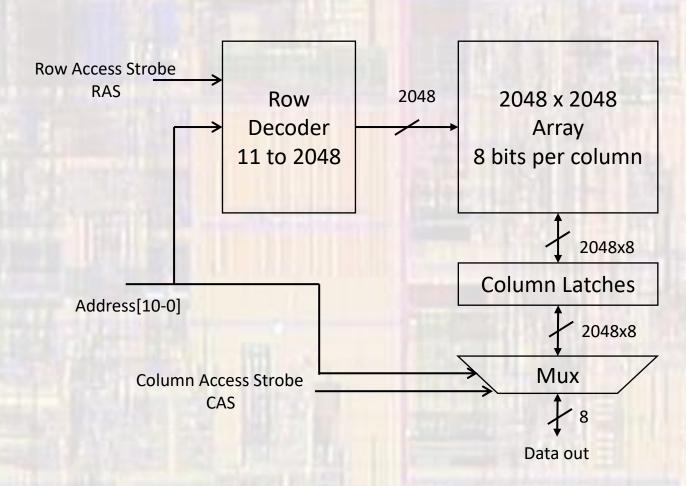

Array Layout – 4M X 8 DRAM

Array Layout – 16M X 1 DRAM

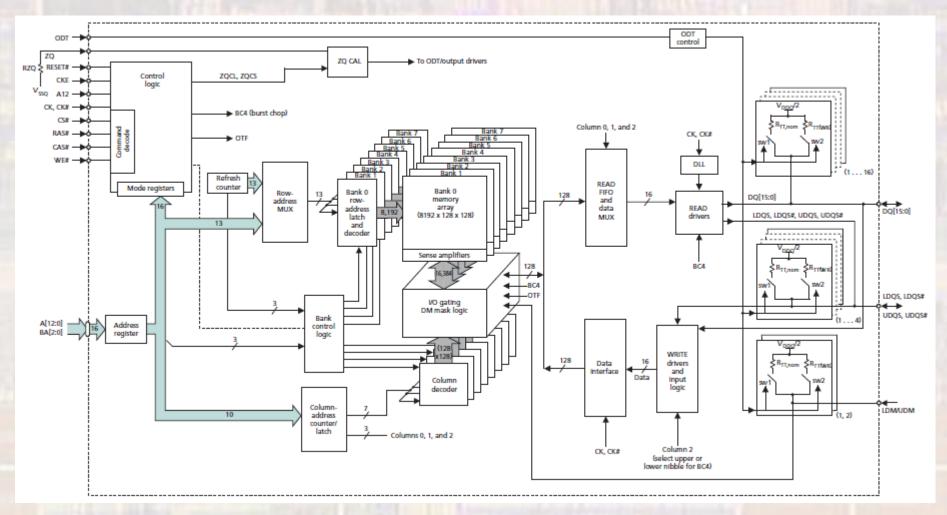

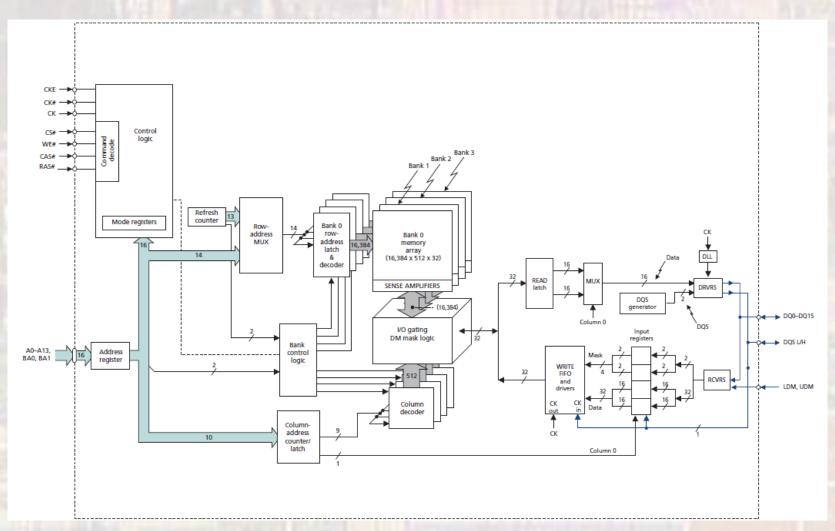

#### 1Gb DDR SDRAM - 64M x 16

#### 1Gb DDR2 SDRAM - 64M x 16

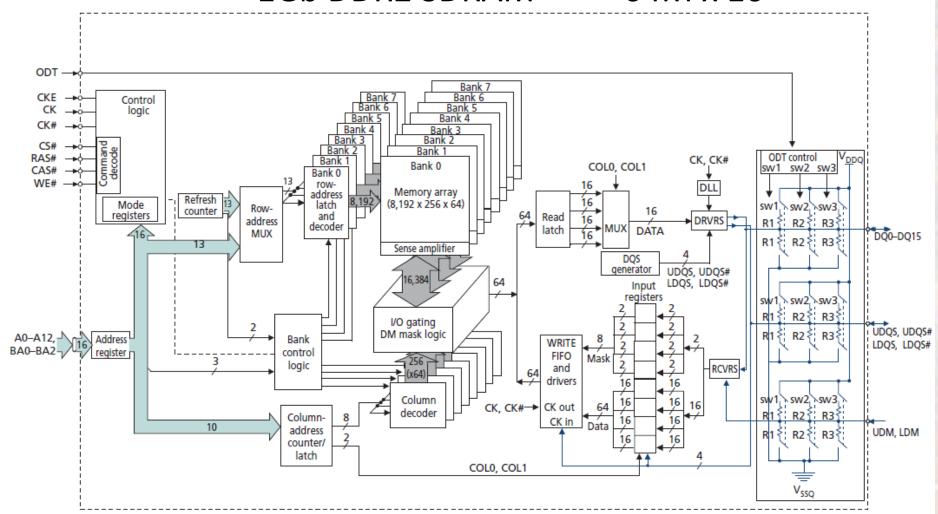

#### 1Gb DDR3 SDRAM - 64M x 16