# Last updated 1/22/21

- Encoding

- Comparison considerations

- Memory elements (bits)  $\rightarrow$  area or fit

- Coding / Decoding logic  $\rightarrow$  area or fit

- Speed

- Shorter logic chains → faster maximum clock speeds

- Power

- P = v \* i

- P = v \* c \* dv/dt

- dv/dt represents a transition 0 → 1

- Fewer transitions → lower power

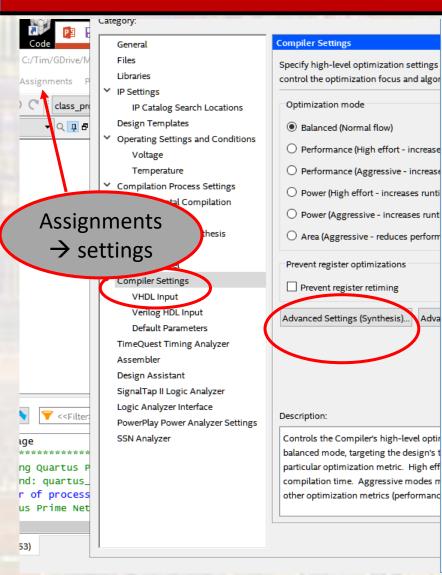

#### Encoding – Quartus options

| Auto         | Allows the Compiler to choose the best encoding for the state machine.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Gray         | Uses the minimal number of bits to encode the state machine, ceiling of 2 to the log of $n$ states. This setting is difference from the <b>Minimal Bits</b> setting because each state has only one bit difference from its neighboring states.                                                                                                                                                                                                                  |  |  |  |  |

| Johnson      | The number of bits used to encode the state machine is the ceilling of half of the states. Each state has only one bit difference from its neighboring states. Each state is generated by shifting the previous state's bits to the right by 1. The MSB of each state is the negation of the LSB of the previous state.                                                                                                                                          |  |  |  |  |

| Minimal Bits | <b>Bits</b> Uses the minimal number of bits to encode the state machine.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| One-Hot      | Encodes the state machine in the one-hot style. For one-hot encoding, the                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|              | Quartus II software does not guarantee that each state has one bit set to one<br>and all other bits to zero. Instead, the Quartus II software makes sure that the<br>reset state is all-zeroes. All other states have two bits set to one and all others<br>to zero. This is done so the state machine powers up in the reset state. This<br>encoding has the same properties as true one-hot encoding: each state can be<br>recognized by the value of one bit. |  |  |  |  |

| Sequential   | Quartus II software does not guarantee that each state has one bit set to one<br>and all other bits to zero. Instead, the Quartus II software makes sure that the<br>reset state is all-zeroes. All other states have two bits set to one and all others<br>to zero. This is done so the state machine powers up in the reset state. This<br>encoding has the same properties as true one-hot encoding: each state can be                                        |  |  |  |  |

|                                         | Settings - class_proj                                         |                                                                                                                                                                         | _       |                                                                                                                                                                                             |                         | × 100   |                    | - 22    |

|-----------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------|--------------------|---------|

|                                         |                                                               |                                                                                                                                                                         | 1       | Advanced Analysis & Synthesis Settings                                                                                                                                                      |                         |         |                    | ×       |

| - C:/Tim/GDrive/M<br>Assignments Pr     | C:/Tim/GDrive/M<br>ssignments Pi<br>General Compiler Settings |                                                                                                                                                                         |         | Specify the settings for the logic options in your project. Assignments made to an individual node or entity in the Assignment Editor will override the option settings in this dialog box. |                         |         |                    |         |

| Class_pro                               | Files<br>Libraries<br>✓ IP Settings                           | Specify high-level optimization settings control the optimization focus and algor                                                                                       |         | < <filter>&gt;</filter>                                                                                                                                                                     | 1                       | Sh      | ow: All            | •       |

|                                         | IP Catalog Search Locations                                   | Optimization mode                                                                                                                                                       |         | Name:                                                                                                                                                                                       |                         | Setting | <b>;</b> :         | ^       |

|                                         | Design Templates<br>Y Operating Settings and Conditions       | Balanced (Normal flow)                                                                                                                                                  |         | Pre-Mapping Resynthesis Optimization Remove Duplicate Registers                                                                                                                             | Off<br>On               |         |                    |         |

|                                         |                                                               | <ul> <li>Performance (High effort - increase</li> </ul>                                                                                                                 | e       | Remove Redundant Logic Cells                                                                                                                                                                | Off                     |         |                    |         |

| Assignments Settings                    |                                                               | O Performance (Aggressive - increase                                                                                                                                    |         | Report Connectivity Checks                                                                                                                                                                  | On                      |         |                    |         |

|                                         |                                                               | O Power (High effort - increases runti                                                                                                                                  | ti      | Report Parameter Settings                                                                                                                                                                   | On                      |         |                    |         |

| $\rightarrow$ set                       | ttings pilation                                               | O Power (Aggressive - increases runt                                                                                                                                    | t       | Report Source Assignments                                                                                                                                                                   | On                      |         |                    |         |

| s c c c c c c c c c c c c c c c c c c c |                                                               | • Area (Aggressive - reduces perform                                                                                                                                    | ~ I     | Resource Aware Inference For Block RAM                                                                                                                                                      | On                      |         |                    |         |

|                                         | Simulation                                                    |                                                                                                                                                                         | _       | Restructure Multiplexers                                                                                                                                                                    | Auto                    |         |                    |         |

| ▼ ≡ ₽ 5                                 | Roard Level                                                   | Prevent register optimizations                                                                                                                                          |         | SDC constraint protection                                                                                                                                                                   | Off                     |         |                    |         |

| Task                                    | Compiler Settings                                             | revent register retiming                                                                                                                                                |         | Safe State Machine                                                                                                                                                                          | Off                     |         |                    |         |

| Task                                    | VHDL Input                                                    |                                                                                                                                                                         |         | Shirt Register Replacement Allow Asynchronous Clear Signal<br>State Machine Processing                                                                                                      | One-Hot                 |         |                    | <b></b> |

| ·                                       | Verilog HDL Input<br>Default Parameters                       | Advanced Settings (Synthesis) Adva                                                                                                                                      | a N     | State PAM Replacement                                                                                                                                                                       | Auto                    |         |                    |         |

| Synthesis                               | TimeQuest Timing Analyzer                                     |                                                                                                                                                                         |         | Synchronization Register Chain Length                                                                                                                                                       | Gray                    |         |                    |         |

| & Route)                                | Assembler                                                     |                                                                                                                                                                         |         | Synthesis Effort                                                                                                                                                                            | Johnson                 |         |                    |         |

| (Generate programn                      | Design Assistant                                              |                                                                                                                                                                         |         | Timing-Driven Synthesis                                                                                                                                                                     | Minimal Bits<br>One-Hot | 5       |                    |         |

|                                         | SignalTap II Logic Analyzer                                   |                                                                                                                                                                         |         | Use LogicLock Constraints during Resource Balancing                                                                                                                                         | Sequential              |         |                    | ~       |

| Filter>                                 | Logic Analyzer Interface<br>PowerPlay Power Analyzer Settings | Description:                                                                                                                                                            |         | Description:                                                                                                                                                                                | User-Encod              | ed      |                    |         |

| ;age SSN Analyzer<br>tus Prime Net      |                                                               | Controls the Compiler's high-level optir<br>balanced mode, targeting the design's t<br>particular optimization metric. High eff<br>compilation time. Aggressive modes n |         | style, or select 'One-Hot', 'Minimal Bits', 'Gray', 'Johnson', 'Sequential' or 'Auto' (Compiler-selected)<br>encoding.                                                                      |                         |         | Reset<br>Reset All |         |

| ıg (143)                                |                                                               | other optimization metrics (performanc                                                                                                                                  | د (<br> |                                                                                                                                                                                             |                         |         | '                  |         |

| SLIDE 2                                 |                                                               |                                                                                                                                                                         |         |                                                                                                                                                                                             | ·                       | ОК      | Cancel             | Help    |

CE 1911

Specify the settings for the logic options in your project. Assignments made to an individual node or entity in the Assignment Editor will override the option settings in this dialog box. <<Filter>>

Advanced Analysis & Synthesis Settings

|                                                 | Show. Ma |   |

|-------------------------------------------------|----------|---|

| Name:                                           | Setting: | ^ |

| Allow Any RAM Size For Recognition              | Off      |   |

| Allow Any ROM Size For Recognition              | Off      |   |

| Allow Any Shift Register Size For Recognition   | Off      |   |

| Allow Register Duplication                      | On       | • |

| Allow Register Merging                          | On       |   |

| Allow Shift Register Merging across Hierarchies | Auto     |   |

| Allow Synchronous Control Signals               | On       |   |

| Analysis & Synthesis Message Level              | Medium   |   |

| Auto Carry Chains                               | On       |   |

| Auto Clock Enable Replacement                   | On       |   |

| Auto DSP Block Replacement                      | On       |   |

| Auto Gated Clock Conversion                     | Off      |   |

| Auto Open-Drain Pins                            | On       |   |

| Auto RAM Replacement                            | On       |   |

| Auto ROM Replacement                            | On       |   |

| Auto Resource Sharing                           | Off      |   |

| Auto Shift Register Replacement                 | Auto     | ~ |

Description:

Adva

Controls whether the Compiler is allowed to duplicate registers to improve design performance. When register duplication is allowed, the Compiler may perform optimizations that create a second copy of a register and move a portion of its fan-out to this new node, in order to improve routability and/or reduce the total routing wire required to route a net with many fan-outs.

Reset All

Help

ΟК

Cancel

Show: All

- Encoding

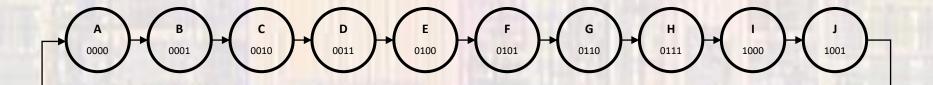

- Comparison Mod 10 counter

- Encoding

- Comparison Mod 10 counter

10 values (states) to encode

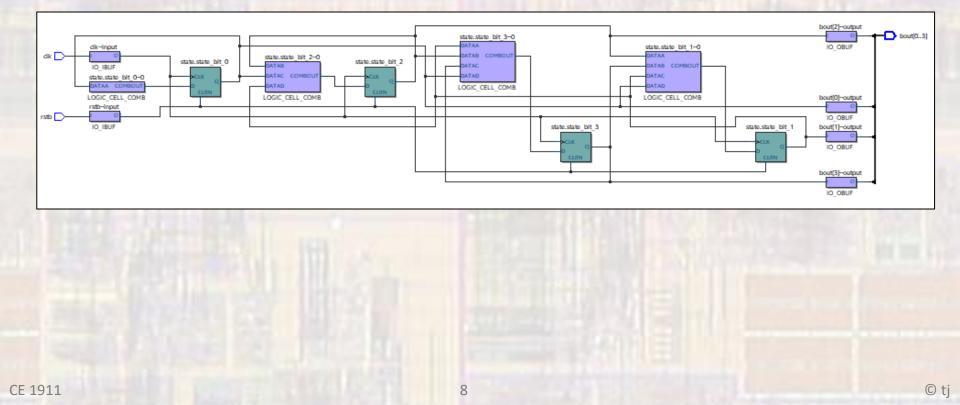

- Binary (sequential)

0000, 0001, 0010, 0011, 0100, 0101, 0110, 0111, 1000, 1001

- 4 registers

- complex decoding

- slower

- bigger

- multiple bit transitions

© tj

Encoding – Mod 10 counter

Total logic elements Total registers

- Encoding

- Comparison Mod 10 counter

10 values to encode

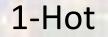

• One hot (cold)

- 10 registers

- trivial decoding

- faster

- small

- dual bit transitions

Encoding – Mod 10 counter

Total logic elements Total registers

- Encoding

- Comparison Mod 10 counter

10 values to encode

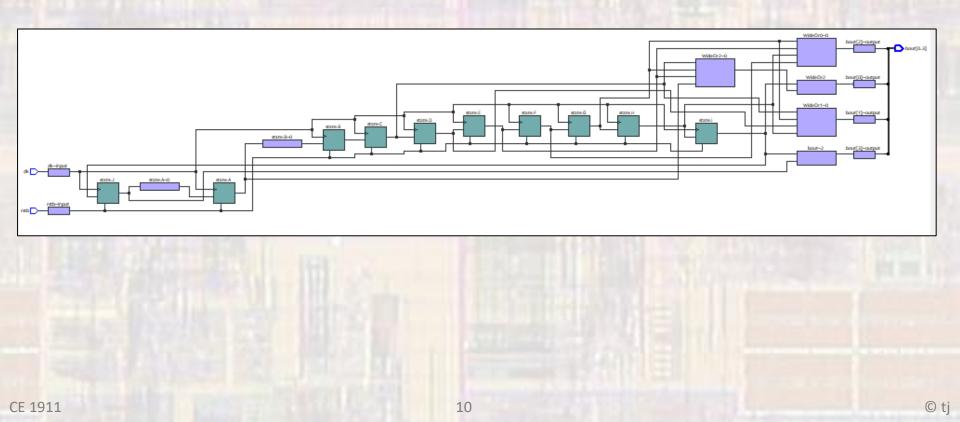

• Gray

0000, 0001, 0011, 0010, 0110, 0111, 0101, 0100, 1100, 1101

- 4 registers

- complex decoding

- slower

- larger

- single bit transitions

Encoding – Mod 10 counter

Gray

Total logic elements Total registers

- Encoding

- Comparison Mod 10 counter

10 values to encode

Johnson

00000, 1000<mark>0</mark>, 11000, 11100, 11110, 11111, 01111, 00111, 00011, 00001

- 5 registers

- complex decoding

- slower

- bigger

- single bit transitions

Encoding – Mod 10 counter

Johnson

Total logic elements Total registers