## **CE3101 Lab 3: Rectifier Circuits**

## Objectives

- Explore rectifier circuits

- Design practice

|                          | ckout an Analog Discovery 2 kit from the Tech Center<br>ckout needed components from the Tech Center                                                                                                                                                                                                                                                           | student<br>check off |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Assignment               |                                                                                                                                                                                                                                                                                                                                                                |                      |

| Part 1:                  | Use a 1N4148 diode to create a half wave rectifier with a $1K\Omega$ load Simulate your design using a $0$ - $3V$ 60Hz sine wave (replacing the transformer) Setup the AD2 to generate a $0$ - $3V$ 60Hz sine wave (replacing the transformer) Build your design and measure the input voltage, the rectified voltage, and the Estimate the diode "on" voltage | ripple               |

|                          | Compare the simulation to the actual circuit                                                                                                                                                                                                                                                                                                                   |                      |

| Part 2:                  | Add a filter capacitor to the design from Part 1. Target less than, but close to 5% Note: our class eqns do not cover this design - you will need to make a modi Simulate with your calculated capacitor Simulate with the best "common component" capacitor available Build your design and measure the input voltage and the rectified voltage               |                      |

| Part 3:                  | Design a bridge rectifier circuit with <5% ripple using two 0 - 5V 60Hz sine wave                                                                                                                                                                                                                                                                              | s (+/-               |

|                          | 10v pk-pk) (replacing the transformer) and a $2K\Omega$ load. Simulate, build, and test We need 2 signal generators because the AD2 signals are referenced to gnd                                                                                                                                                                                              | -                    |

| Check Off                |                                                                                                                                                                                                                                                                                                                                                                |                      |

| Demo and document part 1 |                                                                                                                                                                                                                                                                                                                                                                | 20%                  |

| Demo and document part 2 |                                                                                                                                                                                                                                                                                                                                                                | 30%                  |

| Demo and document part 3 |                                                                                                                                                                                                                                                                                                                                                                | 50%                  |

Demo (in-person or via Teams chat) and Report (in the box) due by 4:00 pm Wednesday of the week following the lab.

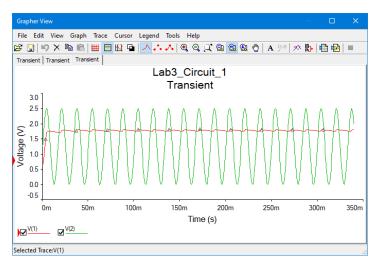

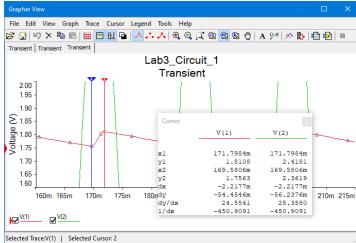

## Example Part 2 Simulation Results (different voltage, common cap)

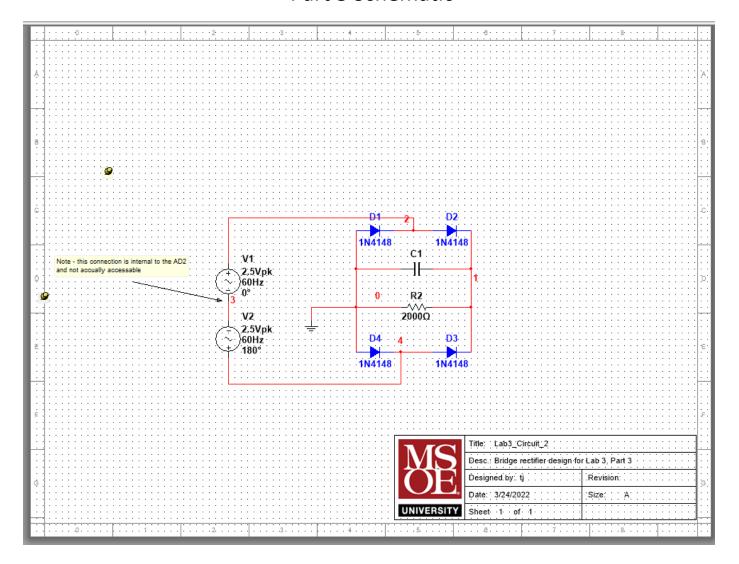

## Part 3 Schematic