# Metal Oxide Semiconductor Enhancement Mode Transistor

Last updated 3/24/22

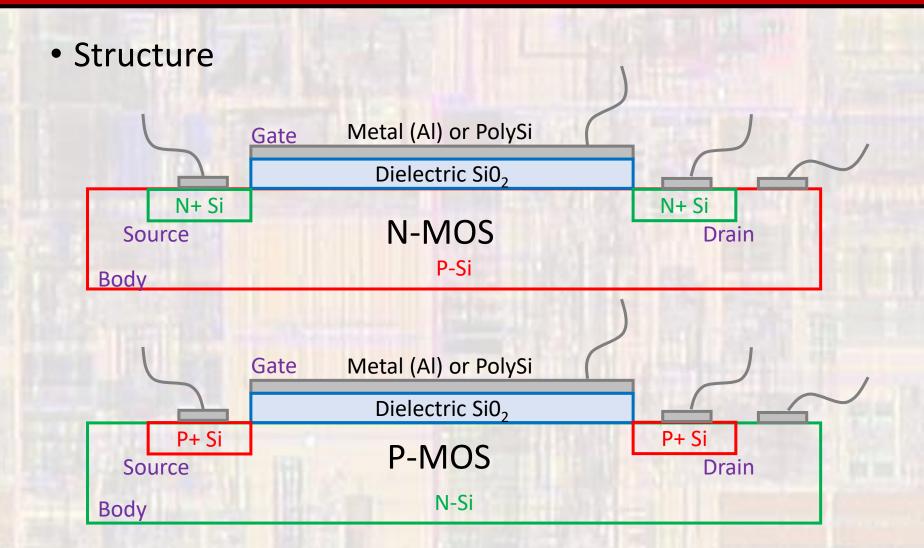

Structure

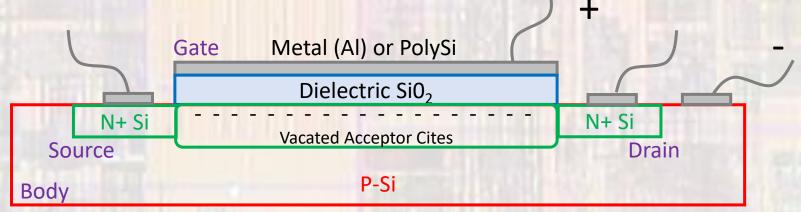

- N-MOS Operation

- Large Positive Bias

- Depletion region is formed

- Mobile holes pushed away (region is depleted of holes)

- Net negative (fixed) charge left behind

- Electrons are drawn from the Si to form an inversion layer

A channel is formed from Source to Drain Electrons can flow through this channel

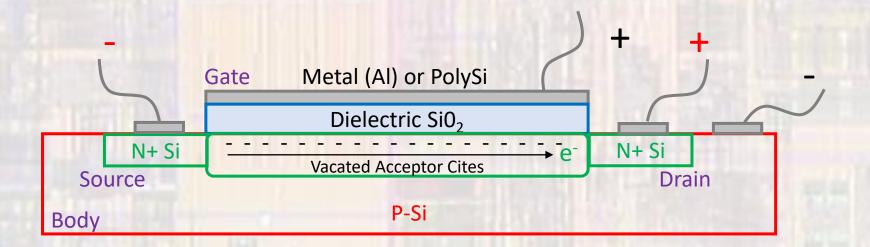

- N-MOS Operation

- Large Positive Bias + Positive Bias from Drain to Source

- Electrons move from Source to Drain

- Current flows from Drain to Source

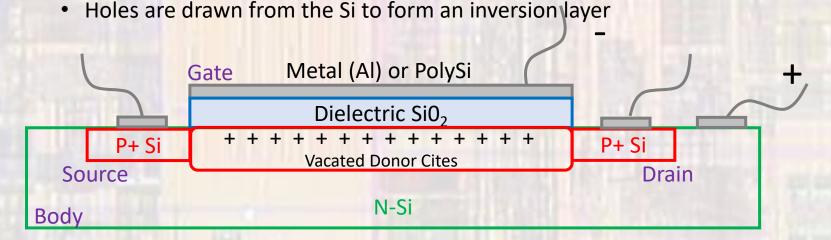

## P-MOS Operation

- Large Negative Bias

- Depletion region is formed

- Mobile electrons pushed away (region is depleted of electrons)

- Net positive (fixed) charge left behind

A channel is formed from Source to Drain Holes can flow through this channel

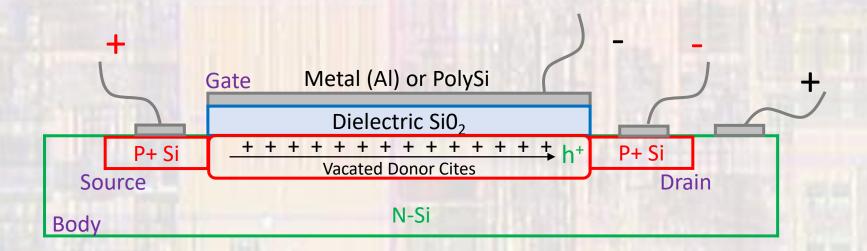

- P-MOS Operation

- Large Negative Bias + Positive Bias from Source to Drain

- Holes move from Source to Drain

- Current flows from Source to Drain

- Enhancement Mode

- A bias is required to form the channel

- 4-terminal symbol

- In digital applications the Source is typically tied to

- Vdd for P-MOS

- Gnd for N-MOS

The simplified logic symbols

Note – almost all N-MOS and P-MOS devices used today are enhancement mode – so the dashed line is omitted

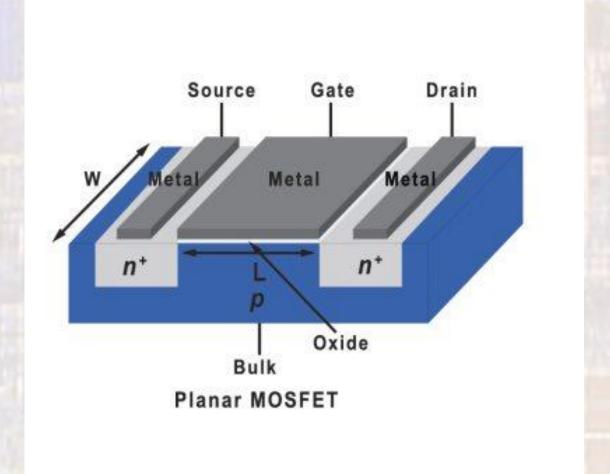

### Parameters

- W width of the transistor

- L length of the transistor (S to D)

- V<sub>th</sub> threshold voltage (inversion layer formed)

- Kn, Kp conduction parameter

$$K_n = \frac{W\mu_n C_{ox}}{2L} \qquad K_p = \frac{W\mu_p C_{ox}}{2L}$$

$$K_n = \frac{k'_n}{2} \frac{W}{L}$$

$$K_p = \frac{k'_p}{2} \frac{W}{L}$$

$$k'_n = \mu_n C_{ox}$$

$$k'_p = \mu_p C_{ox}$$

$\mu_n$ ,  $\mu_n$ ,  $C_{ox}$  fixed for a given semiconductor process