#### Last updated 10/24/24

These slides introduce the basics of a CMOS timing

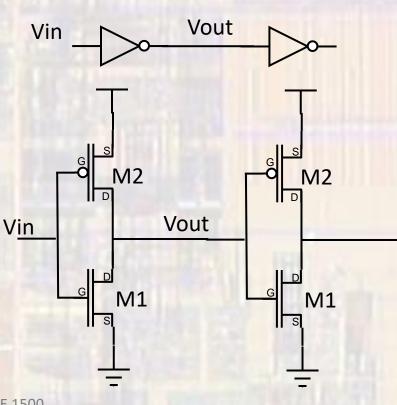

- CMOS Transistor Model

- Our simplified model of CMOS devices:

- Transistor D-S path looks like a resistor

- High valued when off

- Low valued when on

- Transistor G looks like a capacitor tied to gnd

- The D-S resistance can be reduced (increased) by making larger (smaller) devices

- The G capacitance increases (decreases) for larger(smaller) devices

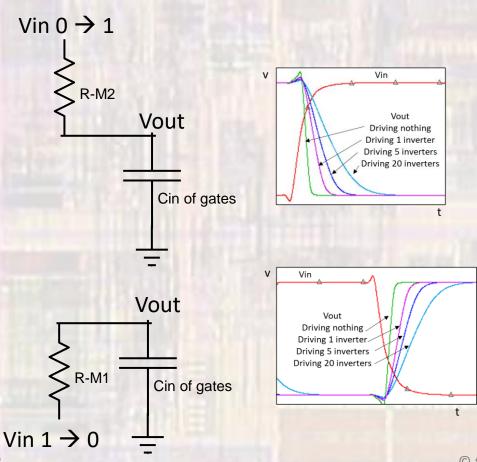

- CMOS Circuit Model

- The output of one gate is connected to (drives) one or more gate inputs (Gs)

- This forms an RC circuit

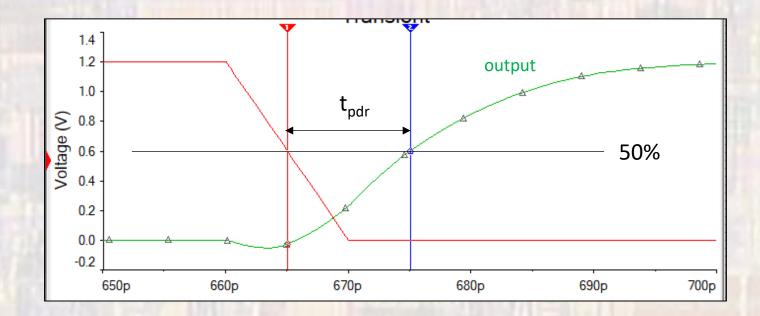

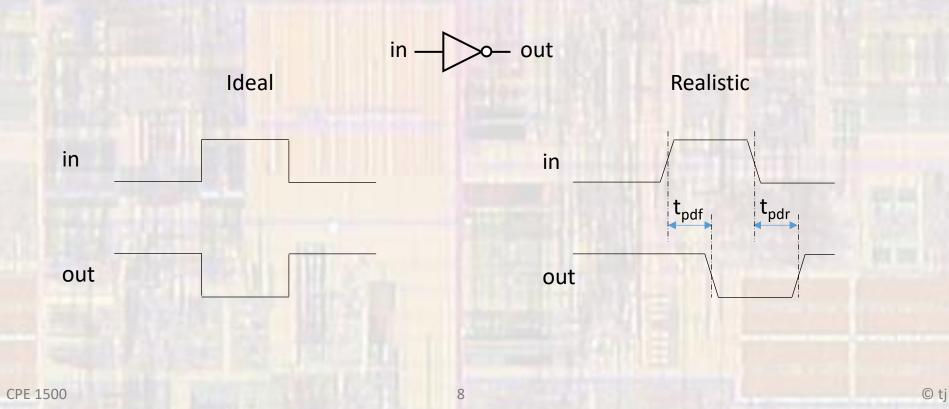

- Propagation Delay Rising t<sub>pdr</sub> t<sub>pdh</sub>

- t<sub>pdr</sub> Time for Propagation Delay with the output Rising

- Measured from 50% of input "high" value to 50% of output "high" value on an output rising edge

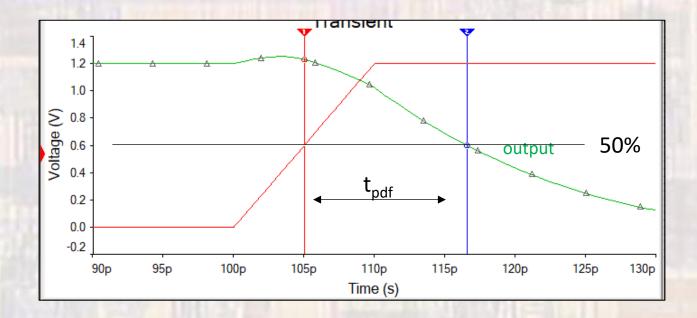

- Propagation Delay Falling t<sub>pdf</sub> t<sub>pdf</sub>

- t<sub>pdf</sub> Time for Propagation Delay with the output Falling

- Measured from 50% of input "high" value to 50% of output "high" value on an output falling edge

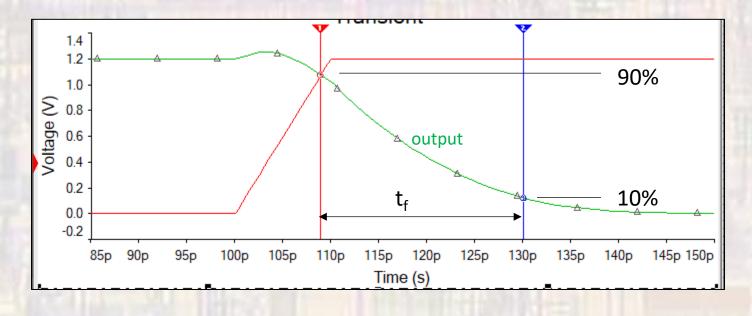

- Fall Time t<sub>fall</sub> (t<sub>f</sub>)

- t<sub>f</sub>

- Measured from 90% of "high" value to 10% of "high" value on the output

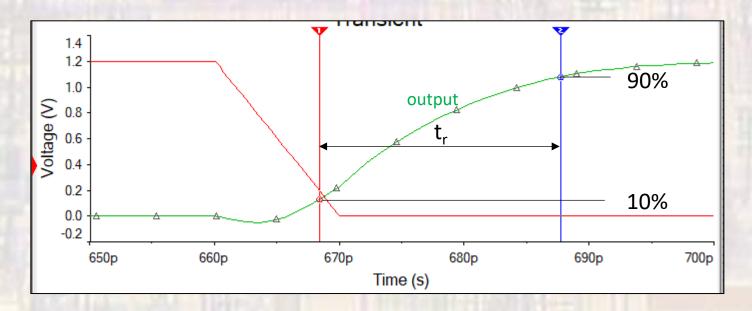

- Rise Time t<sub>rise</sub> (t<sub>r</sub>)

- t<sub>r</sub> is measured on the output

- Measured from 10% of "high" value to 90% of "high" value on the output

- Timing Diagrams

- Propagation Delay

- Maximum time from when the input changes (50%) to the time when the output reaches its final value (50%)

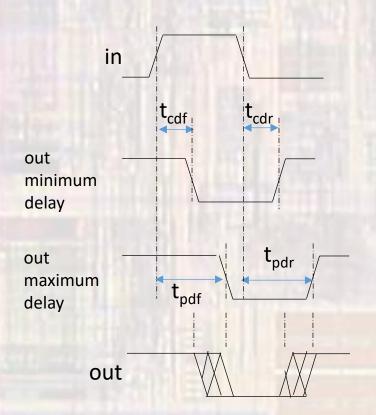

- Timing Diagrams

- Contamination Delay

- Minimum time from when the input changes (50%) to the time when the output reaches its final value (50%)

9

t<sub>cd</sub>

- Delay times change due to:

- Circuit parameters

- Temperature

- Part to part variations

out