## Digital Logic Timing Glitches

Last updated 10/24/24

These slides introduce the basics of a digital logic timing glitches

## Digital Logic Timing Glitches

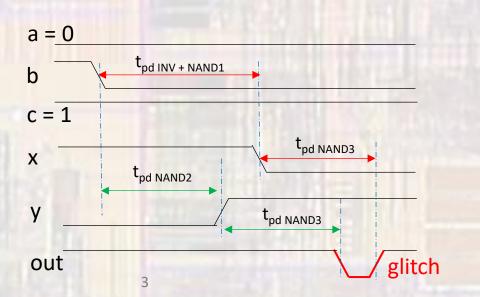

- Digital Logic Timing Glitch

- A temporary output transition that occurs before the final output value is reached

- Created when multiple paths lead from 1 input to the output and

- One implicant in the truth table turns off before another turns on

- A problem when:

- We are using the output signal as an edge triggered input

- More on this later in the class

- When we look at the result prior to its final value

## Digital Logic Timing Glitches

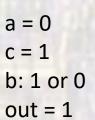

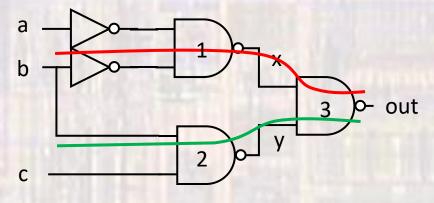

Example 1 – input transition that should not cause an output change

| а | b | С | оит |    |

|---|---|---|-----|----|

| 0 | 0 | 0 | 1   | ħ. |

| 0 | 0 | 1 | 1   | ×  |

| 0 | 1 | 0 | 0   |    |

| 0 | 1 | 1 | 1   |    |

| 1 | 0 | 0 | 0   |    |

| 1 | 0 | 1 | 0   |    |

| 1 | 1 | 0 | 0   |    |

| 1 | 1 | 1 | 1   |    |

## Digital Logic Timing Glitches

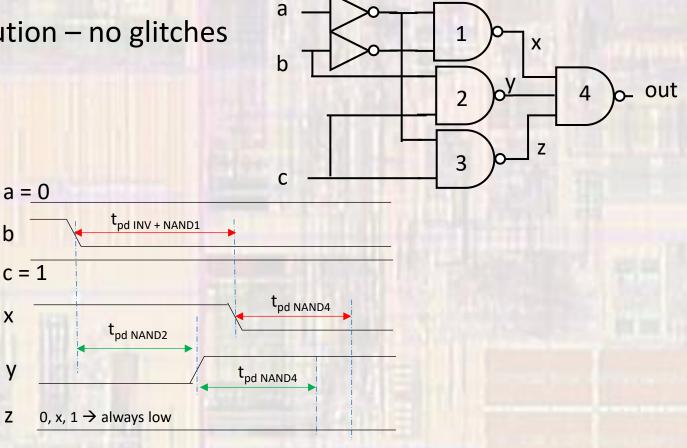

Example 2 – glitch free solution

• Use the consensus theorem to ensure no glitches (more

later)

Bigger solution – no glitches