## Last updated 12/18/24

- Simulation using the University Waveform tool

- 1. Create the HDL file(s)

- 2. Run Analysis and Elaboration in Quartus

- 3. Verify the RTL is what is expected

- 4. Open a new University Program VWF file

- 5. Select the desired signals to drive / analyze

- 6. Setup the input signal waveforms

- 7. Setup simulator options

- 8. Run the simulation

- 9. Evaluate the results

© ti

#### 1) Create the HDL file

mux\_4\_hdl.vhdl -- created 12/18/24 -- tj -- HDL version of a 4 to 1 mux -- inputs: a, b, c, d, sel0, sel1 -- outputs: mux\_out library ieee; use ieee.std\_logic\_1164.all; entity mux\_4\_hdl is port ( i\_a : in std\_logic; i\_b : in std\_logic; i\_c : in std\_logic; in std\_logic; i\_d : in std\_logic\_vector(1 downto 0); i\_sel : out std\_logic o\_mux\_out : ); end entity; architecture behavioral of mux\_4\_hdl is internal signals - just for clarity signal a\_int: std\_logic; signal b\_int: std\_logic; signal c\_int: std\_logic; signal d\_int: std\_logic; begin o\_mux\_out <= a\_int or b\_int or c\_int or d\_int;</pre> end architecture;

- 2) Run Analysis and Synthesis in Quartus Creates a gate level implementation of the HDL

- Set the top-level block

- Rt-click on your top level block

- Select Set as Top-level Entity

| File Edit View Pro | ject Assignments Pr                                 | ocessing Tools             | Window Help       |      |

|--------------------|-----------------------------------------------------|----------------------------|-------------------|------|

|                    |                                                     |                            | capture 💌         | _    |

| Project Navigator  | Files                                               | <ul> <li>Q II 5</li> </ul> | 1 x 👇             |      |

| Files              |                                                     |                            | Table of Contents |      |

|                    | Open<br>Remove File from Proje                      | ct                         |                   | loba |

|                    | Set as Top-Level Entity                             |                            | Ctrl+Shift+V      |      |

|                    | Create AHDL Include Fil                             | es for Current File        |                   |      |

|                    | Create Symbol Files for<br>Create Verilog Instantia |                            |                   | on   |

|                    | Create VHDL Compone                                 |                            | for Current File  | essa |

|                    | Properties                                          |                            |                   |      |

|                    |                                                     |                            |                   |      |

| Tasks              | Compilation                                         | - ■ ₽ 5                    | 1 x               |      |

#### 2) Run Analysis and Synthesis in Quartus

- Processing → Start → Start Analysis and Synthesis

- Check the Device

- Check the Top-level Entity Name

21057 Implemented 9 device resources after synthesis - the final resource count might be different Quartus Prime Analysis & Synthesis was successful. 0 errors, 2 warnings

| Flow Summary                       |                                             |

|------------------------------------|---------------------------------------------|

| < <filter>&gt;</filter>            |                                             |

| Flow Status                        | Successful - Wed Dec 18 14:15:35 2024       |

| Quartus Prime Version              | 18.1.0 Build 625 09/12/2018 SJ Lite Edition |

| Revision Name                      | hat_capture                                 |

| Top-level Entity Name              | mux_4_hdl                                   |

| Family                             | MAX 10                                      |

| Device                             | 10M50DAF484C7G                              |

| Timing Models                      | Finat                                       |

| Total logic elements               | 2                                           |

| Total registers                    | 0                                           |

| Total pins                         | 7                                           |

| Total virtual pins                 | 0                                           |

| Total memory bits                  | 0                                           |

| Embedded Multiplier 9-bit elements | 0                                           |

| Total PLLs                         | 0                                           |

| UFM blocks                         | 0                                           |

| ADC blocks                         | 0                                           |

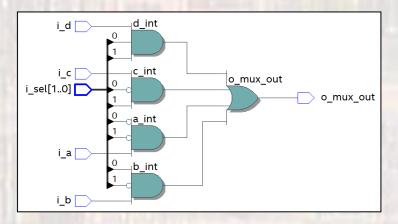

### 3) Verify the RTL (schematic of the implementation)

- Tools → Netlist Viewers → RTL Viewer

- Evaluate the schematic does it make sense?

| Processing | Тос  | ls Window Help                      |                                      |               |  |  |  |  |  |

|------------|------|-------------------------------------|--------------------------------------|---------------|--|--|--|--|--|

| って         | ŝ.   | Run Simulation Tool                 | * 🍯 🚭 🚳 💷 Þ 🍝 🍝                      | $\rightarrow$ |  |  |  |  |  |

| -          | ₹\$. | Launch Design Space Explorer II     | ompilation Report - hdl_capture      |               |  |  |  |  |  |

|            | 9    | Timing Analyzer                     | Flow Summary                         |               |  |  |  |  |  |

|            |      | Advisors                            | Flow Status Successful               | - Wed         |  |  |  |  |  |

|            | 4    | Chip Planner                        | Quartus Prime Version 18.1.0 Buile   | d 625 (       |  |  |  |  |  |

|            | 4    | Design Partition Planner            | Revision Name hdl_capture            | e             |  |  |  |  |  |

|            | <    | Netlist Viewers                     | RTL Viewer                           |               |  |  |  |  |  |

|            | mp   | Signal Tap Logic Analyzer           | Technology Map Viewer (Post-Mapping) | 484C7         |  |  |  |  |  |

|            | -    | In-System Memory Content Editor     | Technology Map Viewer (Post-Fitting) |               |  |  |  |  |  |

|            |      | Logic Analyzer Interface Editor     | State Machine Viewer                 | artition      |  |  |  |  |  |

|            | 01   | In-System Sources and Probes Editor | Total registers N/A until P          | artition      |  |  |  |  |  |

|            |      | Cignal Droke Dine                   | Total pins N/A until P               | artition      |  |  |  |  |  |

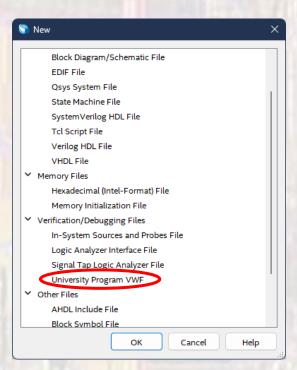

#### 4) Open a new University Program VWF file

File → New → University Program VWF

#### 4) Open a new University Program VWF file

- File → New → University Program VWF

- Save the file: File  $\rightarrow$  Save As

- Give is a useful file name (mux\_4\_hdl\_sim1.vwf)

| 8            | Simulation Wav                                                           | eform Editor - (   | C:/Users/j   | johnsontimo    | oj/Quartus_F                                                                  | Projects_CPE | 1500/HDL_ | Capture/hdl_ | capture - ho | dl_capture - | [mux_4_hdl | _sim1vwf.vw | fJ       |               |          | ×  |

|--------------|--------------------------------------------------------------------------|--------------------|--------------|----------------|-------------------------------------------------------------------------------|--------------|-----------|--------------|--------------|--------------|------------|-------------|----------|---------------|----------|----|

| <u>F</u> ile | <u>E</u> dit <u>V</u> iew                                                | <u>S</u> imulation | <u>H</u> elp |                |                                                                               |              |           |              |              |              |            |             | 9        | Search altera | .com     | •  |

|              | e 🔍 💥 🕑                                                                  | ,h <u>z</u> ∖ī ∖   | Ξ₩X X        | <u>c</u> X8 X2 | $\langle \mathbf{B} \mid \mathbb{R}^{\mathbb{P}}_{n} \mid \mathbb{R}^{1}_{n}$ | 2 🍋 📠        | <b>咒</b>  |              |              |              |            |             |          |               |          |    |

| Mas          | Master Time Bar: 0 ps Pointer: 356.56 ns Interval: 356.56 ns Start: End: |                    |              |                |                                                                               |              |           |              |              |              |            |             |          |               |          |    |

|              | Name                                                                     | Value at           | 0 ps         | 80.0 ns        | 160.0 ns                                                                      | 240.0 ns     | 320,0 ns  | 400,0 ns     | 480.0 ns     | 560,0 ns     | 640,0 ns   | 720,0 ns    | 800,0 ns | 880,0 ns      | 960,0 ns |    |

|              | Name                                                                     | 0 ps               | 0 ps         |                |                                                                               |              |           |              |              |              |            |             |          |               |          |    |

| •            |                                                                          |                    |              |                |                                                                               |              |           |              |              |              |            |             |          |               |          |    |

|              |                                                                          |                    |              |                |                                                                               |              |           |              |              |              |            |             |          | 0%            | 00:00:0  | 00 |

#### 5) Select the desired signals to drive / analyze

- Edit  $\rightarrow$  Insert Node or Bus

- Node Finder...

- List

At this point we will only see the pins

| Inper Input   adue type: 9-Level   Binary Node Finder     Index Finder     Input     Input |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| width: 1   1   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0   0                                                                                                                                                                                                       |

#### 5) Select the desired signals to drive / analyze

- Use the arrows to move nodes form the Found list to the Selected list

- OK, OK

| 🕤 Node Finder                                                                                                                                                                                                                      |                   | ×                                                                                                                                                                                                                                                                    | 🕥 Node Finder                                                                                             | Х                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Named: * I                                                                                                                                                                                                                         | Filter: Pins: all | ▼ OK<br>List Cancel                                                                                                                                                                                                                                                  | Named: * Filter: Pin                                                                                      | ns: all OK                                                                                                                                                                                                           |

| Nodes Found:                                                                                                                                                                                                                       | Selected Nodes:   |                                                                                                                                                                                                                                                                      |                                                                                                           | Selected Nodes:                                                                                                                                                                                                      |

| Name     Type       in- i_a     Input       in- i_b     Input       in- i_c     Input       in- i_d     Input       in- i_sel     Input Group       in- i_sel[0]     Input       in- i_sel[1]     Input       o_mux_out     Output | Name              | Type         Insert Node or Bus         Name:       **Multiple Items*         Type:       **Multiple Items*         Value type:       9-Level         Radix:       Binary         Bus width:       1         Start index:       0         Display gray code count as | in_ i_b Input<br>in_ i_c Input<br>in_ i_d Input<br>input Group<br>Input<br>Input<br>Cancel<br>Node Finder | Name     Type       in_ia     Input       in_ib     Input       in_ic     Input       in_id     Input       in_isel     Input Group       in_isel[0]     Input       in_isel[1]     Input       o_mux_out     Output |

#### 6) Setup the input signal waveforms

- You must have a plan

- What signals to switch at what time

- How long does the total test take

- Edit  $\rightarrow$  Set Grid Size (10 ns)

- Edit → Set End Time (640 ns)

| 🕤 Sir | mulation Wa               | veform Editor - ( | C:/Users/joh | nsontimoj/Quar | tus_Projects_CPE | 1500/HDL_Captu | re/hdl_capture - h | dl_capture - [mux | _4_hdl_sim1vw | f.v —         |            |

|-------|---------------------------|-------------------|--------------|----------------|------------------|----------------|--------------------|-------------------|---------------|---------------|------------|

| Eile  | <u>E</u> dit <u>V</u> iew | Simulation        | <u>H</u> elp |                |                  |                |                    |                   |               | Search altera | .com       |

|       | 🔍 👗 එ                     | ተ 🚣 🗡፤ 👌          | H WX XC      | X X2 XB 🛛 💐    | ີ 💐 🚈 📠          |                |                    |                   |               |               |            |

| Maste | r Time Bar:               | 0 ps              | •            | Pointer:       | 3.59 ns          | Interval:      | 3.59 ns            | Start: 0 ps       |               | Enc: 640.0    | 15         |

|       | Name                      | Value at          | 0 ps         | 80.0 ns        | 160.0 ns         | 240.0 ns       | 320,0 ns           | 400.0 ns          | 480.0 ns      | 560,0 ns      | 640.0 ns 🏾 |

|       | Name                      | 0 ps              | 0 ps         |                |                  |                |                    |                   |               |               |            |

| in    | i_a                       | во                |              |                |                  | 10 nc          |                    |                   |               |               |            |

| n     | i_b                       | во                |              |                |                  | TO US          |                    |                   |               |               |            |

| n     | i_c                       | во                |              |                |                  |                |                    |                   |               |               |            |

| n     | i d                       | во                | -            |                |                  |                |                    |                   |               |               |            |

|       | > i sel                   | B 00              |              |                |                  |                | 00                 |                   |               |               |            |

| out   | o_mux                     | вх                |              | ******         | ******           | ******         | *******            | ******            | ******        | ******        |            |

|       |                           |                   |              |                |                  |                |                    |                   |               |               |            |

| •     |                           | 1                 | • [          |                |                  |                |                    |                   |               |               | <b>v</b>   |

|       |                           |                   |              |                |                  |                |                    |                   |               | 0%            | 00:00:00   |

#### 6) Setup the input signal waveforms

- See the University Waveform Viewer Input Setup Slides (lab 2)

- File  $\rightarrow$  Save

| 8            | Simulation Wav            | eform Editor - C:                                            | /Users/johnsontimoj/Quartus_Projects_CPE1500/HDL_Capture/hdl_capture - hdl_capture - [mux_4_hdl_sim1vwf. | v —            | o x        |

|--------------|---------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------|------------|

| <u>F</u> ile | <u>E</u> dit <u>V</u> iew | <u>S</u> imulation <u>I</u>                                  | ielp                                                                                                     | Search altera. | :om 🌖      |

|              | 2 🐹 🕹                     | $\mathbb{A} \cong \mathbb{X}_{\mathbb{E}} \times \mathbb{E}$ | 🔛 XC XZ XE 😪 🦓 🚈 🔜 账                                                                                     |                |            |

| Mas          | ter Time Bar:             | ) ps                                                         | Pointer: 3.59 ns Interval: 3.59 ns Start: 0 ps                                                           | End: 0 ps      |            |

|              | Name                      | Value at<br>0 ps                                             | 0 ps 80.0 ns 160.0 ns 240.0 ns 320.0 ns 400.0 ns 480.0 ns<br>0 ps                                        | 560.0 ns       | 640.0 ns 🏛 |

| 5            | ✓ data_in                 | B 0000                                                       | \$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$                             | ~~~~~          |            |

| in_          | i_a                       | B 0                                                          |                                                                                                          |                |            |

| in_          | i_b                       | B 0                                                          |                                                                                                          |                |            |

| in_          | i_c                       | B 0                                                          |                                                                                                          |                |            |

| in<br>—      | i_d                       | BO                                                           |                                                                                                          |                |            |

| -            | ✓ i_sel                   | B 00                                                         | 00 X 01 X 10 X                                                                                           | 11             |            |

| in<br>—      | i_sel                     | B 0                                                          |                                                                                                          |                |            |

| in_          | i_sel                     | B 0                                                          |                                                                                                          |                |            |

| out          | o_mux                     | BX                                                           |                                                                                                          | ******         | XXXX       |

|              |                           | Þ                                                            |                                                                                                          |                |            |

|              |                           |                                                              |                                                                                                          | 0%             | 00:00:00   |

#### 7) Setup the simulator options

- Simulation → Simulation Settings

- Select VHDL

- Verify the vwf file name

- If incorrect Restore Defaults

- Save

| Caution: Improv                                                    | edy modifying these settings can cause the simulation to fail                   |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------|

| . Language: 🔿 Veril 😦 🗿 VH                                         | DL The language used for the testbench and netlist)                             |

| unctional Simulation Settings                                      | Timing Simulation Settings                                                      |

| estbench Generation Command                                        | (Functional Simulation):                                                        |

| juartus_edagen_testbencht                                          | tool=modelsim_oemformat=vhdlwrite_settings_files=off hdl_capture -c h           |

| etlist Generation Command (Fu                                      | nctional Simulation):                                                           |

| juartus_edawrite_settings_file                                     | es=offsimulationfunctional=onflatten_buses=offtool=modelsim_oen                 |

| IodelSim Script (Functional Sim                                    | ulation):                                                                       |

| onerror {exit -code 1}                                             |                                                                                 |

| /lib work                                                          |                                                                                 |

| com -work work hell_appare.vr                                      | IU                                                                              |

| /com -work work mux_4_hdl_si                                       | m1vwf.vwjvht                                                                    |

| /sim -novopt -c -t 1p L fiftyfiv                                   | enm + altera - L altera_mf - L 220model - L sgate - L altera_Insim work.mux_4_H |

| vcd file -direction hdl_capture.m                                  | /sim.vcd                                                                        |

| vcd add -internal mux_4_hdl_vh                                     | d_vec_tst/*                                                                     |

| vcd add -internal mux_4_hdl_vh                                     | d_vec_tst/i1/*                                                                  |

| proc simTimestamp {} {                                             |                                                                                 |

|                                                                    |                                                                                 |

| echo "Simulation time: \$::now                                     | ps"                                                                             |

| echo "Simulation time: \$::now<br>if { [string equal running [runS |                                                                                 |

|                                                                    |                                                                                 |

| if { [string equal running [runS                                   |                                                                                 |

| if { [string equal running [runS<br>after 2500 simTimestamp        |                                                                                 |

| if { [string equal running [runS<br>after 2500 simTimestamp<br>}   |                                                                                 |

| if { [string equal running [runS<br>after 2500 simTimestamp<br>}   |                                                                                 |

Restore Defau

#### 8) Run Simulation

• Simulation → Run Functional Simulation

| ی 🧊           | imulation Flow Progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ົ 🕤 ຣ        | Simulation Wav            | eform Editor -     | C:/Users/johnsontimoj/Quartus_Projects_CPE1500/HDL_Capture/hdl_capture - hdl_capt — 🛛 🗙 |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------|--------------------|-----------------------------------------------------------------------------------------|

|               | Generating netlist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <u>F</u> ile | <u>E</u> dit <u>V</u> iew | <u>S</u> imulation | Help Search altera.com                                                                  |

| writ          | e_settings_files=off lab1 -c lab1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              | 역 🐹 🕹                     | 片 프 Xī (           | /= 器 XC XE XE   唬 № №   🔜 账                                                             |

| v<br>te<br>vi | Run Log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Mast         | ter Time Bar:             | ) ps               | Pointer: 105.83 ns Interval: Simulation Plot                                            |

| lr<br>V       | (Will show any errors) which may                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              | Name                      | Value at<br>0 ps   | ops 160.0 ns (not the VWF window) ns (                                                  |

| f¢            | (Disappears if all ok)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -            | Ƴ data_in                 | B 0000             |                                                                                         |

| Со            | npleted successfully.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | in           | i_a                       | BO                 |                                                                                         |

|               | Generating the functional simulation netlist ****                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <u>in</u>    | i_b                       | B 0                |                                                                                         |

|               | rtus_edawrite_settings_files=offsimulationfunctional=onfl<br>l=modelsim_oemformat=vhdl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | in<br>in     | i_c<br>i_d                | в 0<br>в 0         |                                                                                         |

| out<br>lab    | output_directory="C:/Users/johnsontimoj/Quartus_Projects_CPE1500/L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              | ⊻ i_sel                   | B 00               |                                                                                         |

| tau           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | in           | i_sel                     | B 0                |                                                                                         |

| _             | stated as a line of the second s | <u>in</u>    | i_sel                     | во                 |                                                                                         |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | out          | o_mux                     | BO                 |                                                                                         |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •            |                           | Þ                  |                                                                                         |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                           |                    | ون. 00:00:00 %0                                                                         |

#### 9) Evaluate results

Compare simulation results with expected results

| <b>S</b> 5   | Simulation Wav            | eform Editor -     | C:/Users/johnsontimoj/Qua                    | rtus_Projects_CPE1500/H | IDL_Capture/hdl_captu                   | re - hdl_capt | - 0 X                  |

|--------------|---------------------------|--------------------|----------------------------------------------|-------------------------|-----------------------------------------|---------------|------------------------|

| <u>F</u> ile | <u>E</u> dit <u>V</u> iew | <u>S</u> imulation | <u>H</u> elp                                 |                         |                                         | Searc         | h altera.com 🌖         |

|              | 은 🐹 🕑                     | 치 프 XI             | H III XE XE XE                               | R R 🐴 🔜 🏎               |                                         |               |                        |

| Mast         | ter Time Bar: 0           | ps                 | Pointer: 105                                 | .83 ns Interval: 10     | 05.83 ns Start:                         |               | End:                   |

|              | Name                      | Value at           | 0 ps 160                                     | .0 ns 3                 | 20.0 ns                                 | 480.0 ns      | 640.0 ns               |

|              | Name                      | 0 ps               | D ps                                         |                         |                                         |               |                        |

| 5            | Ƴ data_in                 | B 0000             | <u>5000000000000000000000000000000000000</u> |                         | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | ****          | 000000000000000        |

| in<br>—      | i_a                       | в 0                |                                              |                         |                                         |               |                        |

| in<br>—      | i_b                       | в 0                |                                              |                         |                                         |               |                        |

| in<br>—      | i_c                       | в 0                |                                              |                         |                                         |               |                        |

| in<br>—      | i_d                       | во                 |                                              |                         |                                         |               |                        |

| 5            | ⊻ i_sel                   | B 00               | 00                                           | 01                      | X 10                                    |               | 11                     |

| in<br>—      | i_sel                     | во                 |                                              |                         |                                         |               |                        |

| in<br>—      | i_sel                     | во                 |                                              |                         |                                         |               |                        |

| out          | o_mux                     | В 0                |                                              |                         |                                         |               |                        |

| •            | _                         | •                  | sel:0,0<br>mux: i_a                          | sel:1,0<br>mux: i_b     | sel:1,0<br>mux: i_c                     |               | sel:1,1<br>nux: i_d 20 |