# Register Transfer Level

Last updated 12/12/24

# Register Transfer Level

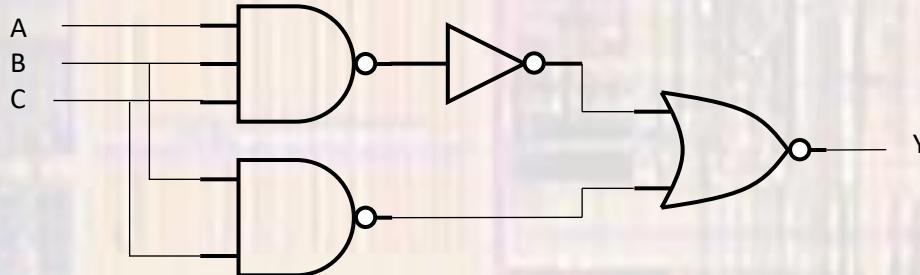

- Combinational Logic

- Outputs are dependent only on current inputs

- Output changes can be triggered by any input change

# Register Transfer Level

- Sequential Logic

- Outputs are dependent on inputs and current STATE

- State

- Collection of outputs and intermediate values stored within the system

- Requires some sort of memory

- Asynchronous - Output changes can be triggered by some input changes

- Synchronous – Outputs changes triggered by a synchronous event – usually a clock

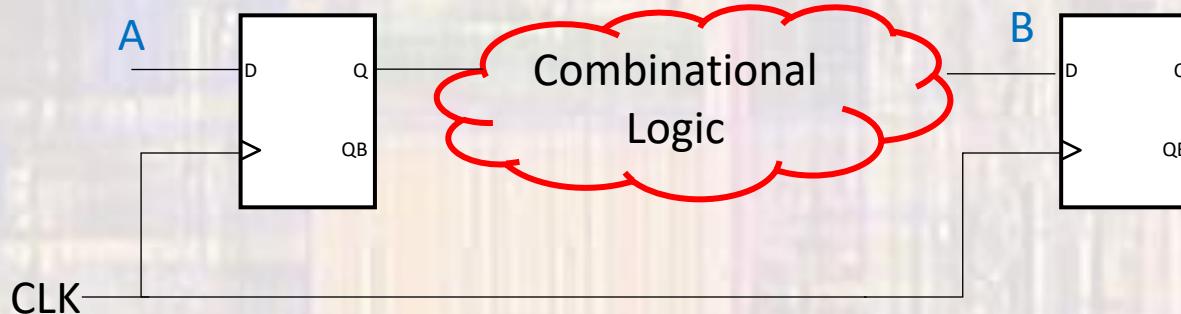

# Register Transfer Level

- Typical Flip-Flop Circuit

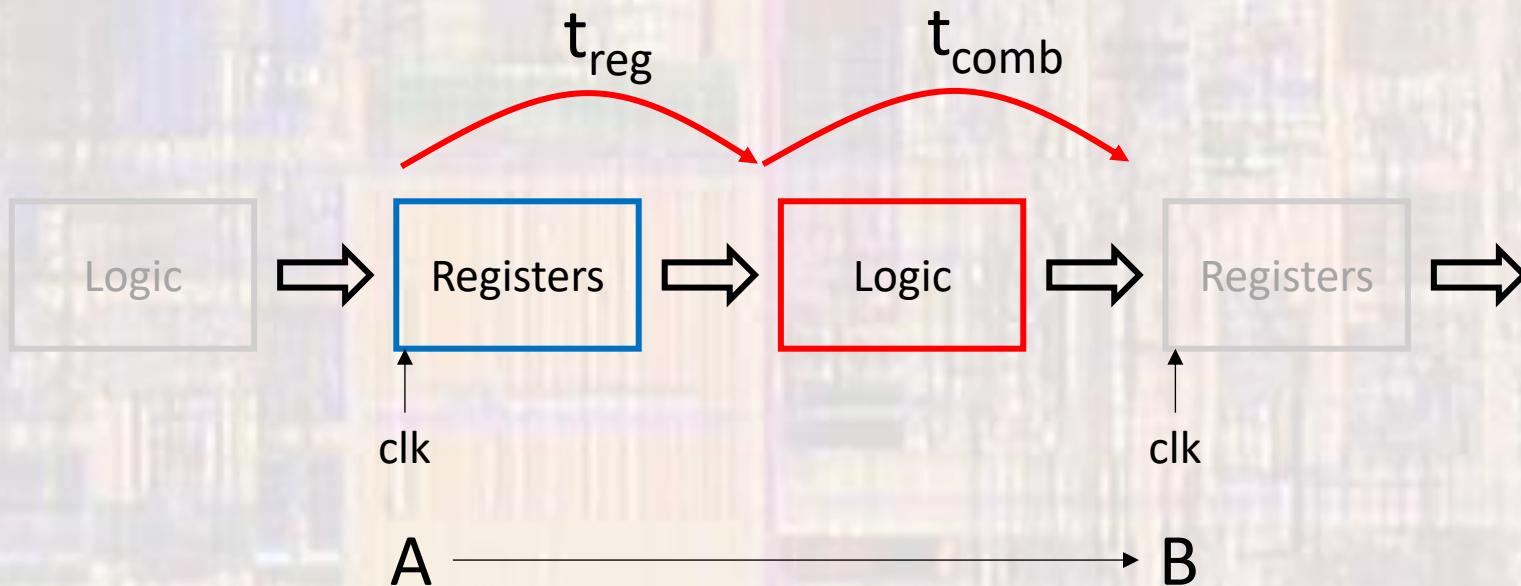

- Need the data to get from point A to point B before the next clock edge occurs

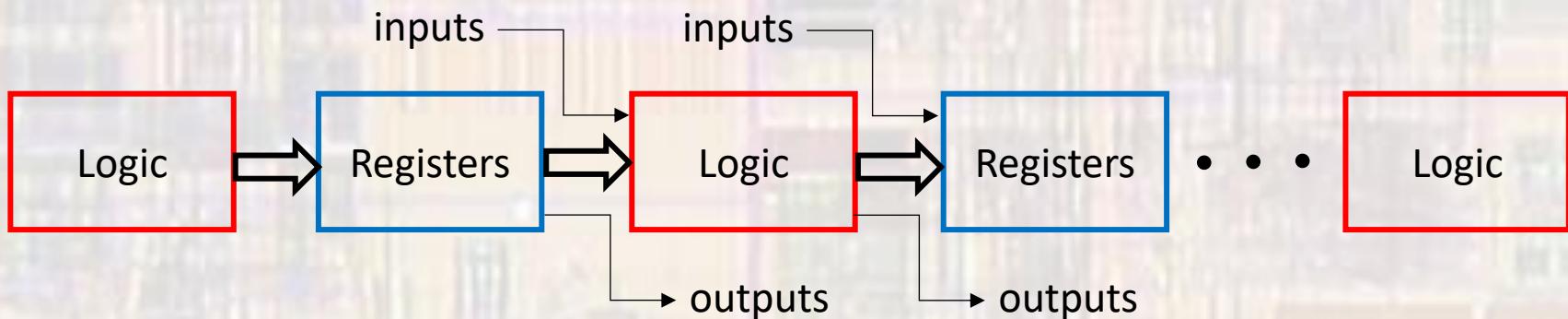

# Register Transfer Level

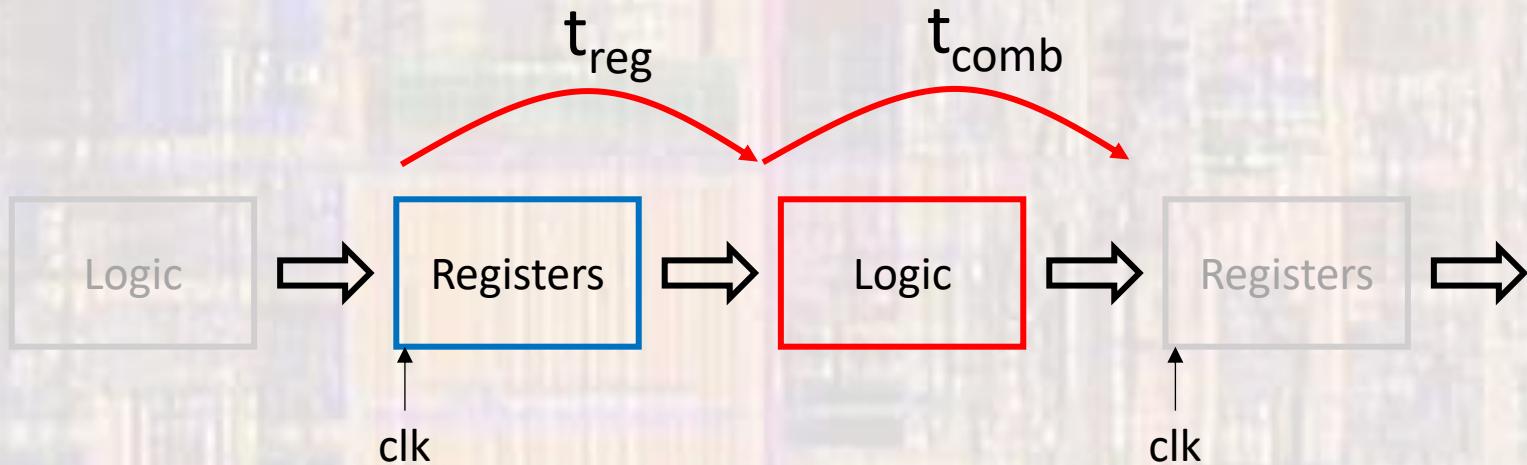

- Register Transfer Architecture

- Synchronous System

- Blocks of combinational logic and registers

- Every intermediate state is captured in a register

# Register Transfer Level

- Register Transfer Architecture

- Synchronous System

- Blocks of combinational logic and registers

- Every intermediate state is captured in a register

- Many I/O paths

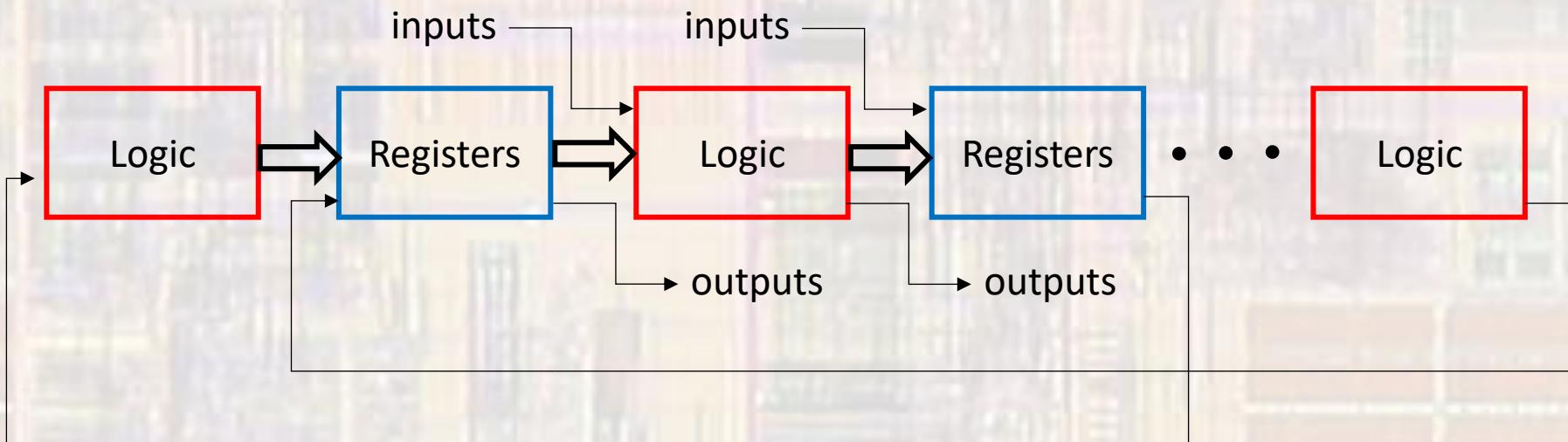

# Register Transfer Level

- Register Transfer Architecture

- Synchronous System

- Blocks of combinational logic and registers

- Every intermediate state is captured in a register

- Many I/O paths

- Many feedback paths

# Register Transfer Level

- Timing

Data must make it from A to B before the next active clock edge (rising)

# Register Transfer Level

- Timing

$$T_{\text{nom}} = t_{\text{CQ}} + t_{\text{comb}}$$

$$T_{\text{nom}} = t_{\text{CQ}} + t_{\text{interconnect1}} + t_{\text{comb}} + t_{\text{interconnect2}} + t_{\text{setup}}$$