## Last updated 12/12/24

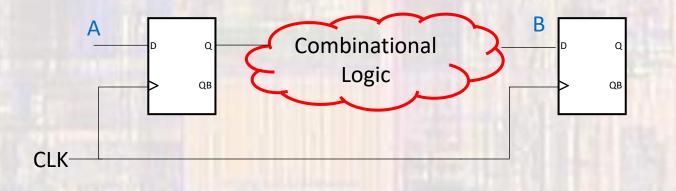

Typical Flip-Flop Circuit

Need the data to get from point A to point B before the next clock edge occurs

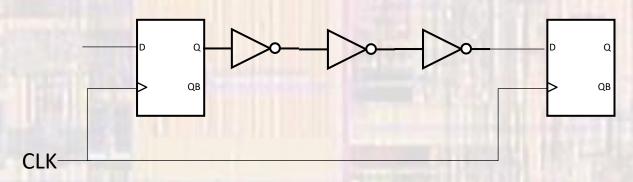

- Flip-Flop Example

- t<sub>PD</sub> INV = 10ps

- t<sub>cq</sub> = 22ps

- t<sub>setup</sub> = 4ps

- t<sub>hold</sub> = 2ps

All values already account for loading

Shortest clock period =  $t_{CQ} + t_{INV} + t_{INV} + t_{INV} + t_{setup} = 56ps$ Fastest clock speed = 17.857GHz

© tj

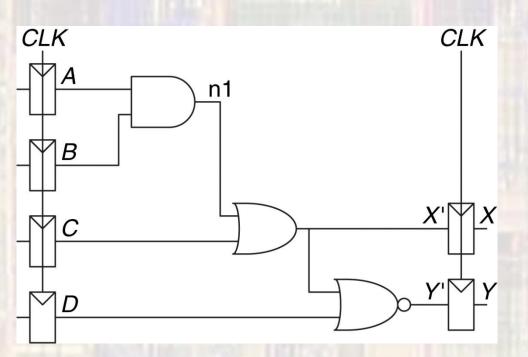

• RTL Example

All values already account for loading

$t_{CQ\_min} = 30ps$  $t_{CQ\_max} = 80ps$  $t_{setup} = 50ps$  $t_{hold} = 60ps$

$t_{pd_{min}}Logic = 25ps$  $t_{pd_{max}}Logic = 40ps$

src: Harris & Harris

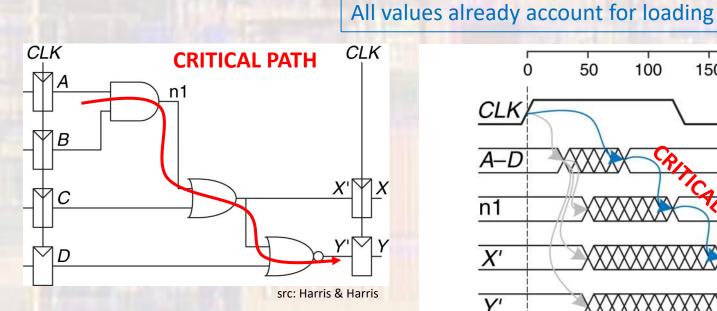

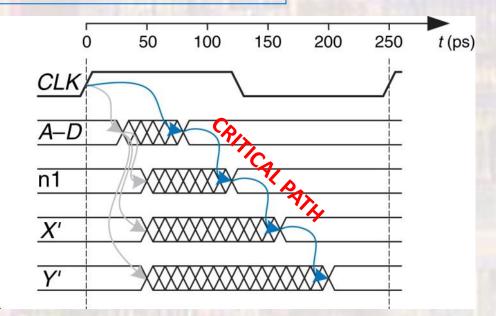

RTL Example – Critical Path

$t_{CQ\_min} = 30ps$  $t_{CQ\_max} = 80ps$  $t_{setup} = 50ps$  $t_{hold} = 60ps$

t<sub>pd\_min</sub>Logic = 25ps t<sub>pd\_max</sub>Logic = 40ps

$$t_{crit} = t_{CQ_{max}} + 3*t_{pd_{max}} + t_{setup}$$

$t_{crit} = 80ps + 3*40ps + 50ps = 250ps$

$F_{max} = 1/250ps = 4GHz$

© tj

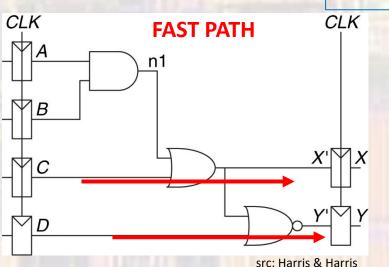

RTL Example – Fast Path

$t_{CQ\_min} = 30ps$  $t_{CQ\_max} = 80ps$  $t_{setup} = 50ps$  $t_{hold} = 60ps$

t<sub>pd\_min</sub>Logic = 25ps t<sub>pd\_max</sub>Logic = 40ps

$t'_{fast} = t_{CQ\_min} + t_{pd\_min}$  $t'_{fast} = 30ps + 25ps = 55ps$  $t'_{fast} < hold time \rightarrow unpredictable output$

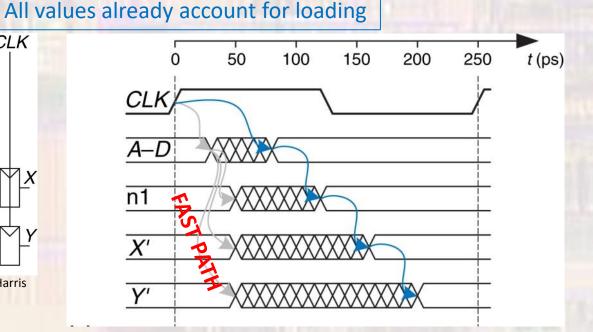

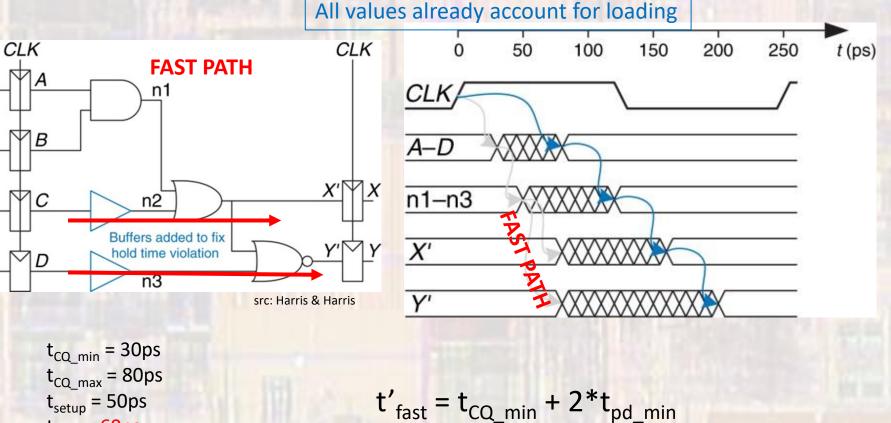

RTL Example – Fast Path - corrected

t'<sub>fast</sub> = 30ps + 2\*25ps = 80ps

$t'_{fast}$  > hold time  $\rightarrow$  predictable output

t<sub>hold</sub> = 60ps

t<sub>pd\_min</sub>Logic = 25ps t<sub>pd\_max</sub>Logic = 40ps

HOLD time reality

In almost all modern systems, T<sub>HOLD</sub> << T<sub>CQ</sub> so Hold requirements rarely are a concern

In most integrated circuit systems, T<sub>HOLD</sub> = 0

- Additional Timing Issues

- Clock skew

- Variation in clock edge arrival time

- Due to path variations (capacitances)

- Reduces maximum clock frequency

- Can create hold time issues

- Clock Gating

- Creates clock skew