Last updated 1/29/25

- Verification via Hardware (DE10)

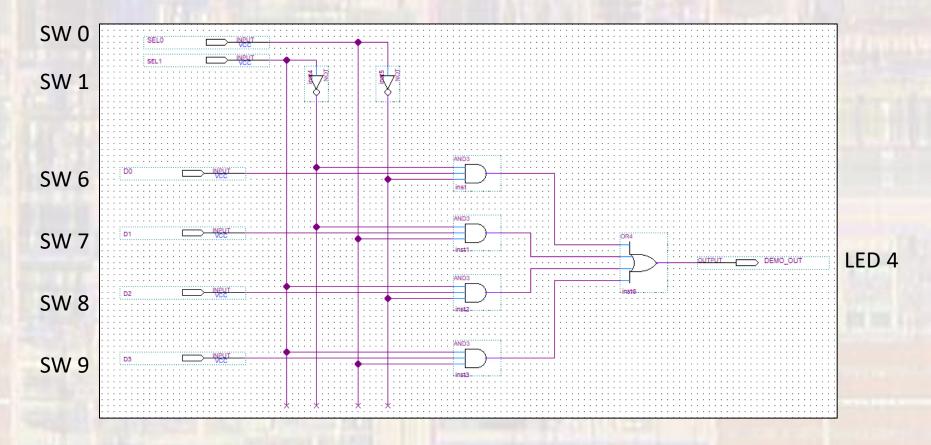

- 1. Create the schematic

- see Quartus Schematic Generation slides

- 2. Verify the design via simulation

- see the Schematic Simulation University Waveforms slides

- 3. Plan the DE10 locations for each pin on the schematic

- 4. Map the schematic pins to DE10 inputs and outputs

- Compile the design

- 6. Download the design to the DE10

- 7. Verify the design

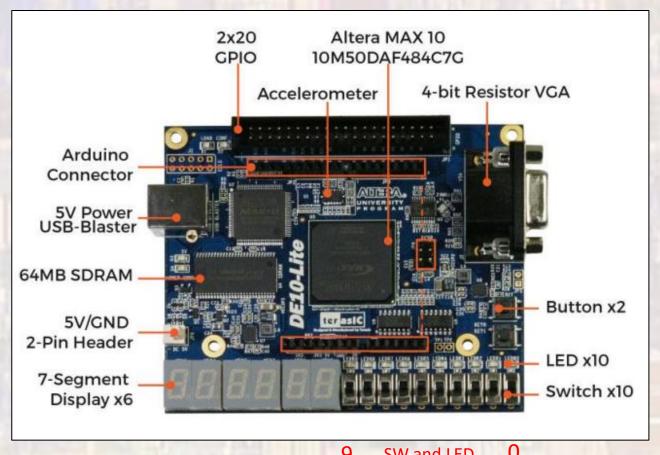

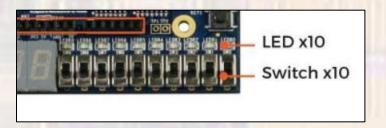

# 3) Plan the DE10 locations for each pin on the schematic

SWx

9 SW and LED

CPE 1500 © ti

# 3) Plan the DE10 locations for each pin on the schematic

# 4) Map the schematic pins to DE10 inputs and outputs

| sel0 |  |

|------|--|

| sel1 |  |

d0 d1 d2 d3

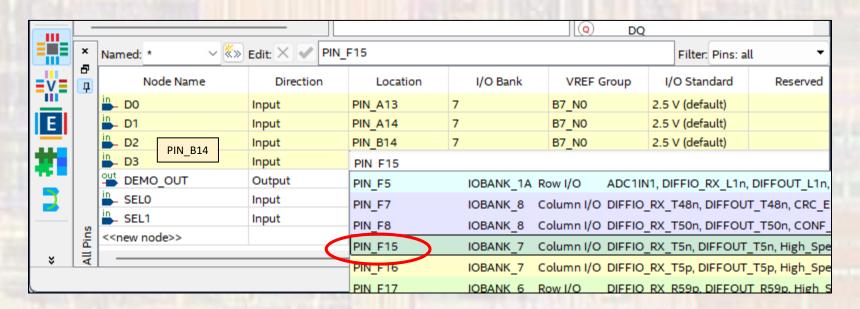

| Signal Name | FPGA Pin No. | Description     | I/O Standard |

|-------------|--------------|-----------------|--------------|

| SW0         | PIN_C10      | Slide Switch[0] | 3.3-V LVTTL  |

| SW1         | PIN_C11      | Slide Switch[1] | 3.3-V LVTTL  |

| SW2         | PIN_D12      | Slide Switch[2] | 3.3-V LVTTL  |

| SW3         | PIN_C12      | Slide Switch[3] | 3.3-V LVTTL  |

| SW4         | PIN_A12      | Slide Switch[4] | 3.3-V LVTTL  |

| SW5         | PIN_B12      | Slide Switch[5] | 3.3-V LVTTL  |

| SW6         | PIN_A13      | Slide Switch[6] | 3.3-V LVTTL  |

| SW7         | PIN_A14      | Slide Switch[7] | 3.3-V LVTTL  |

| SW8         | PIN_B14      | Slide Switch[8] | 3.3-V LVTTL  |

| SW9         | PIN F15      | Slide Switch[9] | 3.3-V LVTTL  |

Table 3-5 Pin Assignment of LEDs

out

| Signal Name | FPGA Pin No. | Description | I/O Standard |

|-------------|--------------|-------------|--------------|

| LEDR0       | PIN_A8       | LED [0]     | 3.3-V LVTTL  |

| LEDR1       | PIN_A9       | LED [1]     | 3.3-V LVTTL  |

| LEDR2       | PIN_A10      | LED [2]     | 3.3-V LVTTL  |

| LEDR3       | PIN_B10      | LED [3]     | 3.3-V LVTTL  |

| LEDR4       | PIN_D13      | LED [4]     | 3.3-V LVTTL  |

| LEDR5       | PIN_C13      | LED [5]     | 3.3-V LVTTL  |

| LEDR6       | PIN_E14      | LED [6]     | 3.3-V LVTTL  |

| LEDR7       | PIN_D14      | LED [7]     | 3.3-V LVTTL  |

| LEDR8       | PIN_A11      | LED [8]     | 3.3-V LVTTL  |

| LEDR9       | PIN_B11      | LED [9]     | 3.3-V LVTTL  |

demo\_out

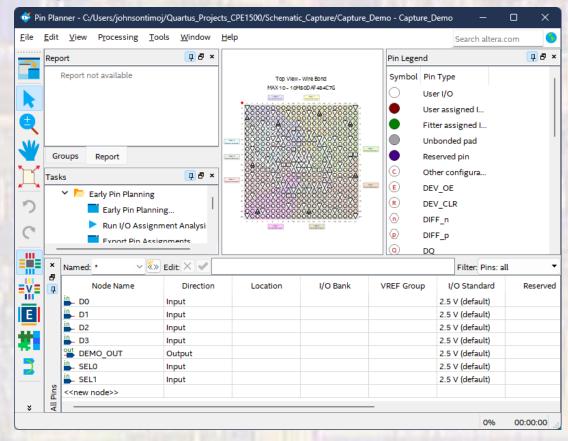

- 4) Map the schematic pins to DE10 inputs and outputs

- Assignments → Pin Planner

# 4) Map the schematic pins to DE10 inputs and outputs

- Double click on the location column for a pin

- Select the expand arrow

- Scroll until the desired pin is found and select it

- Close the Pin Planner when finished

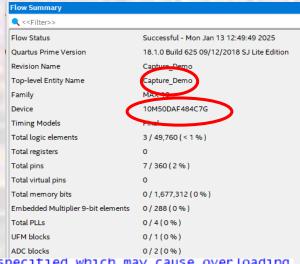

## 5) Compile the design

- Save

- Right click on the design and select Set as Top-Level Entity

- Processing → Start Compilation

- Verify success

18236 Number of processors has not been specified which may cause overloading 10905 Generated the EDA functional simulation netlist because it is the only s

204019 Generated file Capture\_Demo.vho in folder "C:/Users/johnsontimoj/Quartus

Quartus Prime EDA Netlist Writer was successful. 0 errors, 3 warnings

293000 Quartus Prime Full Compilation was successful. 0 errors, 19 warnings

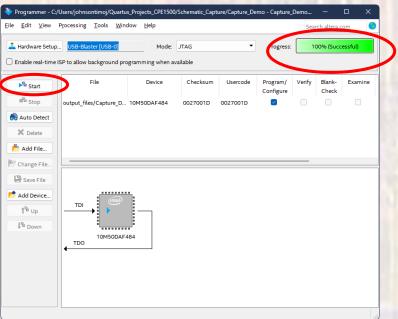

## 6) Download the design to the DE10

- Plug the DE10 board into your laptop USB port

- Should be lots of flashing lights

- Tools → Programmer

- The USB Blaster interface should have been setup when you setup Quartus – see Quartus Setup Slides if it is not visible

- Start

# 7) Verify the design

- Choose a value for SW1 and SW0 (SEL(1) and SEL(0))

- Verify only the associated SW(9-6) toggle the LED on/off

| SEL1 | SEL0 | SW/LED OUT                          |

|------|------|-------------------------------------|

| 0    | 0    | Only SW 6 = 1 causes LED 5 to light |

| 0    | 1    | Only SW 7 = 1 causes LED 5 to light |

| 1    | 0    | Only SW 8 = 1 causes LED 5 to light |

| 1    | 1    | Only SW 9 = 1 causes LED 5 to light |