## Last updated 1/21/25

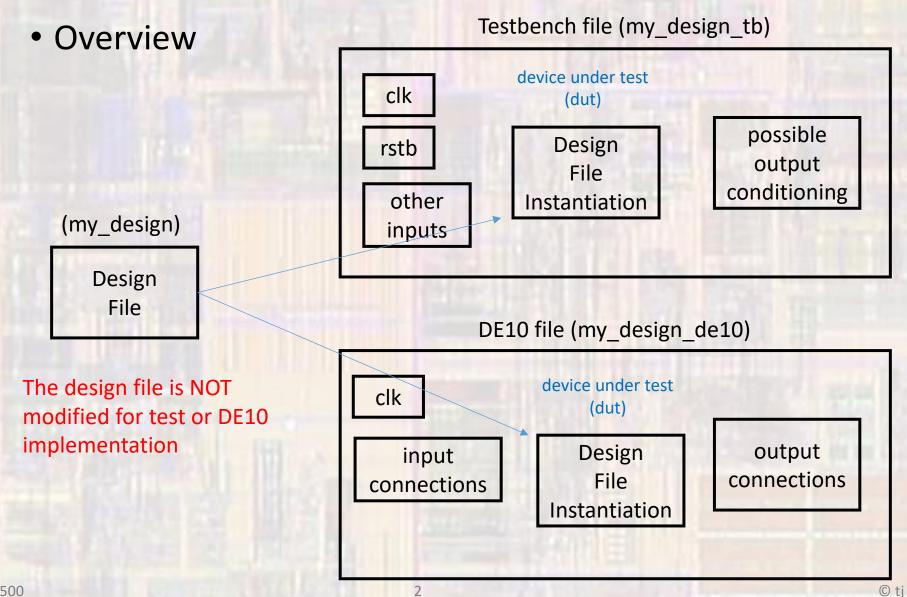

- Quartus Interaction and the DE10

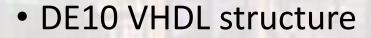

- Quartus provides a file-based interface to map a VHDL file to the DE10

- This allows a VHDL design to map to different FPGAs by simply using a different mapping file

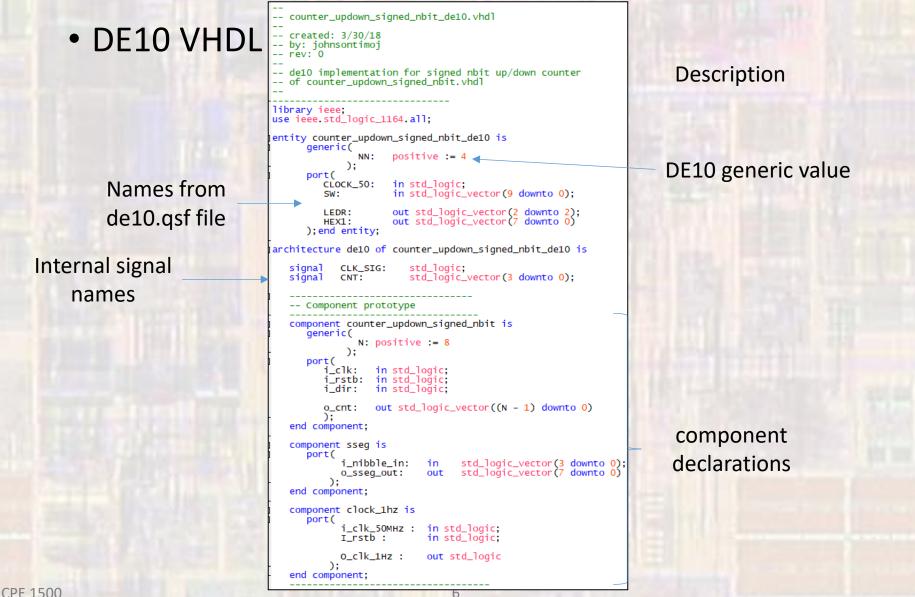

- Each pin on the DE10 family of FPGAs is mapped to a unique name

- Mapping is stored in the de10.qsf file

- The de10.qsf file is imported to the project

- The unique names are used as the port names in the DE10 VHDL implementation file

© ti

• We will use the structure my\_top\_entity\_de10 to name this file

- DE10 Implementation File

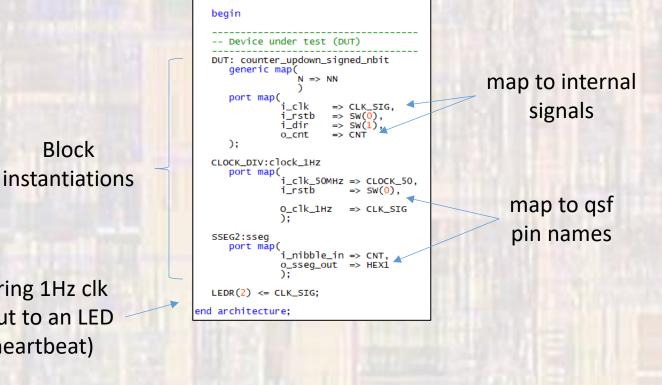

- The de10 implementation file must be synthesizable

- Only synthesizable constructs allowed

- Our best practices

- Name the de10 file based on the top level entity name

- add \_\_de10 to the top level entity name

- e.g. counter\_mod11 → counter\_mod11\_de10

- If extra processing is required, it is placed in the DE10 file

- Never modify the top level entity to make it work on the DE10

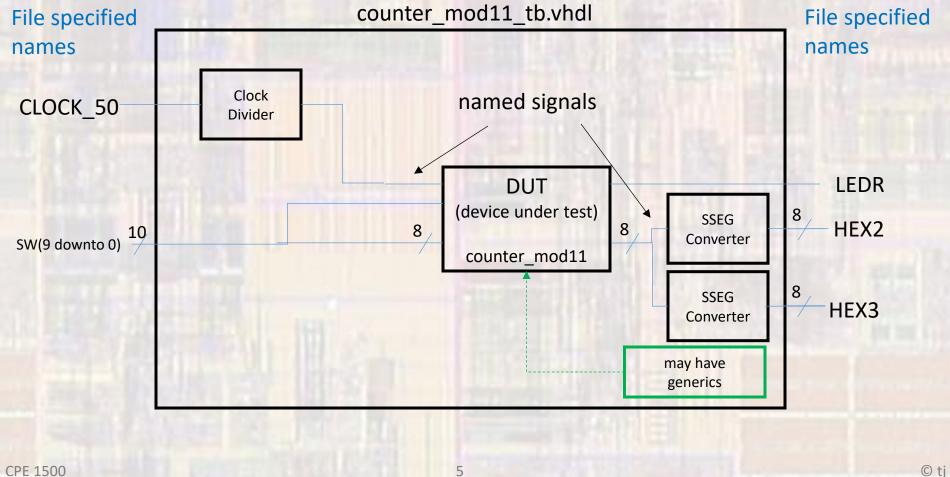

- Typical additional blocks include:

- Clock dividers to allow is to slow the effective clock rate down from 50MHz to just a few Hz

© ti

Seven Segment Drivers

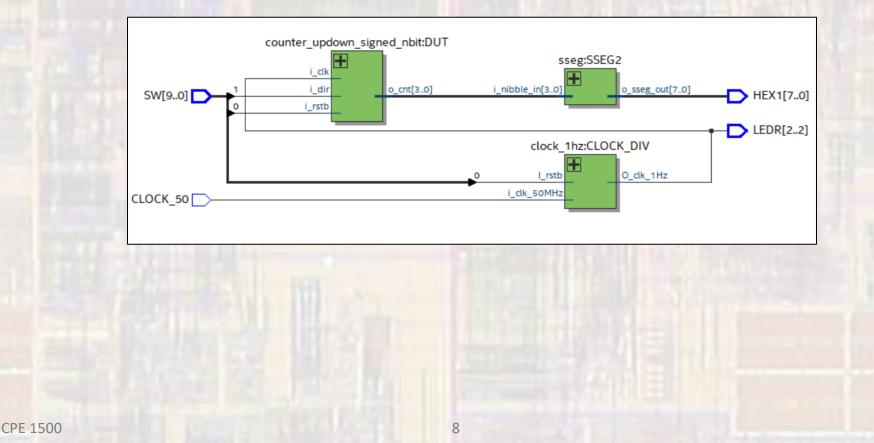

DE10 Graphical Structure

Block

© tj

- DE10 VHDL structure

- Set the DE10 file as the Top Level Entity