Last updated 3/26/25

- Four major VHDL memory solutions

- Mux based

- Only applicable for ROMs

- FlipFlop based

- Very large only acceptable for very small memories

- Inferred

- Memory is implemented in a pre-built memory block

- Memory block must exist in the platform

- Tightly coupled memory small but very fast

- General memory large and not as fast

- External

- The memory interface is implemented

- The memory itself is a separate chip

- VHDL solution for memories

- An array of std\_logic\_vectors

- Coded just like the non-optimized long array of data words

N words x M bits/word

N array elements x SLV

- Array construct

- New type, that has array type as its basis

type my\_new\_type is array (0 to depth) of some\_vhdl\_type

- Memory construct

- Uses std\_logic\_vector

- No understanding of the values (signed/unsigned) is assumed, just bits

type my\_memory is array (0 to depth) of std\_logic\_vector((wordwidth - 1) downto 0);

- ROM Inferred

- Using SRAM integrated on the FPGA as our memory storage element – configured with no write path

- The inferred memories on our FPGA all require synchronous read paths

- To force an inferred memory the read path must be synchronous

- ROM Inferred

- Fixed values in the Memory signal

- Synchronous read path

No write path

```

architecture behavioral of rom_inferred_constants is

-- ROM structure

type rom_type is array (0 to (mem_depth - 1)) of std_logic_vector ((mem_width - 1) downto 0);

-- rom inferred constants.vhdl

ROM contents

signal my_ROM: rom_type:=(

-- created 4/25/17

0 => X"C010"

-- tj

1 \Rightarrow X''CO4A''

2 => X"5180"

-- rev 0

3 => X"02C0"

X"4640"

-- Inferred rom with constants for values

8 => X"2E40"

9 => X"6B00"

10 => X"F000".

-- inputs: clk, addr

-- outputs: data

others => X"F000"

);

library ieee;

begin

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

process (i_clk)

use ieee.math_real.all;

begin

if (rising_edge(i_clk)) then

entity rom_inferred_constants is

o_data <= my_ROM(to_integer(unsigned(i_addr)));

generic(

mem_width: positive := 16;

end process;

mem_depth: positive := 16

end architecture;

port(

i_clk:

std_logic:

std_logic_vector(((integer(ceil(log2(real(mem_depth))))) - 1) downto 0);

o_data: out std_logic_vector((mem_width - 1) downto 0)

end entity;

```

- SRAM Inferred

- Using SRAM integrated on the FPGA as our memory storage element

- The inferred memories on our FPGA all require synchronous read paths

- To force an inferred memory the read path must be synchronous

SRAM – inferred

4K word, 1B/w inferred SRAM

• 4K x 8

```

-- sram_inferred.vhdl

architecture behavioral of sram inferred is

-- created 4/25/17

-- create type

type sram_type is array (0 to (mem_depth - 1)) of std_logic_vector ((mem_width - 1) downto 0);

-- create memory

-- synchronous RAM using inferred memories

signal mySRAM: sram_type;

begin

-- Inputs: clk, addr, we_b, data_in

-- SRAM write process

-- Outputs: data_out

process (i_clk)

library ieee;

if (rising_edge(i_clk)) then

use ieee.std_logic_1164.all;

- read logic

if(i_we_b \stackrel{\checkmark}{=}'0') then

use ieee.numeric_std.all;

mySRAM(to_integer(unsigned(i_addr))) <= i_data_in;</pre>

use ieee.math_real.all:

--registered output

entity sram_inferred is

o_data_out <= mySRAM(to_integer(unsigned(i_addr)));

Synchronous read

generic(

end if:

mem_width: positive := 8;

end process;

to create inferred memory

mem_depth: positive := 4096

nd behavioral:

port(

in std_logic;

in std_logic;

i_clk:

i_we_b:

in std_logic_vector(((integer(ceil(log2(real(mem_depth))))) - 1) downto 0);

i_addr:

i_data_in: in std_logic_vector((mem_width - 1) downto 0); o_data_out: out std_logic_vector((mem_width - 1) downto 0)

end entity;

```

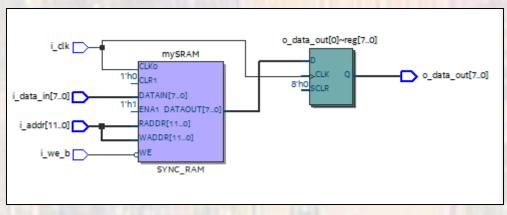

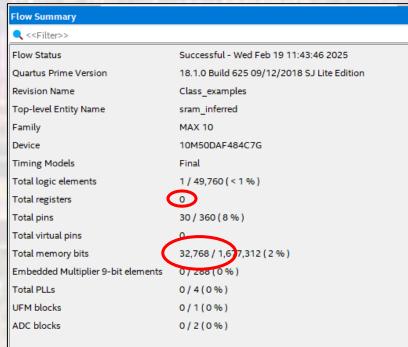

- SRAM inferred

- 4K x 8

There is an RTL model for this memory

The implementation used inferred SRAM on the FPGA

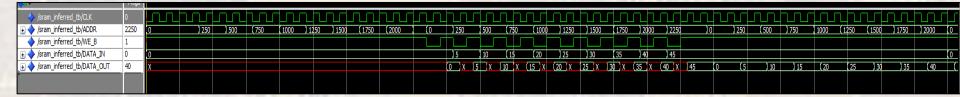

- SRAM Inferred test bench

- 4K x 8

```

Run Process

run: Process

-- note - no sensitivity list allowed

beain

-- Initalize values

Not all addresses tested

ADDR <= (others => '0');

DATA_IN <= (others => '0');

Not all bit values tested

WE_B <= '1';

-- Read from a few addresses

for i in 0 to 9 loop

wait for 2*PER:

ADDR <= std_logic_vector(to_unsigned(i*250,(integer(ceil(log2(real(mem_depth)))))));

end loop:

-- Write to a few addresses

for i in 0 to 9 loop

wait for 1*PER:

ADDR <= std_logic_vector(to_unsigned(i*250,(integer(ceil(log2(real(mem_depth)))))));

DATA_IN <= std_logic_vector(to_unsigned(i*5, mem_width));

WE_B <= '0';

wait for 1*PER;

WE_B <= '1':

end loop;

-- Read from a few addresses

for i in 0 to 9 loop

wait for 2*PER;

ADDR <= std_logic_vector(to_unsigned(i*250,(integer(ceil(log2(real(mem_depth)))))));

end loop:

end process run;

```

|                            | Misgs | sgs |      |    |      |    |      |    |  |    |  |     |  |      |  |     |

|----------------------------|-------|-----|------|----|------|----|------|----|--|----|--|-----|--|------|--|-----|

| /sram_inferred_tb/CLK      | 0     |     |      |    |      |    |      |    |  |    |  |     |  |      |  |     |

| /sram_inferred_tb/ADDR     | 2250  |     | 1750 |    | 2000 |    | 2250 |    |  | (O |  | 250 |  | 500  |  | 750 |

| /sram_inferred_tb/WE_B     | 1     |     |      |    |      |    |      |    |  |    |  |     |  |      |  |     |

| /sram_inferred_tb/DATA_IN  | 0     | 30  | 35   |    | 40   |    | 45   |    |  |    |  |     |  |      |  |     |

| /sram_inferred_tb/DATA_OUT | 40    | 30  | X    | 35 | Х    | 40 | Х    | 45 |  | χo |  | (5  |  | ( 10 |  |     |

|                            |       |     |      |    |      |    |      |    |  |    |  |     |  |      |  |     |

- Memory Test Benches

- A proper memory testbench would test:

- All addresses

- All bits 0 and 1

- Read ROMs, R/W for RAMs

- Write\_enable\_bar functionality