Last updated 12/18/24

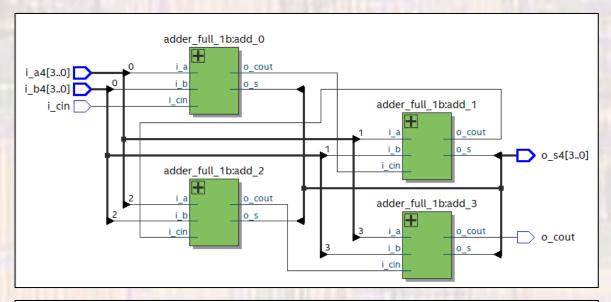

- Structural VHDL implements hierarchical designs

- Instantiates blocks into a more complex design

- Complex Designs

- Test Benches

- Can include behavioral VHDL content

#### Structural VHDL file components

- Header

- Description of who created the file

- Description of the purpose of the block

- Description of inputs and outputs

- Inclusions

- Any libraries that will be referenced in the design

- Entity

- Formal definition of the inputs and outputs

- Any generic parameters are defined here also

- Architecture

- Internal signal declarations

- Including those required for connecting structural blocks

- Component declarations for hierarchical blocks used in the design

- Instantiation (hook-up) of any hierarchical blocks used in the design

- HDL description of the desired additional functionality

- Concurrent, sequential, structural logic

Structural VHDL file components - example

comments begin with 2 dashes

-continue to the end of the

current line

```

-- adder_full_4b.vhdl

-- by: tj

-- created: 12/18/24

-- version: 0.0

-- 4 bit adder to show block instantiation

-- inputs: - a, b, cin

-- outputs: - sum, cout

```

Document who, when, what and how

Should be sufficient to allow a co-worker to use/modify the design

Structural VHDL file components - example

```

Library inclusions

library IEEE;

use ieee.std_logic_1164.all;

statements end with a semi-colon

Include the basic library definitions

```

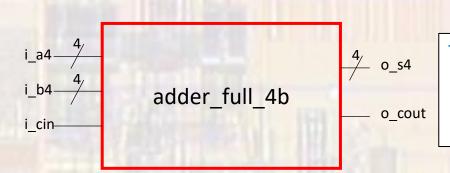

Structural VHDL file components - example

```

entity adder_full_4b is

port( i_a4:

std_logic_vector(3 downto 0);

in

i b4:

std_logic_vector(3 downto 0);

in

the entity name must match the

i_cin:

std loaic:

in

file name

std_logic_vector(3 downto 0);

o_s4:

out

o_cout:

out

std_logic

Entity

end entity;

```

```

port format:

name : direction signal_type ;

directions: in, out, bidir

signal types: std_logic

std_logic_vector(...)

```

i or o

We will prepend ports with

The Entity is the external view of the block

Ports are the i/o connections of the block

Ports have a direction but no interpretation

Wires or groups of wires

Structural VHDL file components - example

```

architecture structural of adder_full_4b is

-- 1 bit full adder prototype

component adder_full_1b is

Architecture

in std_logic;

port( i_a:

in std_logic;

i_cin: in std_logic:

out std_logic;

o_cout: out std_logic

end component:

signal co_0: STD_LOGIC;

-- carry out stage 0

-- carry out stage 1

signal co_1: STD_LOGIC;

-- carry out stage 2

signal co_2: STD_LOGIC;

begin

add_0:

adder_full_1b port map( i_a

i_a4(0),

i_b4(0),

i_cin

i_cin,

0_S

0_{54}(0),

o cout

i_a4(1),

i_b4(1),

add_1:

adder_full_1b port map( i_a

i b

i_cin

co_0,

0_{54}(1),

o_cout

);

add_2:

adder_full_1b port map( i_a

i_a4(2),

i_b4(2),

i_b

i_cin

co_1,

o_s4(2),

0_S

o_cout

);

adder_full_1b port map( i_a

add_3:

i_a4(3),

i_b4(3),

i_b

i_cin

0_S

);

end architecture;

```

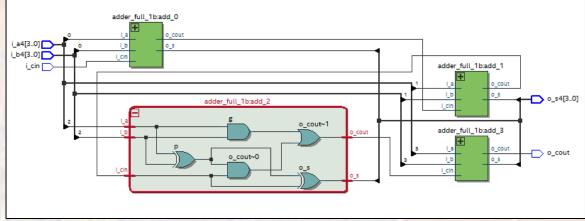

Before the begin

Block prototypes

Internal signals

Constants used for readability

After the begin

Instantiation of blocks

Use EXPLICITE port mapping

HDL for the specific application

Structural VHDL file components - example

```

architecture structural of adder_full_4b is

-- 1 bit full adder prototype

component adder_full_1b is

Architecture

in std_logic;

port( i_a:

in std_logic;

i_cin: in std_logic:

out std_logic;

o_cout: out std_logic

end component:

signal co_0: STD_LOGIC; -- carry out stage 0

signal co_1: STD_LOGIC; -- carry out stage 1

signal co_2: STD_LOGIC; -- carry out stage 2

begin

add_0:

adder_full_1b port map( i_a

i_a4(0),

i_b4(0),

i_cin

i_cin,

0_S

0_{54}(0),

o cout

i_a4(1),

i_b4(1),

add_1:

adder_full_1b port map( i_a

i b

i_cin

co_0,

0_{54}(1),

o_cout

);

add_2:

adder_full_1b port map( i_a

i_a4(2),

i_b4(2),

i_b

i_cin

co_1,

o_s4(2),

0_S

o_cout

);

add_3:

adder_full_1b port map( i_a

i_a4(3),

i_b4(3),

i_b

i_cin

co_2,

0_S

0_{54}(3)

o_cout

);

end architecture;

```

Component prototype

The entity code for the desired block with entity replaced with component

```

signal format:

signal name : signal_type ;

signal types: std_logic

std_logic_vector(...)

```

Structural VHDL file components - example

```

architecture structural of adder_full_4b is

- 1 bit full adder prototype

component adder_full_1b is

Architecture

in std_logic;

i_cin:

in std_logic:

out std_logic;

o_cout: out std_logic

end component:

Explicit Port Mapping

signal co_0: STD_LOGIC;

-- carry out stage

signal co_1: STD_LOGIC;

-- carry out stage

instantiated block port name => structural design signal or port name,

signal co_2: STD_LOGIC;

-- carry out stage

begin

add_0:

adder_full_1b port map( i_a

i_a4(0),

i_b4(0),

i_cin

i_cin,

o_s4(0).

0_S

o cout

add_1:

adder_full_1b port map( i_a

i_a4(1),

i_b4(1).

i_cin

co_0,

0_{54}(1)

add_2:

adder_full_1b port map( i_a

i_a4(2),

```

(adder\_full\_1b instance add\_0 - port o\_s) is mapped to (adder\_full\_4b - port o\_s4 bit 1)

```

o_cout => o_cout

end architecture;

```

CPE 1500

```

adder_full_4b.vhdl

by: tj

- created: 12/18/24

version: 0.0

4 bit adder to show block instantiation

- inputs: - a, b, cin

outputs: - sum, cout

library IEEE;

use ieee.std_logic_1164.all;

entity adder_full_4b is

port( i_a4: in

i_b4: in

i_cin: in

ider_ruil_4b is

i_aa: in std_logic_vector(3 downto 0);

i_ba: in std_logic_vector(3 downto 0);

i_cin: in std_logic_vector(3 downto 0);

o_sa: out std_logic_vector(3 downto 0);

o_cout: out std_logic_vector(3 downto 0);

rchitecture structural of adder_full_4b is

-- 1 bit full adder prototype

component adder_full_1b is

port( i_a:

i_b:

in std_logic;

i_cin:

in std_logic;

out std_logic;

o_s:

o_cout: out std_logic

end component;

signal co_0: STD_LOGIC;

signal co_1: STD_LOGIC;

signal co_2: STD_LOGIC;

-- carry out stage 0

-- carry out stage 1

-- carry out stage 2

adder_full_1b port map(

i_a4(0),

i_b4(0),

i_cin,

o_s4(0),

co_0

i_cin

o_cout =>

i_a4(1),

i_b4(1),

co_0,

o_s4(1),

i_cin

=>

);

add_2: adder_full_1b port map( i_a

i_a4(2),

i_b4(2),

i_cin

co_1,

o_s4(2),

o_s

o_cout

adder_full_1b port map( i_a

i_a4(3),

i_b4(3),

i_cin

co_2,

o_s4(3),

o_cout

);

end architecture;

```

#### L file components - example