Last updated 1/7/25

VHDL is not a programming language It is a hardware description language

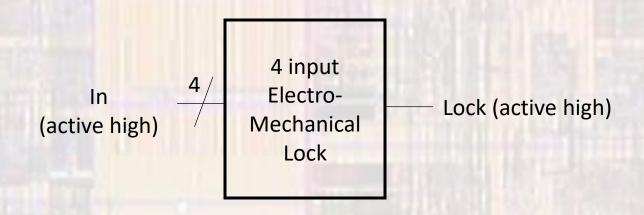

Create a hardware description for an electronic version of a binary 4 input combination lock

1/0 inputs

- Create a hardware description for an electronic version of a binary 4 input combination lock

- Design Decisions

- Default state (locked or unlocked)?

- Input signal activation condition (high or low)?

- Output signal activation condition (lock or unlock)?

- Additional use case information

- Target customer is private and commercial gym locker rooms

- Normally the lockers will be unlocked so customers can place items in the locker and then lock it

- Default to unlocked

- Output signal will be active high to lock

- Create a hardware description for an electronic version of a binary 4 input combination lock

- Block Diagram

Create a hardware description for an electronic version of a binary 4 input combination lock

```

Use generics for values that

can be changed in different

-- lock_4in_binary.vhdl

versions of the design

- created 7/5/2018

-- rev 0

-- 4 input (binary) lock - brute-force

- active high inputs, active high output - locked

architecture behavioral of lock_4in_binary is

begin

-- Inputs: in 4 bits

with i_in select o_lock <=

-- Outputs: lock

'1' when (COMBINATION),

'0' when others:

library ieee:

end behavioral:

use ieee.std_logic_1164.all;

entity lock_4in_binary is

generic(

COMBINATION: std_logic_vector(3 downto 0) := "1011"

port (

in std_logic_vector(3 downto 0);

o_lock: out std_logic

end entity:

can use a signal name

instead of an explicit vector

```

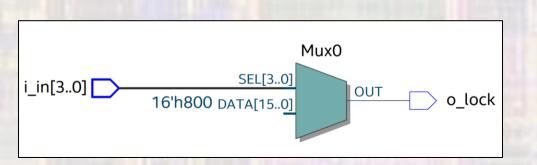

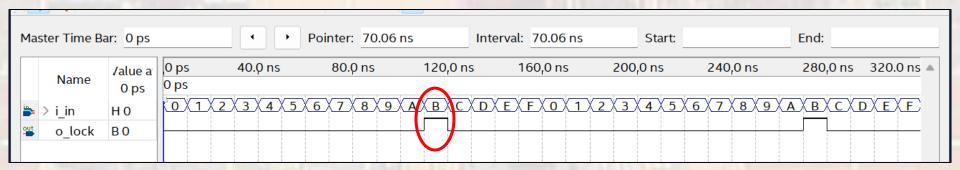

Create a hardware description for an electronic version of a binary 4 input combination lock

© ti

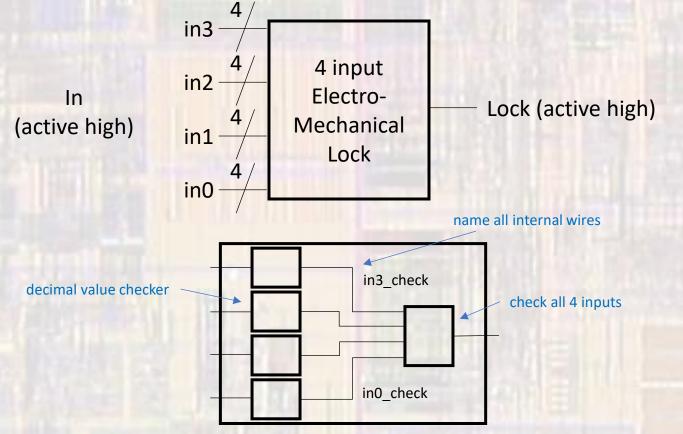

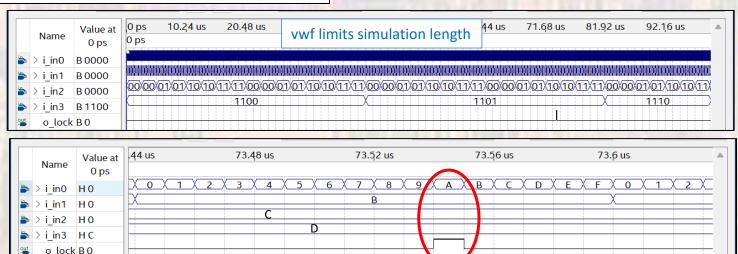

- Create a hardware description for an electronic version of a decimal 4 input combination lock

- Block Diagram

CPE 1500 8 © tj

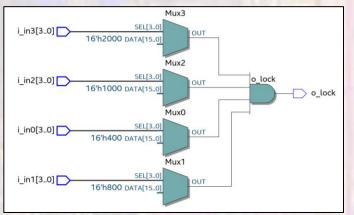

Create a hardware description for an electronic version of a decimal 4 input combination lock

```

architecture behavioral of lock_4in_decimal is

signal in0_check: std_logic;

signal in1_check: std_logic;

signal in2_check: std_logic;

-- lock_4in_decimal.vhdl

signal in3_check: std_logic;

-- created 7/5/2018

begin

-- tj

with i_in0 select in0_check <=

'1' when (COMBINATIONO),

'0' when others;

with i_in1 select in1_check <=

'1' when (COMBINATION1),

-- 4 input (decimal) lock - brute-force

-- active high inputs, active high output - locked

'0' when others:

with i_in2 select in2_check <=

'1' when (COMBINATION2),

'0' when others:

-- Inputs: inO - in3, 4 bits each

with i_in3 select in3_check <=

'1' when (COMBINATION3),

-- Outputs: lock

'0' when others:

library ieee;

o_lock <= in0_check AND in1_check AND in2_check AND in3_check;

use ieee.std_logic_1164.all;

end behavioral;

entity lock_4in_decimal is

generic(

COMBINATIONO: std_logic_vector(3 downto 0)

COMBINATION1: std_logic_vector(3 downto 0) := "1011";

COMBINATION2: std_logic_vector(3 downto 0) := "1100";

COMBINATION3: std_logic_vector(3 downto 0) := "1101"

port (

in std_logic_vector(3 downto 0);

in std_logic_vector(3 downto 0);

in std_logic_vector(3 downto 0);

i_in0:

in std_logic_vector(3 downto 0);

i_in3:

o_lock: out std_logic

end entity;

```

Create a hardware description for an electronic version of a decimal 4 input combination lock

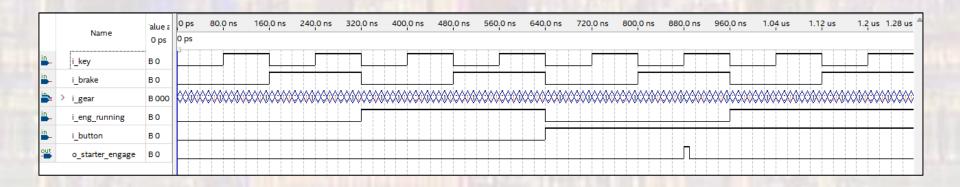

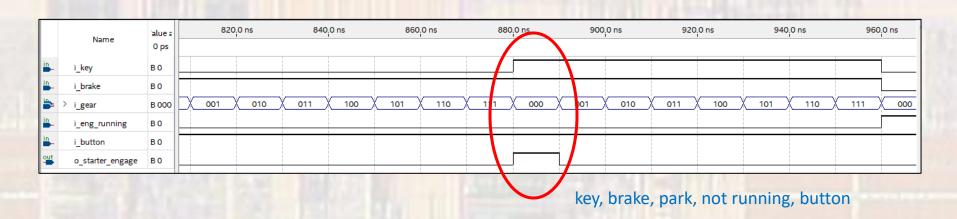

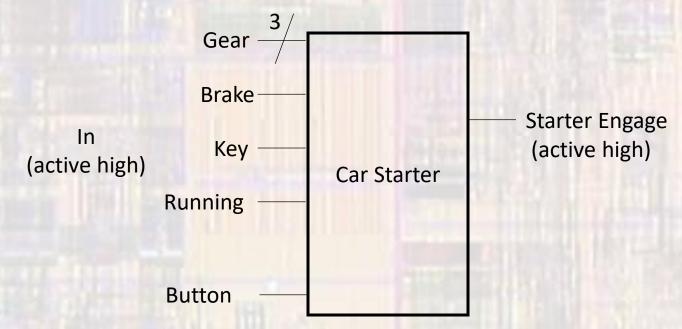

- Create a hardware description for a car starter mechanism

- Start conditions

- Brake on

- Key in range

- Not running

- In park

- Button pushed

- All inputs active high

- Output active high

- Create a hardware description for a car starter mechanism

- Block Diagram

Gear encoding: 000 – Park, 001 – Neutral, 100 – Reverse, 010 - L1, 011 – L2

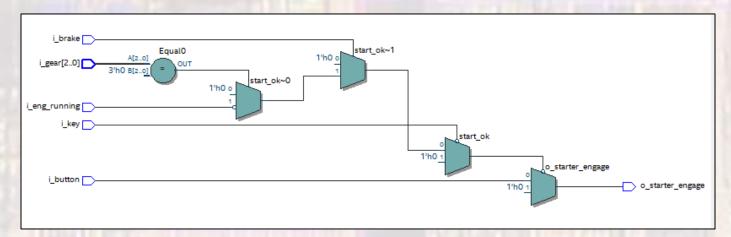

Create a hardware description for a car starter mechanism

```

-- starter_car.vhdl

-- created 7/5/2018

-- tj

-- car starter module - brute-force

-- active high inputs, active high outputs

-- park - 000

-- Inputs: key, brake, gear (3 bit), button, eng running,

-- Outputs: starter engage

library ieee;

use ieee.std_logic_1164.all;

entity starter_car is

generic(

PARK: std_logic_vector(2 downto 0) := "000"

i_key:

in std_logic;

i_brake:

in std_logic;

in std_logic_vector(2 downto 0);

o_starter_engage: out std_logic

end entity;

```

```

architecture behavioral of starter_car is

signal start_ok: std_logic;

begin

start_ok <= '0' when (i_key = '0') else

'0' when (i_brake = '0') else

'0' when (i_gear /= (PARK)) else

'0' when (i_eng_running = '1') else

'1';

o_starter_engage <= '0' when (start_ok = '0') else

'1' when (i_button = '1') else

'0';

end architecture;</pre>

```

Create a hardware description for a car starter mechanism

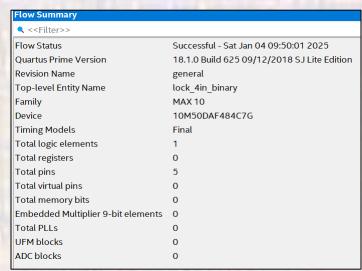

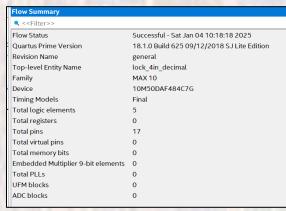

| Flow Summary                       |                                             |

|------------------------------------|---------------------------------------------|

| < <filter>&gt;</filter>            |                                             |

| Flow Status                        | Successful - Mon Jan 06 09:24:41 2025       |

| Quartus Prime Version              | 18.1.0 Build 625 09/12/2018 SJ Lite Edition |

| Revision Name                      | general                                     |

| Top-level Entity Name              | starter_car                                 |

| Family                             | MAX 10                                      |

| Device                             | 10M50DAF484C7G                              |

| Timing Models                      | Final                                       |

| Total logic elements               | 2                                           |

| Total registers                    | 0                                           |

| Total pins                         | 8                                           |

| Total virtual pins                 | 0                                           |

| Total memory bits                  | 0                                           |

| Embedded Multiplier 9-bit elements | 0                                           |

| Total PLLs                         | 0                                           |

| UFM blocks                         | 0                                           |

| ADC blocks                         | 0                                           |

Create a hardware description for a car starter mechanism