# Memory Overview

## Last updated 7/1/21

Many Types of memory

- Paper tape

- Cards

- Magnetic Tape

- Floppy Disk

- Hard Drive (Magnetic)

- Optical Drive

- Integrated Circuit Memory

- 2 Key Concepts for Integrated Circuit memory

- ROM

- ROM read only memory

- fixed values memory cannot be changed

- RAM

- RAM random access (really R/W)

- memory can be changed

- Integrated Circuit Memory

- Non Volatile

- Retains it's values even when power is removed

- ROM

- NAND and NOR Flash

- EPROM, EEPROM

- Volatile

- Loses its values when power is removed

- Static Retains value without any extra effort

- Registers

- SRAM Static RAM

- Dynamic Requires periodic refresh or values will degrade

- DRAM Dynamic RAM

- SDRAM Synchronous DRAM (DDR, DDR2, DDR3, DDR4, ...)

- Integrated Circuit Memory

- Minimum logical element

- 1 bit (b)

- Has a logical value of '0' or '1'

- Has a physical value of "vdd" or "gnd"

- 5v, 3.3v, <mark>2.4v, 1.8v, 1.2v</mark>

- Minimum accessible storage element

- 1- Byte (B)

- 8 bits

- Minimum Addressable element

- 1 Word

- Situational dependent length

- 1B, 2B, 4B, 8B, 16B, ...

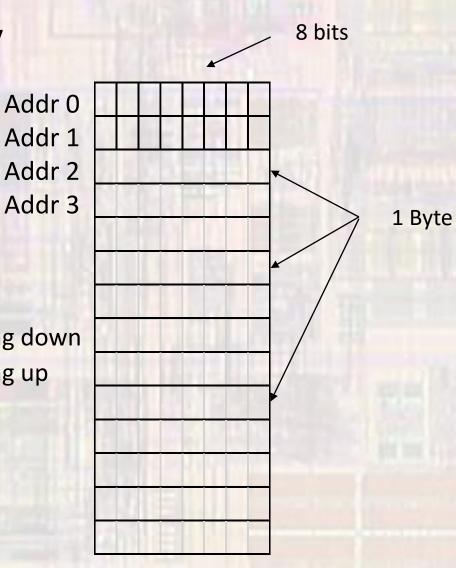

- Integrated Circuit Memory

- Logical configuration

- Long column of bytes

- 1<sup>st</sup> address is "0"

- Sometimes thought of as growing down

- Sometimes thought of as growing up

Integrated Circuit Memory

- Even though we may not have stored anything in a specific memory location

- It has a value

- the value is likely random

| ry |        |   |   |   |   |   | • | _ | /  | 8 bits |        |

|----|--------|---|---|---|---|---|---|---|----|--------|--------|

|    | Addr 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1  |        |        |

|    | Addr 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0  |        |        |

|    | Addr 2 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1, |        |        |

|    | Addr 3 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1  |        | 4.0.1  |

|    |        | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0  | 1      | 1 Byte |

|    |        | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1  |        |        |

|    |        | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1  |        |        |

|    |        | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0  | /      |        |

|    |        | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0  | /      |        |

|    |        | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0  | !      |        |

|    |        | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1  |        |        |

|    |        | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0  |        |        |

|    |        | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0  |        |        |

|    |        | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0  |        |        |

- Integrated Circuit Memory

- Write

- Provide Address and Data

- Write (addr 3, 01100110)

- Write (addr 7, 11010000)

- Write (addr 9, 0000000)

- Note: Writing overwrites existing data

| Addr 0 |   |   |   |   |   |   |   |   |

|--------|---|---|---|---|---|---|---|---|

| Addr 1 |   |   |   | 2 | F | 5 |   |   |

| Addr 2 |   |   |   |   |   |   |   |   |

| Addr 3 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

|        |   |   |   |   |   |   |   |   |

|        |   |   |   |   |   |   |   |   |

|        |   |   |   |   |   | 2 |   |   |

|        | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

|        |   |   |   |   |   |   |   |   |

| lata   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|        |   |   |   |   | _ |   |   |   |

|        |   |   |   |   |   |   |   |   |

|        |   |   |   |   |   |   |   |   |

|        |   | 1 |   |   |   |   |   |   |

- Integrated Circuit Memory

- Read

- Provide Address

- Read (addr 3) → 01100110

- Read (addr 7) → 11010000

- Read (addr 8) → ????????

- NOTE: Reading does not destroy the data

| Addr 0<br>Addr 1<br>Addr 2<br>Addr 3 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

|--------------------------------------|---|---|---|---|---|---|---|---|

| ne data                              |   |   | 0 |   |   |   |   |   |

|                                      |   |   |   |   |   |   |   |   |

- Integrated Circuit Memory

- Addresses

- Addresses are NOT part of the memory array

- Addresses are logic circuits to choose which part of the array to read from or write to – decoders determine the location

| Addr 0<br>Addr 1 |   |   |   |   |   |   |   |   |

|------------------|---|---|---|---|---|---|---|---|

| Addr 2<br>Addr 3 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

|                  | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

|                  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|                  |   |   |   |   |   |   |   |   |

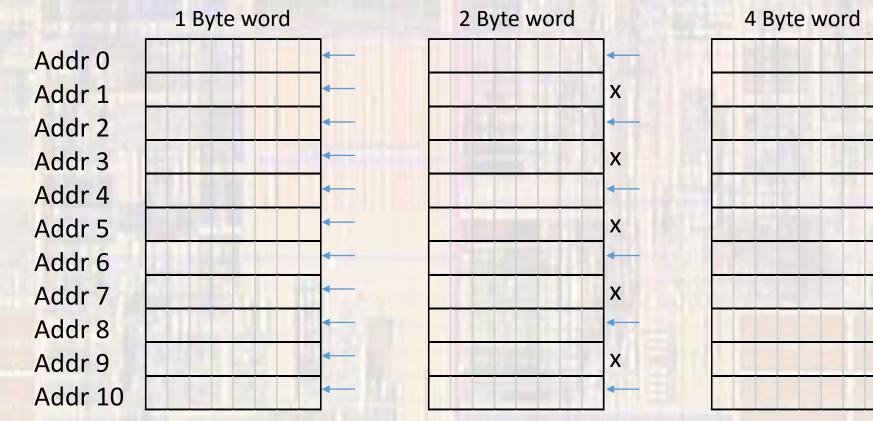

- Integrated Circuit Memory

- Word Alignment

- Processors work with data WORDS

- Size of the internal registers

- 1 Byte 8 bit processor

- 2 Bytes 16 bit processor

- 4 Bytes 32 bit processor

- 8 Bytes 64 bit processor

- Memory is word aligned

- Must access the entire word

- Not allowed/possible to access inside a word\*

\* exceptions exist

- Integrated Circuit Memory

- Word Alignment

- Allowed addresses indicated by

12

X

X

X

X

X

Х

Х

Х

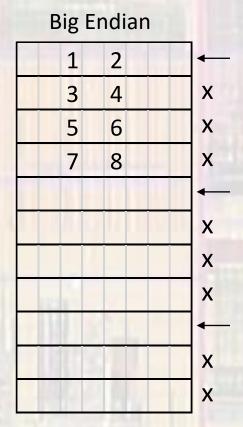

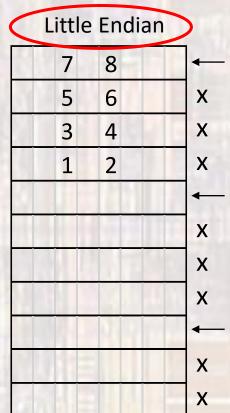

- Integrated Circuit Memory

- Big-Endian vs Little-Endian

- data value 0x12345678 in a 4 byte word

Addr 0 Addr 1 Addr 2 Addr 3 Addr 4 Addr 5 Addr 6 Addr 7 Addr 8 Addr 9 Addr 10

13

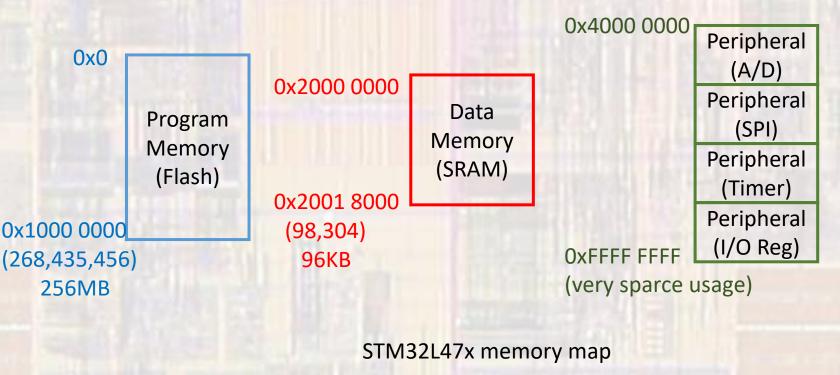

- Memory Mapped Architecture (embedded)

- Treat memories and peripherals the same

- Assign separate memory "spaces" to each type of storage

- Some architectures include registers in memory map

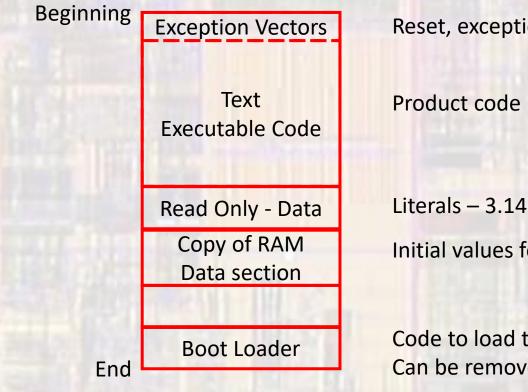

- Program Memory (embedded)

- Flash

- Accessible Double Word format

Reset, exception, and interrupt actions

Literals – 3.14159, 1.414, ...

Initial values for variables

Code to load the remainder of flash Can be removed for additional space in production

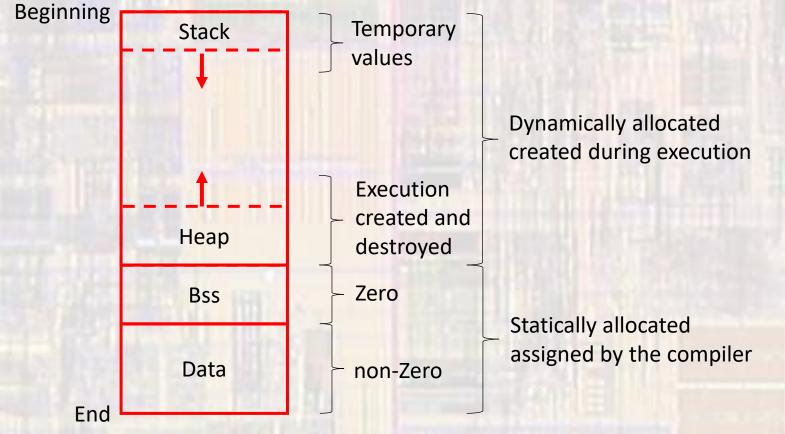

- Data Memory (embedded)

- Accessible in Byte, Half-Word, and Word format

- Has some Bit level access

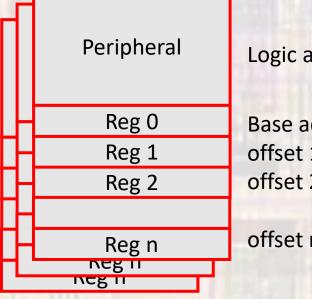

- Peripheral Memory (embedded)

- 4 Bytes (Word) accesses

Logic and other Hardware

Base address (offset 0) offset 1 offset 2

offset n