# Timer A

Last updated 8/7/18

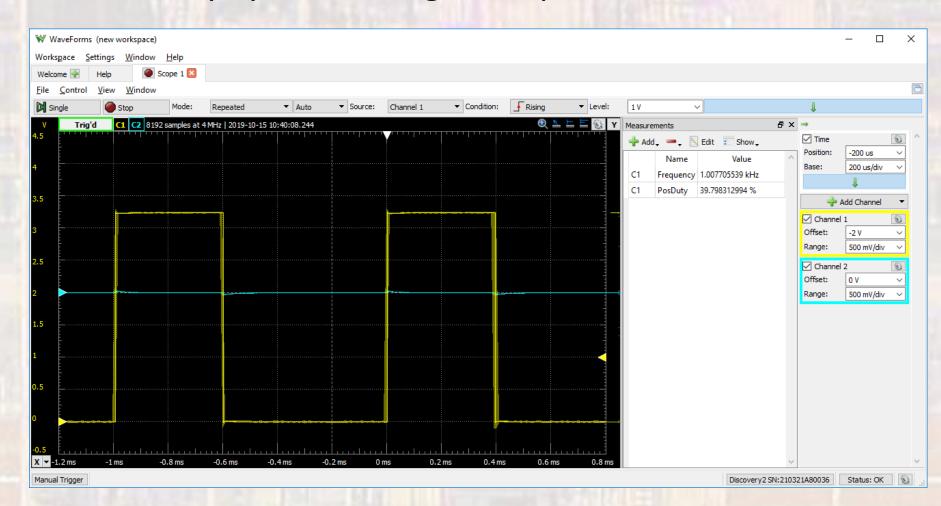

40% duty cycle bit-banged output – method 1

© ti

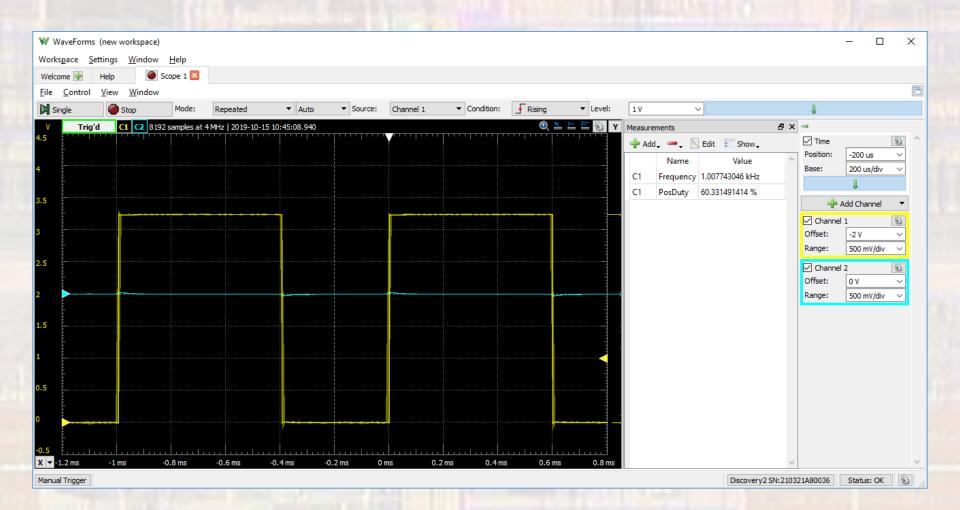

60% duty cycle bit-banged output – method 2

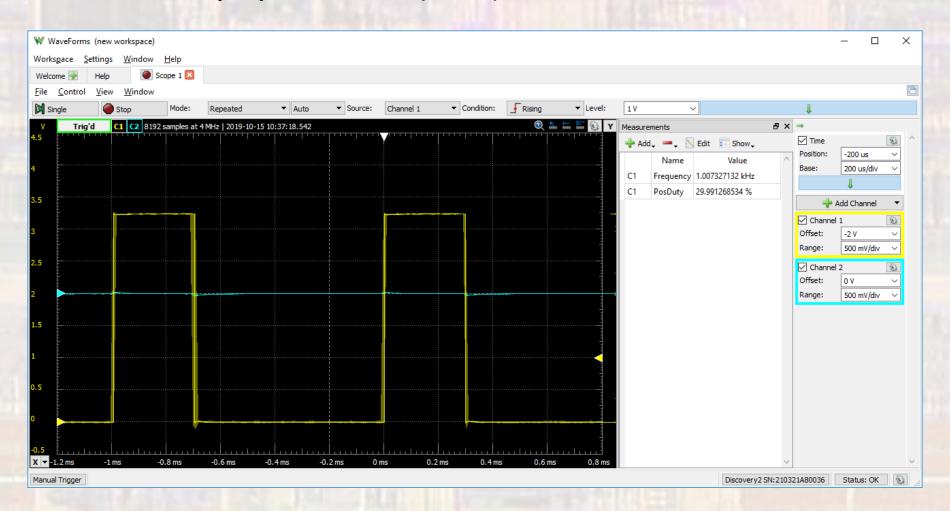

xx% duty cycle PWM (30%)

- Input Capture

- 3MHz/12 clk

- 4us period

- Both edges

- 10KHz input signal

- 100us period

- 50us between edges

- 12.5 clks /edge

- 25 clks every other edge

- Input Capture 2

- 3MHz/12 clk

- 4us period

- Both edges

- 12.5Hz input signal

- 80ms period

- 40ms between edges

- 10000 clks /edge

```

10000 1

10000 0

10001 1

10000

10001 1

10000

10000

10000

10001

trigger signal value

```

clocks between edges

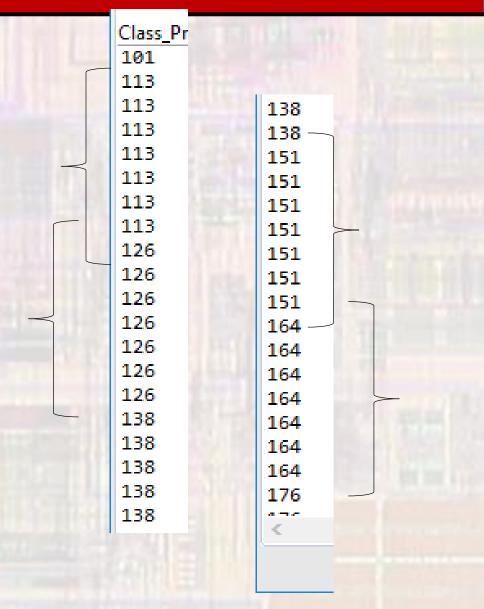

- Clock input example

- 2KHz PWM signal

- Used as clock input to second counter

- Count edges in 5 sec period

```

Class_Project:CIO

Counts in 5 sec = 9993, frequency = 1998Hz

Counts in 5 sec = 9993, frequency = 1998Hz

Counts in 5 sec = 9994, frequency = 1998Hz

Counts in 5 sec = 9994, frequency = 1998Hz

Counts in 5 sec = 9994, frequency = 1998Hz

Counts in 5 sec = 9994, frequency = 1998Hz

Counts in 5 sec = 9993, frequency = 1998Hz

Counts in 5 sec = 9994, frequency = 1998Hz

Counts in 5 sec = 9994, frequency = 1998Hz

```