## EE 3921

Dr. Johnson

## Homework 1

2 – Word Match, Identify the <u>best</u> matching number on the left for each item on the right. (no duplicates) 10pts

| 1  | Analysis and Elaboration | View Schematic                       |

|----|--------------------------|--------------------------------------|

| 2  | Analyze Current File     | State machine schematic/logic        |

| 3  | Analysis and Synthesis   | Creates the physical design          |

| 4  | Start Fitter             | Creates logic                        |

| 5  | Pin Planner              | Allows access to the physical design |

| 6  | RTL Viewer               | Checks for syntax errors             |

| 7  | Signal Tap II            | Debug Tool                           |

| 8  | Model Sim                | Simulates RTL                        |

| 9  | State Machine Viewer     | Creates RTL                          |

| 10 | Chip Planner             | Assign/view pins                     |

3) Given the VHDL code below and the indicated inputs, provide the expected

signal values

```

a=1, b=0, c=0, d=1

e=0110, f=1001

g=0111, h=1110

```

i= aa=

j= bb=

b=

q= ee=

r= ff=

S=

gg= u=

hh=

**V**=

```

30pts

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.NUMERIC_STD.all;

-- IGNORING NAMING CONVENTION --

Jentity arithHW is

generic( NNN: INTEGER := 4);

port ( a,b,c,d:

in STD_LOGIC;

e,f,g,h:

i,j,k,l:

in STD_LOGIC_VECTOR(NNN-1 downto 0);

out STD_LOGIC;

out STD_LOGIC_VECTOR(NNN-1 downto 0);

out STD_LOGIC_VECTOR(2*NNN-1 downto 0);

o,p,z:

foo:

out std_logic_vector(65 downto 0)

end entity;

Architecture behavioral of arithHW is

SIGNED((NNN-1) downto 0);

signal q,r,s,t,u,v:

signal aa,bb,cc,dd,ee,ff: UNSIGNED((NNN-1) downto 0); signal gg: SIGNED((2*NNN-1) downto 0);

UNSIGNED((2*NNN-1) downto 0):

signal hh:

begin

q <= SIGNED(f);</pre>

r <= SIGNED(g);

aa <= UNSIGNED(f);

bb <= UNSIGNED(g);</pre>

i \leftarrow ((a \text{ or } b) \text{ and } c) \text{ xor } d;

j \le a \text{ and } (e(1) \text{ or } e(2));

s \ll q + r;

gg <= q * r;

u \ll q / r;

v \ll q \mod r;

cc <= aa + bb;

hh <= aa * bb;

ee <= aa / bb;

ff <= aa mod bb;

p <= ('1' & h(2) & "00" & g(3 downto 1) & '1');

end architecture;

```

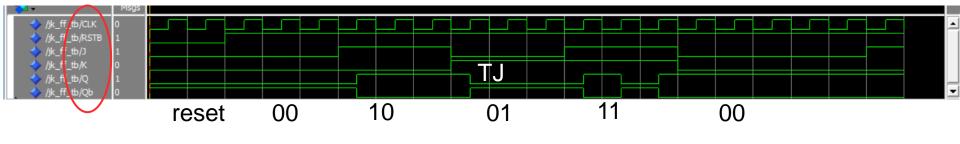

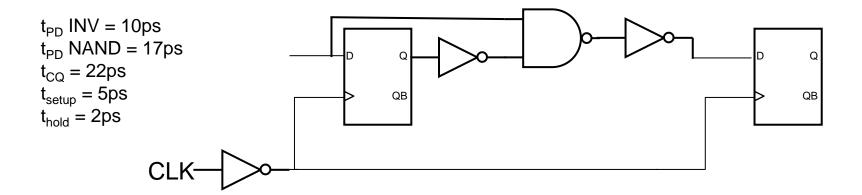

4 – Write your own behavioral VHDL code for a JK Flip-Flop Provide code and a simulation

40pts