## EE 3921

Dr. Johnson

## Homework 6

1 – FF Based memory: Modify the design from class (Max10 Memory HDL notes – page 6) to create a 128 word, 40 bit memory. Write down every line of code that must be modified. Compile your design and include the compilation report / flow summary with the number of LE's highlighted. 10pts

generic( REG\_NUM: natural := 128; REG\_DATA\_WIDTH: natural := 40

| •                                  |                                             |

|------------------------------------|---------------------------------------------|

| Flow Status                        | Successful - Tue Sep 21 11:40:06 2021       |

| Quartus Prime Version              | 18.1.0 Build 625 09/12/2018 SJ Lite Edition |

| Revision Name                      | hw6                                         |

| Top-level Entity Name              | reg_file_nbit_by_m_hw6                      |

| Family                             | MAX 10                                      |

| Device                             | 10M50DAF484C7G                              |

| Timing Models                      | Final                                       |

| Total logic elements               | 8,672                                       |

| Total registers                    | 5120                                        |

| Total pins                         | 97                                          |

| Total virtual pins                 | 0                                           |

| Total memory bits                  | 0                                           |

| Embedded Multiplier 9-bit elements | 0                                           |

| Total PLLs                         | 0                                           |

| UFM blocks                         | 0                                           |

| ADC blocks                         | 0                                           |

|                                    |                                             |

2A – How many onboard memory blocks would be required to support the same size memory as the previous problem? 10pts

128 x 40 = 5120 < one M9K block

2B – What is the largest size 32bit word memory that can fit in a single on chip memory block? 10pts

M9K has extra 1K bits attached to the word width, not the # of words  $\rightarrow$  8Kb  $\rightarrow$  1KB  $\rightarrow$  256W in x32 configuration

| Feature                        | M9K Block       |                                                                                                                  |

|--------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------|

|                                | 8192 × 1        | Constant of the second                                                                                           |

|                                | 4096 × 2        |                                                                                                                  |

|                                | 2048 × 4        |                                                                                                                  |

|                                | $1024 \times 8$ | LATIN BEEN STONETER                                                                                              |

| Configurations (depth × width) | 1024×9 ◄        | Parity used as memory                                                                                            |

|                                | 512 × 16        | /                                                                                                                |

|                                | 512×18          |                                                                                                                  |

|                                | 256 × 32        | - I MALE MARKED AND AND AND AND AND AND AND AND AND AN                                                           |

|                                | 256 × 36        | Te se de la contra de |

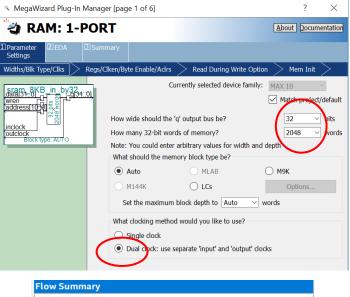

## 3 – Implement a dual clock 8KB SRAM in by-32 configuration using the Mega Wizard 50pts

Compile your HDL and provide the code showing the address/data widths and clocks Provide the compilation summary showing the number of memory bits used

```

-- sram_8KB_in_by32_mega.vhdl

-- created 4/25/17

-- tj

___

-- rev 0

_____

-- 8KB in x32 dq RAM from mega library

-- Inputs: clk, addr, data_in, we_b

-- Outputs: data_out

library ieee;

use ieee std_logic_1164 all;

use ieee.numeric_std.all;

entity sram_8KB_in_by32_mega is

port(

i_clk_in: in std_logic;

i_clk_out: in std_logic;

i_we_b: in std_logic;

in std_logic_vector(10 downto 0);

i_addr:

i_data_in: in std_logic_vector(31 downto 0);

o_data_out: out std_logic_vector(31 downto 0)

);

end:

architecture behavioral of sram_8KB_in_by32_mega is

-- invert we

signal we_sig: std_logic;

component SRAM_8KB_in_by32

PORT

address

: IN STD_LOGIC_VECTOR (10 DOWNTO 0);

data : IN STD_LOGIC_VECTOR (31 DOWNTO 0);

inclock : IN STD_LOGIC := '1';

outclock : IN STD_LOGIC ;

wren : IN STD_LOGIC ;

: OUT STD_LOGIC_VECTOR (31 DOWNTO 0)

q

):

end component;

begin

we_sig <= not i_we_b;</pre>

SRAM_8KB_in_by32_inst : SRAM_8KB_in_by32

PORT MAP (

address

=> i_addr,

=> i_data_in,

data

inclock

=> i_clk_in,

=> i_clk_out,

outclock

wren

=> we_sig,

=> o_data_out

a

):

end behavioral:

```

| Flow Summary                       |                              |

|------------------------------------|------------------------------|

| < <filter>&gt;</filter>            |                              |

| Flow Status                        | Successful - Fri Jun 26 11:5 |

| Quartus Prime Version              | 18.1.0 Build 625 09/12/20    |

| Revision Name                      | hw6                          |

| Top-level Entity Name              | sram_8KB_in_by32_mega        |

| Family                             | MAX 10                       |

| Device                             | 10M50DAF484C7G               |

| Timing Models                      | Final                        |

| Total logic elements               | 1 / 49,760 ( < 1 % )         |

| Total registers                    | 0                            |

| Total pins                         | 78 / 360 ( 22 % )            |

| Total virtual pins                 | 0                            |

| Total memory bits 🤇                | 65,536 / 1,677,312 ( 4 % )   |

| Embedded Multiplier 9-bit elements | 0/288(0%)                    |

| Total PLLs                         | 0/4(0%)                      |

| UFM blocks                         | 0/1(0%)                      |

| ADC blocks                         | 0/2(0%)                      |

|                                    |                              |

4 – Simple single port memory: Given the timing diagram below for the simple single port memory, fill in the values for the empty boxes on the diagram and the final memory values. Assume a new data output model 20pts Clock WR Enable Address A5 A6 Α7 A2 A6 Α7 Α3 A4 A0 A1 Α3 A4 A5 0x11 0x22 0x33 0x44 0xAA 0xBB 0xCC Data In х х Х х х х 0x11 0x22 0x33 (<mark>0x4</mark>4 Dx1A Q out Synchronous Mem Hex Mem Hex AFTER **BEFORE 0x1A A0** 0x1A 0x1B 0x1B A1 0x1C A2 0x1C 0x11 A3 0x1D 0x22 A4 0x1E 0xAA A5 0x1F 0xBB A6 0x10 0xCC 0x21 Α7