# EE 3921 Lab 3: VGA

2 dedicated lab periods, 3 lab periods to complete

| Name: | 1 |  |  |  |

|-------|---|--|--|--|

|       |   |  |  |  |

-4...

## **Objectives**

- Utilize Max 10 mega-functions

- Utilize third party IP

- Drive an external component (VGA)

|        |                            | student   |  |  |

|--------|----------------------------|-----------|--|--|

| Prelal | b                          | check off |  |  |

| •      | Review the ROM Mega Wizard |           |  |  |

| •      | Review the VGA class notes |           |  |  |

| •      | Review the VGA driver code |           |  |  |

## **Assignment**

Part 1: Create a ROM verification block

## Specifications:

- 1) The ROM will be configured as a Single-Port ROM

- 2) The ROM will have 256, 8 bit words

- 3) The rom will be initialized from a file

- 4) The clock will cycle through the ROM, one word per clock cycle

- 5) The cycling can be paused

- 6) Generics:

- a. none

- 7) Input signals:

- a. rstb

- b. clk

- c. pauseb (active low)

- 8) Output signals:

- a. Current ROM address

- b. ROM contents (1 word)

#### Additional Requirements:

- 1) Create the ROM using the Mega Wizard

- 2) Use the Alpha1.mif from the website for the contents of the ROM

- 3) Put the current address value on the LEDs on the DE10 (binary)

- 4) Put the ROM data on the seven segment displays in HEX on the DE10

- 5) Use one of the pushbutton switches as the pauseb signal

- 6) Operate the DE10 implementation with a 2Hz clock

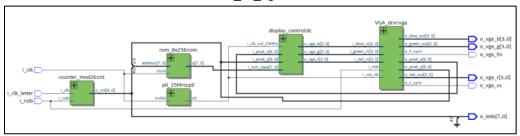

# Part 2: Create a VGA display block using the instructor provided VGA driver Specifications:

- 1) The display block will utilize an internal character ROM

- The design will run on two external clocks (one for the VGA, one for the Character Driver)

- 3) The design will output 1 character every second

- 4) The design will output each character to the same location

- 5) Input signals:

- a. clk

- b. rstb

- c. clk\_char (clock for advancing the character number)

- 6) Output Signals:

- a. Character number (binary)

- b. VGA signals

#### Additional requirements:

- 1) Implement the DE10 version using the ROM and Alpha1.mif file from Part 1

- 2) Output 26 characters in an infinite loop

- 3) The VGA driver block must use a PLL for its clock

- 4) Use a VGA monitor (available in the tech-center) for displaying your VGA output

- 5) Output the current character count to the LEDs

Note: The ROM contains all the pixel information for the capital letters of the alphabet, plus a space. The information for each character is stored as eight 8-bit bytes, where each byte contains the bit pattern for a single row of that character. Each character is represented as a matrix of pixels 8-by-8. A '1' bit means the pixel is turned on, a '0' means it is off.

The VGA driver is available on the website. Read its documentation to determine the required clock frequency and the I/O signals.

#### Part 3: Express yourself - choose one of the following

- 1) Instead of cycling through the characters, display some non-offensive message of your choice on the first line of the monitor. Use somewhere between 20 and 79 characters

- 2) Modify your design to select the location of the character using switches

- 3) Modify your design to select the color of the character using switches

#### **Check Off**

You must demonstrate your working design(s) prior to the end of the 2nd lab period

| Tod mast demonstrate your working design(s) prior to the end of the             | Zila lab perioa |

|---------------------------------------------------------------------------------|-----------------|

| <ul> <li>Demo the ROM verification design (Simulation, DE10)</li> </ul>         | 30%             |

| <ul> <li>Demo your VGA character design (DE10 implementation)</li> </ul>        | 50%             |

| Demo your part 3 selection (DE10 implementation)                                | 10%             |

| Lab Report (informal)                                                           |                 |

| <ul> <li>Due at 4:00 pm. 1 day after 3<sup>nd</sup> lab – in the box</li> </ul> |                 |

| <ul> <li>Due at 4:00 pm, 1 day after 3<sup>nd</sup> lab – in the box</li> </ul> |                 |

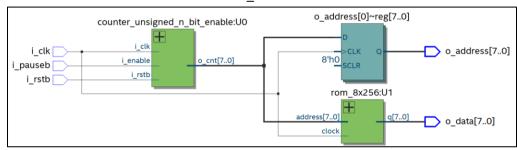

# $rom\_ver.vhdl$

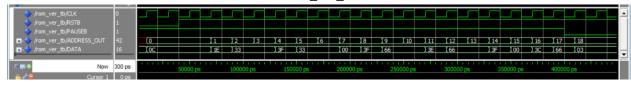

### rom\_ver\_tb

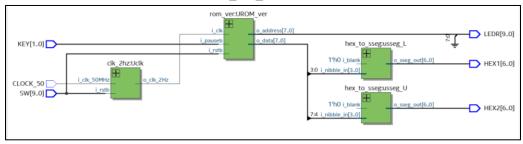

## rom\_ver\_de10.vhdl

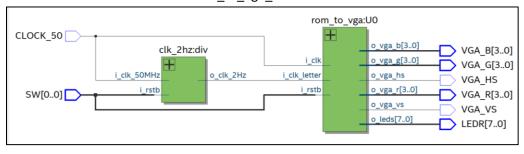

## rom\_to\_vga.vhdl

## rom\_to\_vga\_de10.vhdl