# MAX 10 - ADC

# Last updated 6/3/20

#### These slides review the configuration of an MAX10 ADC

Upon completion: You should be able to describe and operation of the MAX10 ADC module

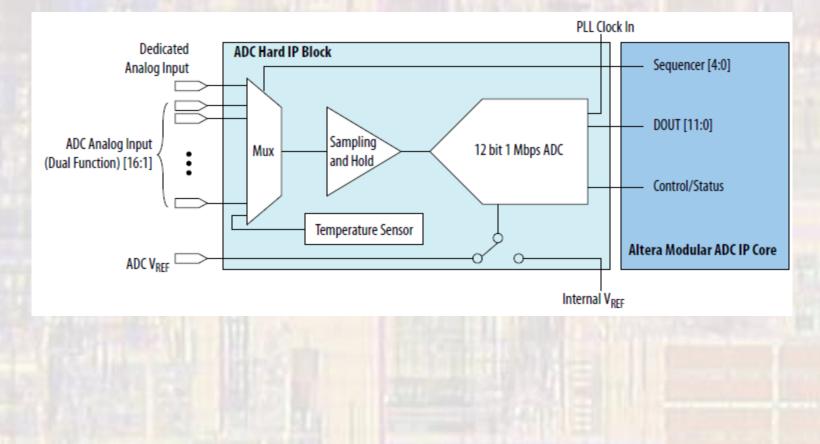

- ADC Configuration

- 2 ADC channels

- SAR type conversion

- 12 bit conversion

- 1MHz (max) operation

- 1 dedicated input / channel

- 8 programmable inputs / channel

- 0 2.5V conversion range

ADC Configuration

ADC Configuration

- ADC Configuration

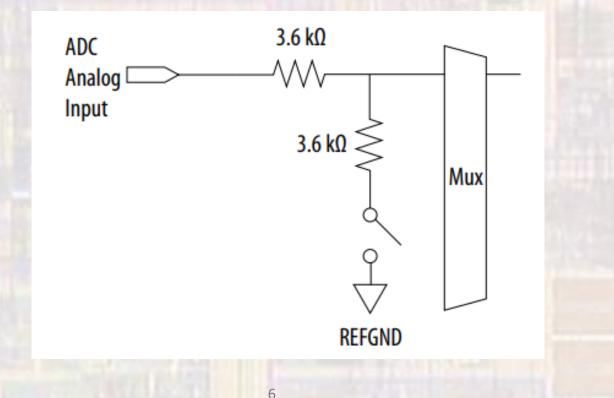

- Special Pre-scaler mode for Channel 8

- Divides input voltage by 2

- Allows input voltages up to 5V with a 2.5V reference

- ADC Configuration

- Clocking

- Must use PLL for clocking

- PLL1 or PLL3

- Voltage Reference

- Internal and external reference options

- Common external reference pin

- Common internal reference

- Can select references separately for each ADC

- Temperature Sensor

- ADC1 has an on-die temperature sensor

© tj

- ADC Configuration

- 2 ADC IP Cores

- Altera Modular ADC IP core

- Can use either ADC

- Both cores can be used at the same time

- If both cores used they will operate asynchronously

- Altera Modular Dual ADC IP core

- Instantiates both cores

- ANAIN1 and ANAIN2 inputs are sampled synchronously

- All other pins are asynchronous

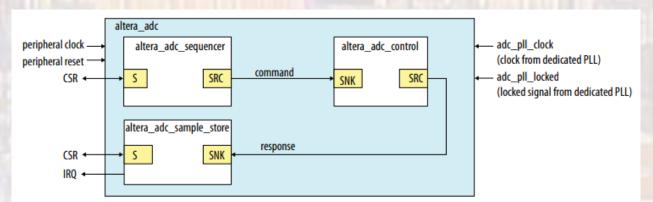

- ADC Configuration

- 4 Configurations for each core

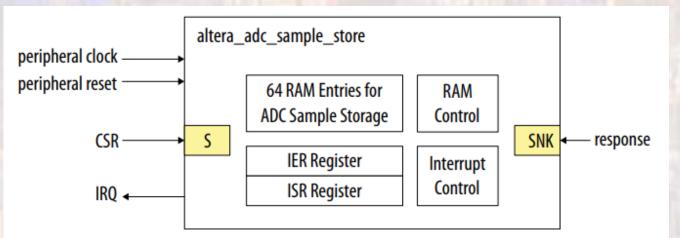

- Standard Sequencer with Avalon-MM Sample Storage

- Sequencer manages multiple input pins and sequencing of samples

- Samples are stored in on-chip memory (Sample Store)

- Control controls the process

- Managed by processor

- ADC Configuration

- 4 Configurations for each core

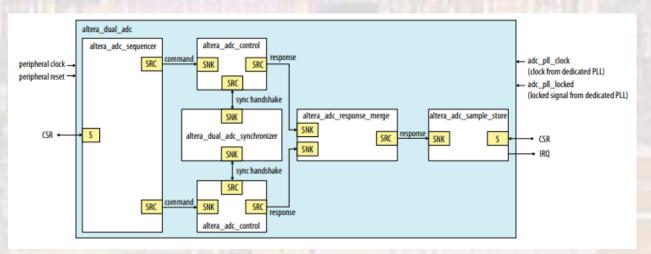

- Standard Sequencer with Avalon-MM Sample Storage Dual Core

- Sequencer manages multiple input pins and sequencing of samples

- Merged samples are stored in on-chip memory (Sample Store)

- Control controls the process independently

- Managed by processor

- ADC Configuration

- 4 Configurations for each core

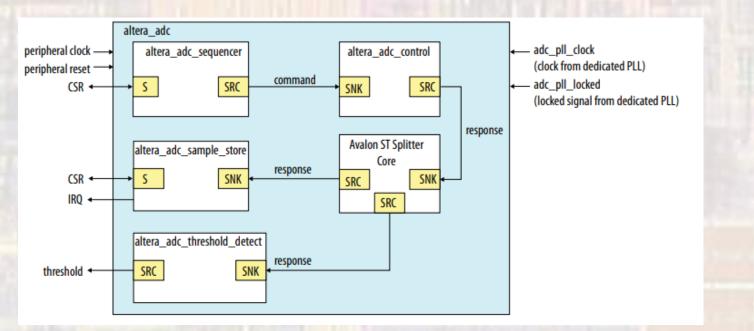

- Standard Sequencer with Avalon-MM Sample Storage and Threshold Violation Detection

- Adds a splitter

- Compares values to thresholds and provides a violation signal

- ADC Configuration

- 4 Configurations for each core

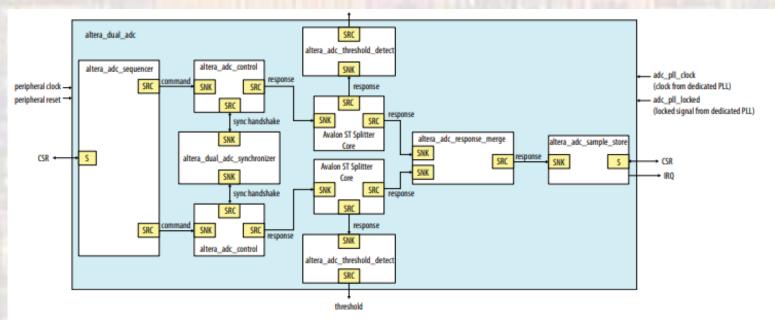

- Standard Sequencer with Avalon-MM Sample Storage and Threshold Violation Detection – Dual Core

- Adds a splitter

- Compares values to thresholds and provides a violation signal

- ADC Configuration

- 4 Configurations for each core

- Standard Sequencer with External Sample Storage

- Sequencer manages multiple input pins and sequencing of samples

- Control controls the process

- Managed by processor

- Samples are stored outside the IP core

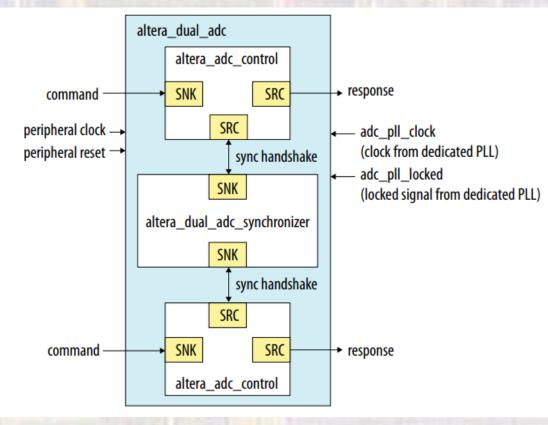

- ADC Configuration

- 4 Configurations for each core

- Standard Sequencer with External Sample Storage Dual Core

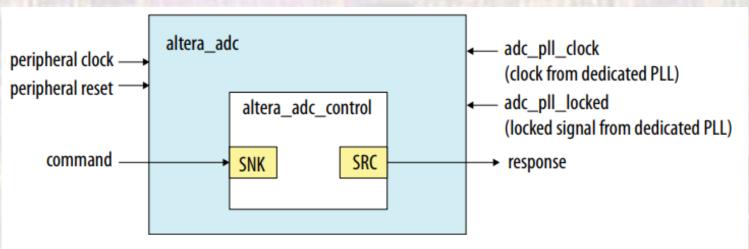

- ADC Configuration

- 4 Configurations for each core

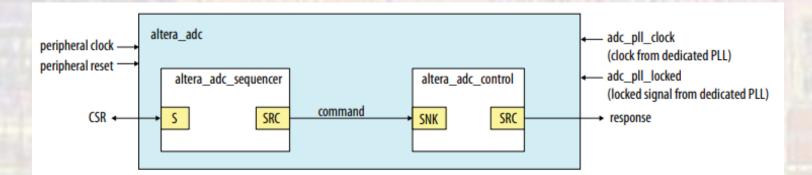

- ADC Control Core Only

- Control controls the process

- Managed by processor

- No Sequencer

- Samples are stored outside the IP core

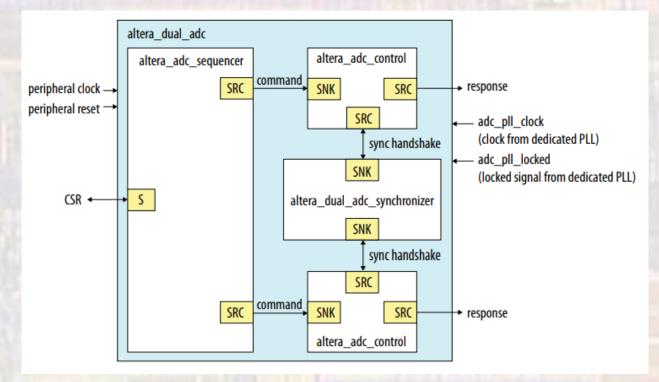

- ADC Configuration

- 4 Configurations for each core

- ADC Control Core Only Dual Core

- ADC Configuration

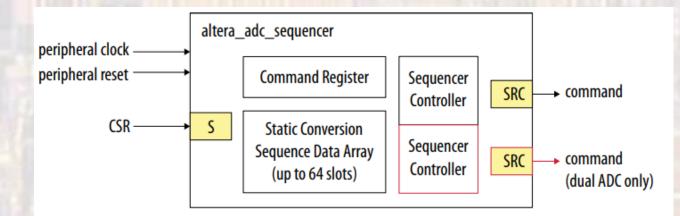

- Configuration Blocks

- ADC Configuration

- Configuration Blocks

- ADC Configuration

- 3 approaches to using the ADCs

- Used as part of a NIOS system

- Avalon interface built in by Platform Designer

- Used with a hand built interface

- Emulate the Avalon interface

- Used with the Quartus ToolKit (Inside System Console) to verify operation

- Avalon interface built into the toolkit

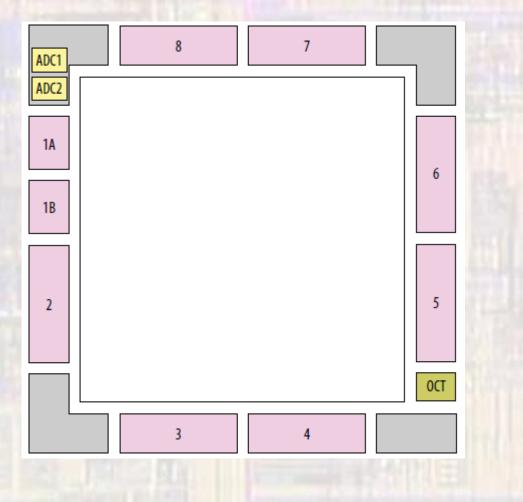

- DE10-Lite ADC WARNINGS

- Only ADC1 is brought out to pins

- No access to ADC2 inputs

- The pin #s are shifted

...

- Arduino A0 is mapped to ADC1\_in1

- Arduino A5 is mapped to ADC1\_in6

- No other ADC inputs are pinned out