Last updated 5/19/20

These slides review HDL implementation of memory in the MAX10 environment

Upon completion: You should be able to design register based, inferred and IP based HDL memories on the MAX10 platform

- Three types of MAX10 Memory

- FF based memory using the LEs

- Most efficient for very small memories

- Compiler driven

- M9K Fixed Memory Blocks

- Embedded SRAM block

- 8K bits + 1024 parity bits (9216b)

- MAX 10-M50 has 182 blocks

- 1,456Kb + parity = 1,677,312b total

- User Flash

- User Programmable 5,888Kb

- Configuration 10,752Kb

Three ways to implement memory

FF based memory embedded in the LEs

Inferred Memory

```

-- SRAM write process

--

process(i_clk)

begin

if (rising_edge(i_clk)) then

-- read logic

if(i_we_b = '0') then

mysRAM(to_integer(unsigned(i_addr))) <= i_data_in;

end if;

end process;

--

SRAM asynchronous read

--

o_data_out <= mysRAM(to_integer(unsigned(i_addr)));

```

```

--

-- SRAM write process

--

-- SRAM write process

--

process (i_clk)

begin

if (rising_edge(i_clk)) then

-- read logic

if(i_we_b ='0') then

mySRAM(to_integer(unsigned(i_addr))) <= i_data_in;

end if;

--registered output

o_data_out <= mySRAM(to_integer(unsigned(i_addr)));

end if;

end process;

```

IP blocks

- FF based memory embedded in the LEs

- Simple memory

- Static

- N bits wide

- M bits deep

- Synchronous write

- Inefficient for all but the smallest memories

FF based memory embedded in the LEs

```

architecture behavioral of sram_regbased is

-- create type

type sram_type is array (0 to (mem_depth - 1)) of std_logic_vector ((mem_width - 1) downto 0);

-- sram_regbased.vhdl

-- create memory

-- created 4/25/17

-- tj

signal mySRAM: sram_type;

begin

-- rev 0

-- SRAM write process

-- synchronous RAM built with registers

process(i_clk)

if (rising_edge(i_clk)) then

-- Inputs: clk, addr, we_b, data_in

-- write logic

-- Outputs: data_out

if(i_we_b = 0) then

mySRAM(to_integer(unsigned(i_addr))) <= i_data_in;

end if:

library ieee;

end if;

use ieee.std_logic_1164.all;

end process;

use ieee.numeric_std.all;

use ieee math_real.all;

-- SRAM asynchronous read

entity sram_regbased is

generic(

o_data_out <= mySRAM(to_integer(unsigned(i_addr)));</pre>

mem_width: positive := 32;

mem_depth: positive := 64

end behavioral:

);

port(

i_clk:

std_logic;

i_we_b:

in std_logic;

in std_logic_vector(((integer(ceil(log2(real(mem_depth))))) - 1) downto 0);

i_addr:

i_data_in: in std_logic_vector((mem_width - 1) downto 0);

o_data_out: out std_logic_vector((mem_width - 1) downto 0)

end entity:

```

• FF based memory embedded in the LEs 64 x 32b 256 x 36b

| Flow Status                        | Successful - Wed Aug 05 1 |

|------------------------------------|---------------------------|

| Quartus Prime Version              | 18.1.0 Build 625 09/12/20 |

| Revision Name                      | Class_Examples            |

| Top-level Entity Name              | sram_regbased             |

| Family                             | MAX 10                    |

| Device                             | 10M50DAF484C7G            |

| Timing Models                      | Final                     |

| Total logic elements               | 2,449 (49,760 (5%)        |

| Total registers                    | 2048                      |

| Total pins                         | 72/360 (20%)              |

| Total virtual pins                 | 0                         |

| Total memory bits                  | 0 / 1,677,312 ( 0 % )     |

| Embedded Multiplier 9-bit elements | 0/288(0%)                 |

| Total PLLs                         | 0/4(0%)                   |

| UFM blocks                         | 0/1(0%)                   |

| ADC blocks                         | 0/2(0%)                   |

| Flow Status                        | In progress - Wed Aug 05  |

|------------------------------------|---------------------------|

| Quartus Prime Version              | 18.1.0 Build 625 09/12/20 |

| Revision Name                      | Class_Examples            |

| Top-level Entity Name              | sram_regbased             |

| Family                             | MAX 10                    |

| Device                             | 10M50DAF484C7G            |

| Timing Models                      | Final                     |

| Total logic elements               | 10,981 / 49,760 (22 %)    |

| Total registers                    | 9216                      |

| Total pins                         | 82/360(23%)               |

| Total virtual pins                 | 0                         |

| Total memory bits                  | 0 / 1,677,312 ( 0 % )     |

| Embedded Multiplier 9-bit elements | 0/288(0%)                 |

| Total PLLs                         | 0/4(0%)                   |

| UFM blocks                         | 0/1(0%)                   |

| ADC blocks                         | 0/2(0%)                   |

|                                    |                           |

Equivalent to one M9K block

- M9K Fixed Memory Blocks

- Functional configurations

- Single-port

- Simple dual-port

- True dual-port (bidirectional dual-port)

- Shift register

- ROM

- FIFO buffers

- Memory Based Multiplier

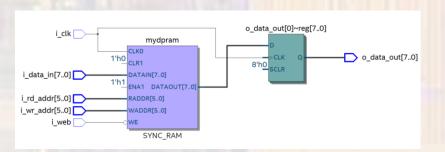

- Inferred Simple Dual-Port RAM

- Basic RAM

- Separate read and write address inputs

- Provides the old data if reading and writing to the same address (no write-through)

- Inputs and outputs registered

- To be inferred

- All input ports must be registered

- rd addr, wr addr, web, data in

- Output port must be registered

Inferred - Simple Dual-Port RAM

```

-- ram_dualport_simple.vhdl

architecture behavioral of ram_dualport_simple is

-- created 7/19/17

type ram_dp is array((2**ADDR_WIDTH-1) downto 0) of signed((DATA_WIDTH-1) downto 0);

-- tj

signal mydpram : ram_dp;

-- rev 0

begin

mem: process(i_clk)

-- Dual port RAM

begin

if(rising_edge(i_clk)) then

if(i_web = '0') then

-- Inputs: clk, read addr, write addr, da

mydpram(to_integer(unsigned(i_wr_addr))) <= signed(i_data_in);</pre>

-- Outputs: data_out

end if:

-- Return old value when read and write access the same address

library ieee;

o_data_out <= std_logic_vector(mydpram(to_integer(unsigned(i_rd_addr))));</pre>

use ieée.std_logic_1164.all;

end if:

use ieee.numeric_std.all;

end process;

entity ram_dualport_simple is

end architecture;

generic(

DATA_WIDTH : natural := 8;

ADDR_WIDTH : natural := 6

port(

i clk

: in std_logic;

: in std_logic_vector((2**ADDR_WIDTH - 1) downto 0);

i_rd_addr

: in std_logic_vector((2**ADDR_WIDTH - 1) downto 0);

i_wr_addr

i_data_in

: in std_logic_vector((DATA_WIDTH-1) downto 0);

i_web

: in std_loaic:

o_data_out : out std_logic_vector((DATA_WIDTH -1) downto 0)

end entity;

```

Inferred - Simple Dual-Port RAM

| Flow Summary                       |                               |

|------------------------------------|-------------------------------|

| < <filter>&gt;</filter>            |                               |

| Flow Status                        | Successful - Tue May 19 14:49 |

| Quartus Prime Version              | 19.1.0 Build 670 09/22/2019   |

| Revision Name                      | Class_Examples                |

| Top-level Entity Name              | ram_dualport_simple           |

| Family                             | MAX 10                        |

| Device                             | 10M50DAF484C7G                |

| Timing Models                      | Final                         |

| Total logic elements               | 0                             |

| Total registers                    | 0                             |

| Total pins                         | 30                            |

| Total virtual pins                 | 0                             |

| Total memory bits                  | 512                           |

| Embedded Multiplier 9-bit elements | 0                             |

| Total PLLs                         | 0                             |

| UFM blocks                         | 0                             |

| ADC blocks                         | 0                             |

|                                    |                               |

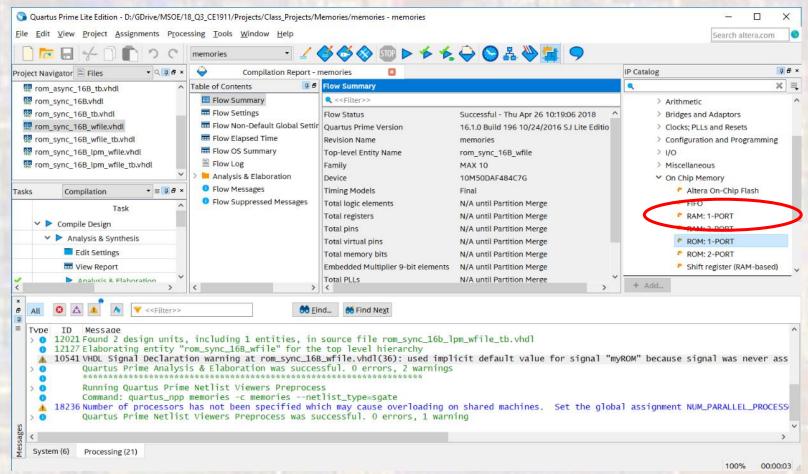

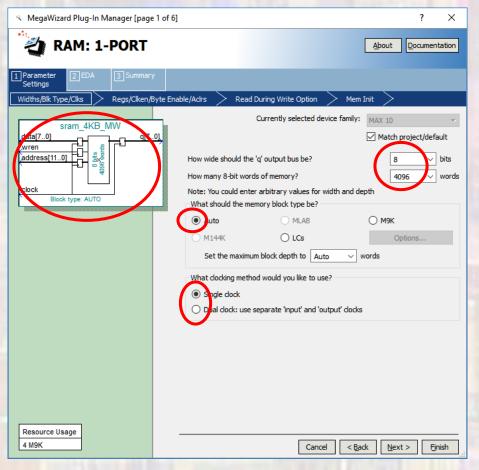

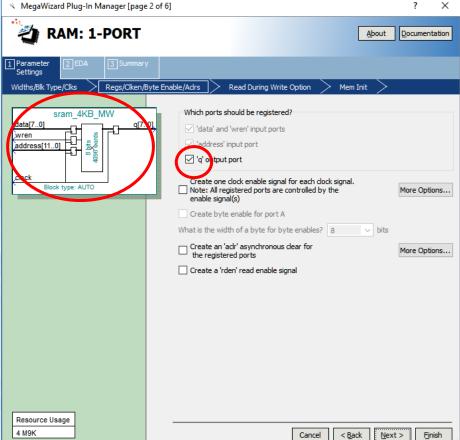

- IP Based RAM

- Quartus has a series of pre-defined blocks

- They can be created in Quartus MegaWizard

- They need to be instantiated in our design

- IP Based RAM

- MegaWizard process

© ti

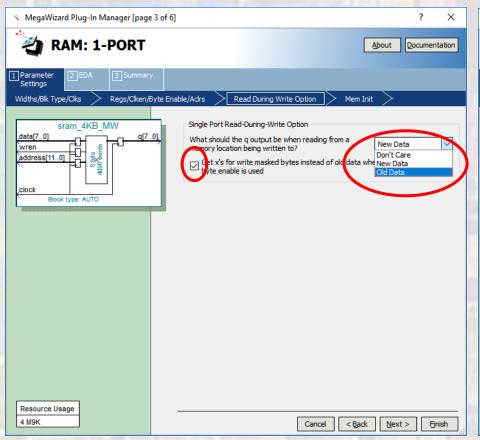

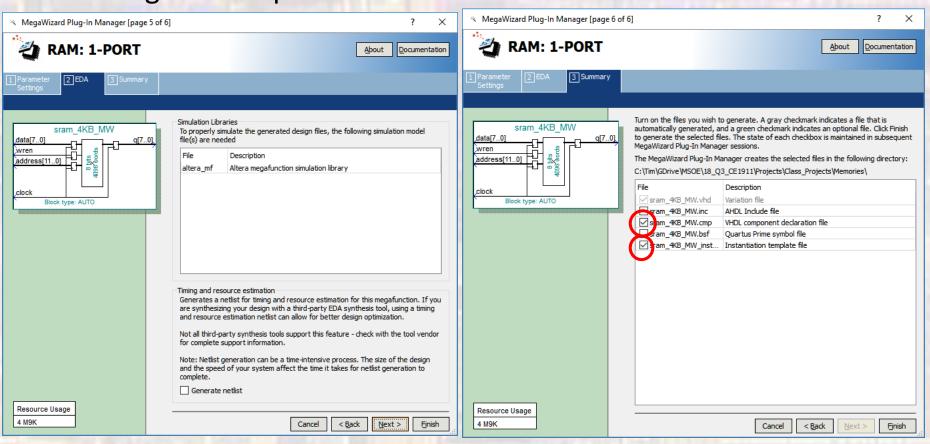

- IP Based RAM

- MegaWizard process

- IP Based RAM

- MegaWizard process

- IP Based RAM

- MegaWizard process

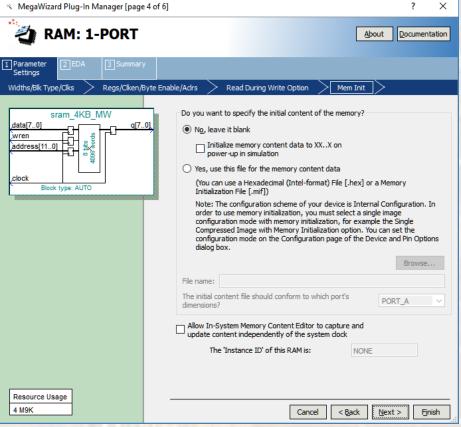

- IP Based RAM

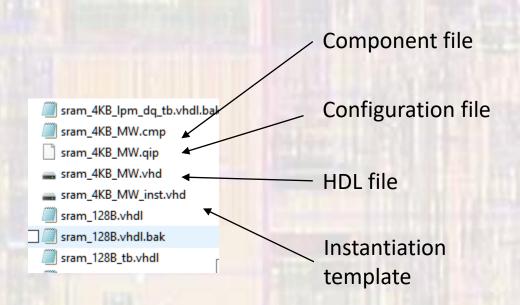

- MegaWizard files

- IP Based RAM

- MegaWizard files

#### HDL file

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY altera mf;

USE altera mf.altera mf components.all;

ENTITY sram 4KB MW IS

PORT

: IN STD LOGIC VECTOR (11 DOWNTO 0);

address

clock

: IN STD LOGIC := '1';

: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

data

: IN STD LOGIC;

wren

: OUT STD LOGIC VECTOR (7 DOWNTO 0)

q

END sram 4KB MW;

ARCHITECTURE SYN OF sram 4kb mw IS

SIGNAL sub wire0 : STD LOGIC VECTOR (7 DOWNTO 0);

```

```

BEGIN

q <= sub_wire0(7 DOWNTO 0);</pre>

altsyncram_component : altsyncram

GENERIC MAP (

clock enable input a => "BYPASS",

clock enable output a => "BYPASS",

intended device family => "MAX 10",

lpm hint => "ENABLE RUNTIME MOD=NO",

lpm type => "altsyncram",

numwords a => 4096,

operation mode => "SINGLE PORT",

outdata aclr a => "NONE",

outdata reg a => "CLOCKO",

power up uninitialized => "FALSE",

read during write mode port a =>

"NEW DATA NO NBE READ",

widthad a \Rightarrow 12,

width_a \Rightarrow 8,

width byteena a => 1

PORT MAP (

address a => address,

clock0 => clock,

data a => data,

wren a => wren,

q_a => sub_wire0

END SYN;

```

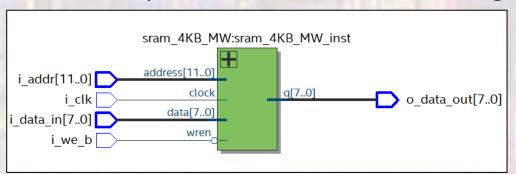

- IP Based RAM

- MegaWizard files

#### Component file

```

component sram_4KB_MW

PORT

(

address : IN STD_LOGIC_VECTOR (11 DOWNTO 0);

clock : IN STD_LOGIC := '1';

data : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

wren : IN STD_LOGIC;

q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

);

end component;

```

#### Instantiation template

```

sram_4KB_MW_inst:sram_4KB_MW PORT MAP (

address => address_sig,

clock => clock_sig,

data => data_sig,

wren => wren_sig,

q => q_sig

);

```

- IP Based RAM

- Implementation into our design

```

-- sram_4KB_MW_ex.vhdl

- created 4/25/17

-- rev 0

-- 4KB SRAM from MegaWizard

-- Inputs: clk, addr

-- Outputs: data

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity sram_4KB_MW_ex is

port(

i_addr : IN STD_LOGIC_'

i_clk : IN STD_LOGIC;

: IN STD_LOGIC_VECTOR (11 DOWNTO 0);

i_data_in : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

i_we_b : IN STD_LOGIC;

o_data_out : OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

```

```

architecture behavioral of sram_4KB_MW_ex is

-- we signal

signal we: std_logic;

component sram_4KB_MW

PORT

address : IN STD_LOGIC_VECTOR (11 DOWNTO 0);

clock : IN STD_LOGIC := '1';

data : IN STD_LOGIC_VECTOR (7 DOWNTO 0);

wren : IN STD_LOGIC ;

: OUT STD_LOGIC_VECTOR (7 DOWNTO 0)

end component;

begin

-- we_b mapping

we <= not i_we_b;

sram_4KB_MW_inst : sram_4KB_MW PORT MAP (

address => i_addr,

clock

=> i_clk.

data

=> i_data_in,

=> we,

wren

=> o_data_out

);

-- Output logic

end behavioral;

```

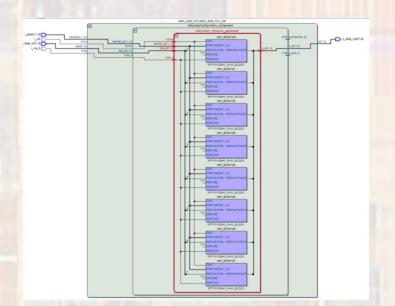

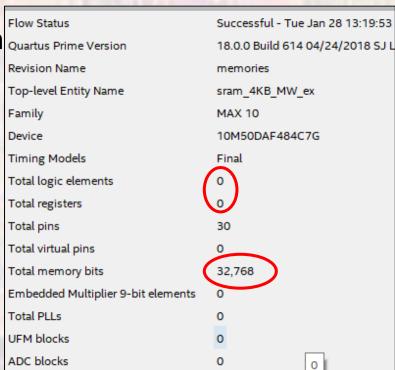

- IP Based RAM

- Implementation into our design Quartus Prime Version

8 – ½ M9K blocks (1 word bit / block)