## NIOS Intro

Last updated 10/12/20

#### **NIOS Basic**

These slides describe the development of a simple NIOS Processor

Upon completion: You should be able implement your own NIOS processor and write code for it

#### NIOS

- NIOS II Embedded Design Suite

- Configurable Processor

- Selection of Peripherals

- Eclipse based Board Support Package (BSP) for SW development

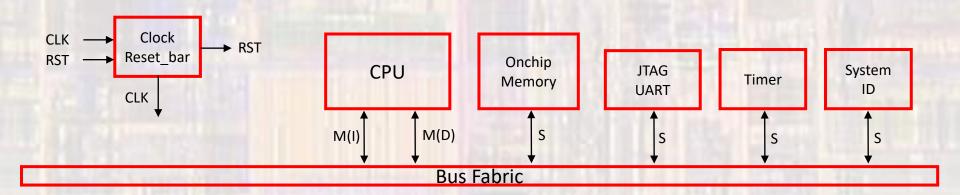

- Basic NIOS System

- Create a processor system to allow printing to the console

Basic NIOS System **HARDWARE** EE 3921

- Create a new Quartus project

- Do not select a Simulation Tool in EDA Tool Settings

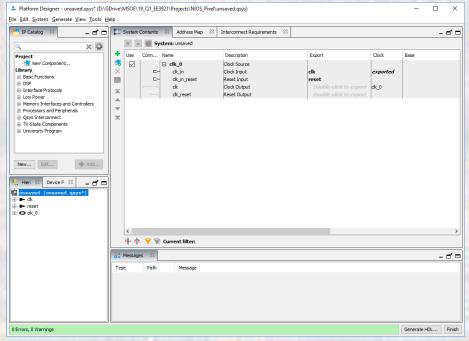

Open Tools → Platform Designer

- Create NIOS System

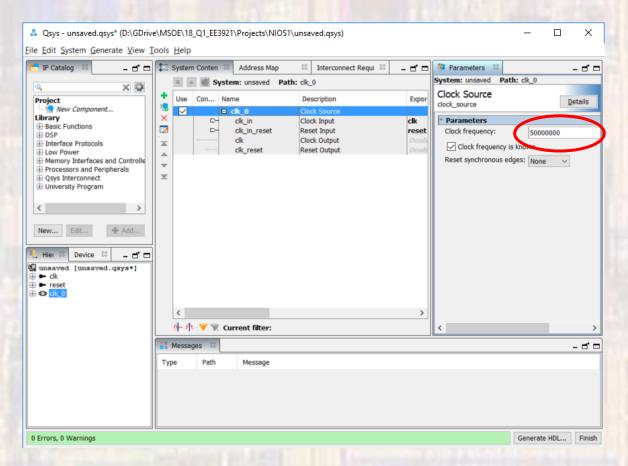

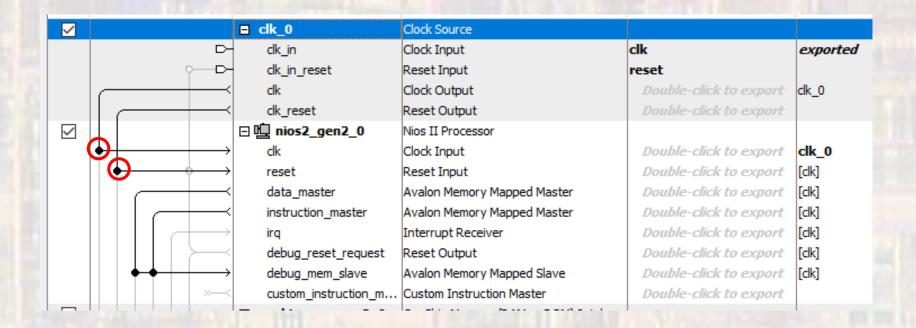

- Double Click on clk\_0 verify clk frequency = 50MHz

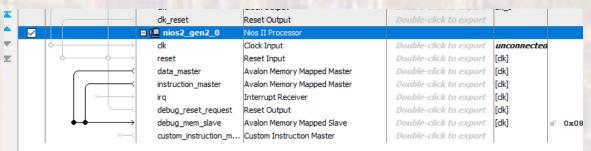

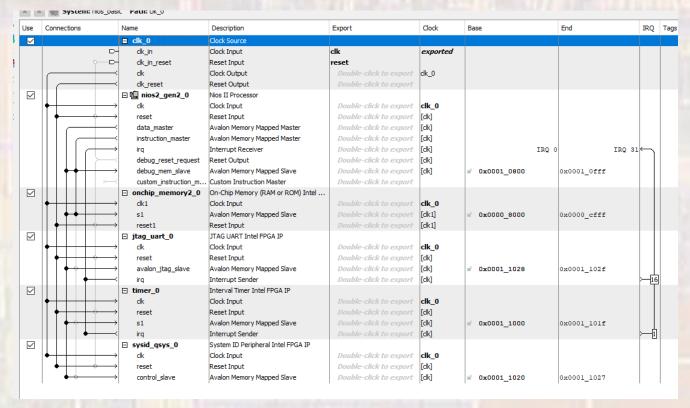

#### Add NIOS

- Processors and Peripherals → Embedded Processors → NIOS II Processor

- NIOS II/f

- No other changes for now

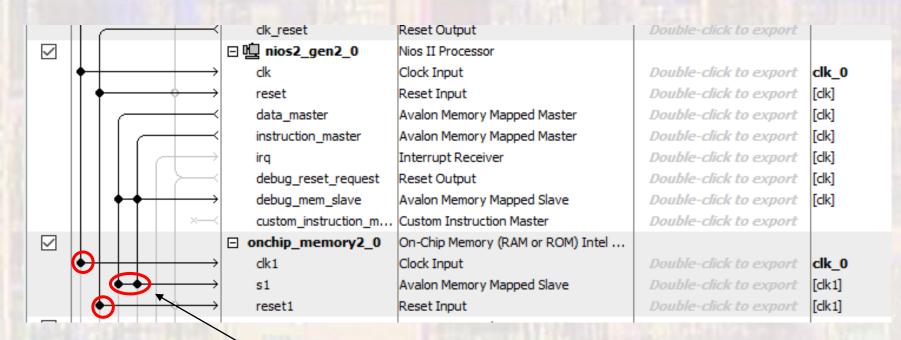

- Add On-chip Memory

- Basic Functions → On Chip Memory → On Chip Memory (RAM or ROM)...

**RAM**

Size = 12,000 bytes

| custom_instruction_m. | Custom Instruction Master         |                        |             |                |

|-----------------------|-----------------------------------|------------------------|-------------|----------------|

|                       |                                   | Double-click to export |             |                |

| ✓ □ onchip_memory2_0  | On-Chip Memory (RAM or ROM) Intel |                        |             |                |

| dk1                   | Clock Input                       | Double-click to export | unconnected |                |

|                       | Avalon Memory Mapped Slave        | Double-click to export | [dk1]       | m <sup>2</sup> |

| reset1                | Reset Input                       | Double-click to export | [dk1]       |                |

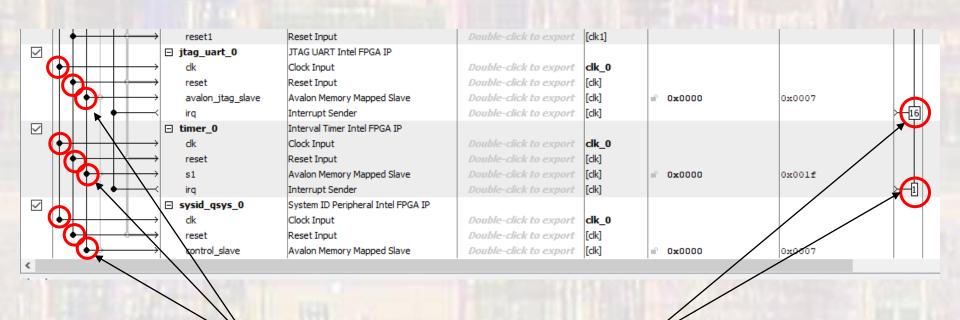

- Add JTAG

- Interface Protocols → Serial → JTAG Uart Intel FPGA IP

- Add Timer

- Processors and Peripherals → Peripherals → Interval

Timer Intel FPGA IP

- Add System ID

Basic Functions → Simulation; Debug and Verification → Debug and Performance → System ID Peripheral Intel

**FPGAIP**

|   | II & + + + & - >                          | reset1            | Reset Input                        | Double-click to export | [dk1]       |

|---|-------------------------------------------|-------------------|------------------------------------|------------------------|-------------|

|   |                                           | □ jtag_uart_0     | JTAG UART Intel FPGA IP            |                        |             |

|   | $  \downarrow           \rightarrow  $    | clk               | Clock Input                        | Double-click to export | unconnected |

|   | $   \diamond + + + \diamond \rightarrow $ | reset             | Reset Input                        | Double-click to export | [clk]       |

|   |                                           | avalon_jtag_slave | Avalon Memory Mapped Slave         | Double-click to export | [dk] =      |

|   |                                           | irq               | Interrupt Sender                   | Double-click to export | [dk]        |

|   |                                           | ☐ timer_0         | Interval Timer Intel FPGA IP       |                        |             |

|   | $  \diamond \cdots \rangle$               | clk               | Clock Input                        | Double-click to export | unconnected |

|   | $   \diamond + + + \diamond \rightarrow$  | reset             | Reset Input                        | Double-click to export | [dk]        |

|   |                                           | s1                | Avalon Memory Mapped Slave         | Double-click to export | [dk]        |

|   |                                           | irq               | Interrupt Sender                   | Double-click to export | [clk]       |

| ~ |                                           | ☐ sysid_qsys_0    | System ID Peripheral Intel FPGA IP |                        |             |

|   | $  \diamond     \longrightarrow$          | dk                | Clock Input                        | Double-click to export | unconnected |

|   |                                           | reset             | Reset Input                        | Double-click to export | [clk]       |

|   | <b> </b>                                  | control_slave     | Avalon Memory Mapped Slave         | Double-click to export | [dk]        |

| / |                                           |                   |                                    |                        |             |

- Connect up basic NIOS system

- NIOS Inputs

- Connect up basic NIOS system

- On-chip Memory

Connect to data and instruction masters

- Connect up basic NIOS system

- JTAG, Timer, SysID

Connect to data master

Assign Priorities

- Connect up basic NIOS system

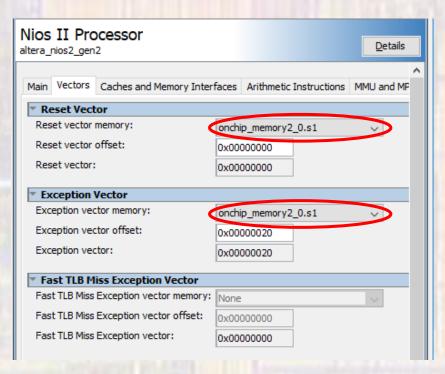

- Assign the NIOS II Reset and Exception vectors

- Open the NIOS Processor

- Select Vectors

- Select on-chip memory for Reset and Exception

- Complete Basic System

- Assign base addresses

- System → Assign Base Addresses

# Assign Base Addresses ... Platform Designer - unsaved.qsys\* (D\\GDrive\MSOE\19\_Q1\_EE3921\\Projec File Edit System Generate View Tools Help Upgrade IP Cores... Assign Base Addresses Assign Base Addresses Assign Interrupt Numbers Assign Custom Instruction Opcodes Ubran Base Bow System With Platform Designer Interconnect Remove Dangling Connections Import Interface Requirements...

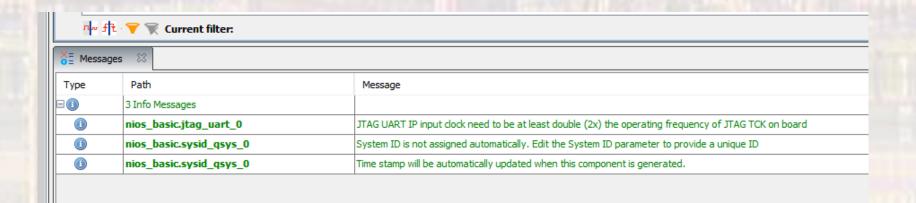

- Create Basic System

- Check for errors

- Create Basic System

- Save the Platform Designer system

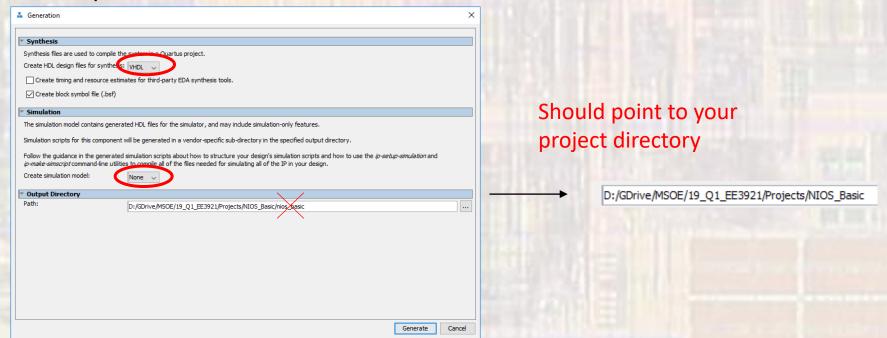

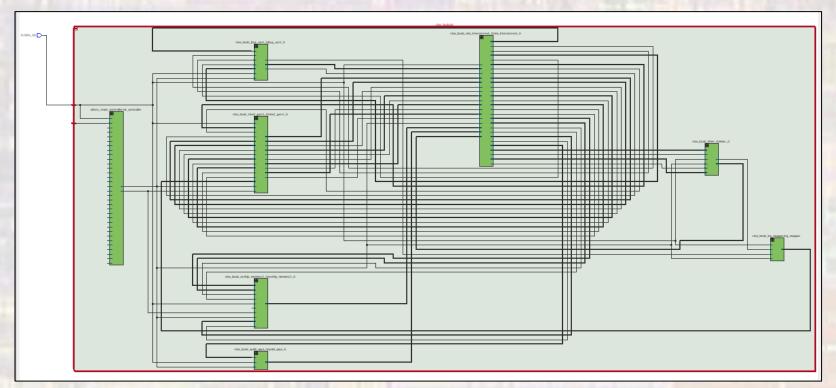

- Generate the Platform Designer system

- Generate → Generate HDL

- The first time you generate you must delete the last directory in the path – don't use the '...'

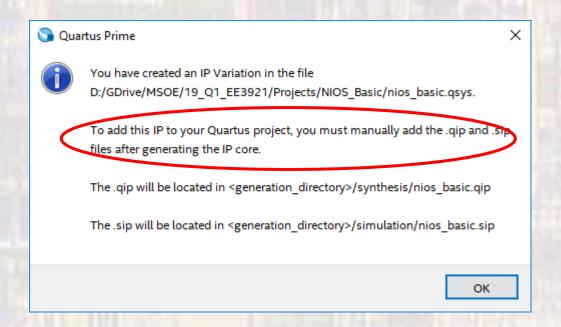

- Create Basic System

- Add the .qip file to the project

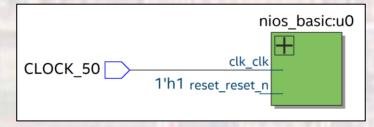

- Create DE10 Design

- Instantiate into a VHDL file

- Open a new VHDL design (nios\_basic\_de10.vhdl)

- In Platform Designer: Generate → Show Instantiation Template

- Create DE10 Design

- Instantiate into a VHDL file

```

nios_basic_de10.vhdl

by: johnsontimoj

created: 8/17/2018

version: 0.0

Basic NIOS example

no I/O pins

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity nios_basic_de10 is

port(

CLOCK_50 : in std_logic

end entity;

```

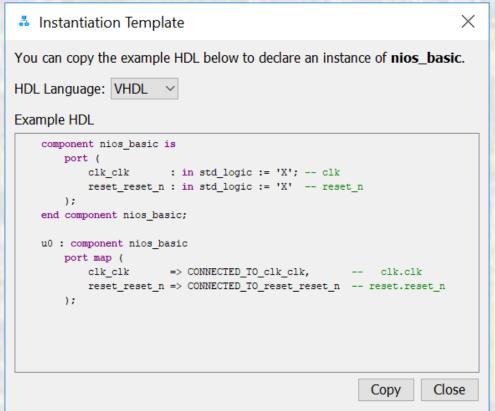

#### Instantiation template component

Instantiation template instance mapped to DE10 qsf pin aliases

- Create DE10 Design

- Prepare to synthesize

- If you did not do these when you created the project be sure to do them now

- assignments → device → device and Pin options

- Single Uncompressed with memory initialization

- Import the pin aliases (qsf file)

- Setup the SDC file for timing analysis

- Be sure to set your top level entity

- Start Compilation

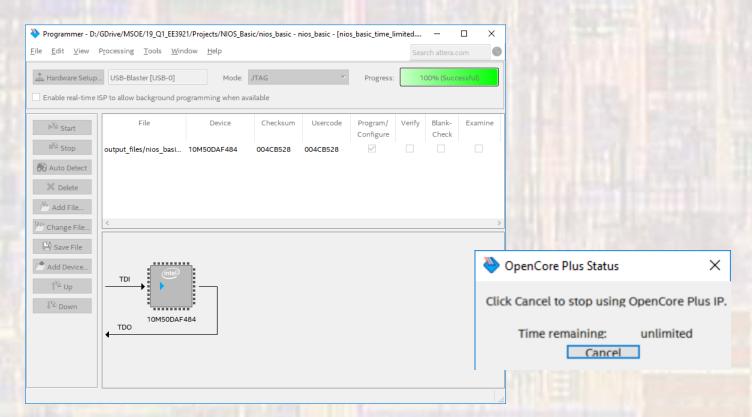

#### Create DE10 Design

- Create DE10 Design

- Complete the HW setup

- Download the HW project onto the board

- DO NOT CLOSE either of these windows

Basic NIOS System **SOFTWARE** 23 © tj EE 3921

- Create Eclipse System

- Open NIOSII software

- Tools → NIOSII Software Build Tools for Eclipse

- Select the project directory for the workspace

- Create the BSP

- File → New → NIOSII Application and BSP from template

- Select the SOPCinfo file in the project directory

- Provide a name for the sw project (I use 'project\_name\_sw')

- Blank Project

- Edit the BSP

- Right click on the BSP, NIOS II → BSP Editor

- Change the properties for small systems

- Small C library

- Reduced device drivers

- Generate the BSP (bottom of window)

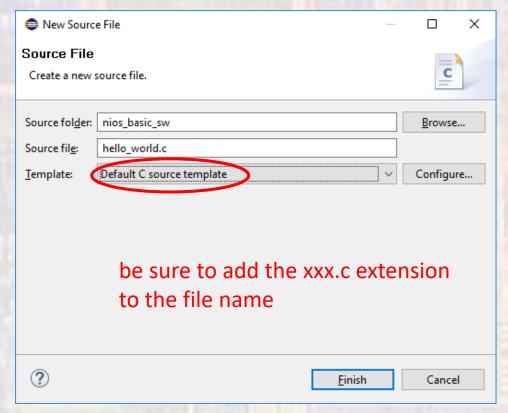

- Create Eclipse System

- Create program

- Right click on the project directory and choose

New → c source file

- Create Eclipse System

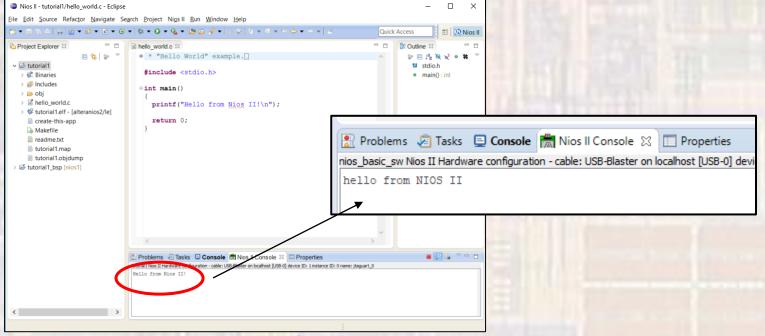

- Create program

- Type in the program

```

Project Explorer 🔀

🖟 hello_world.c 🔀

2⊕ * hello world.c.

#include <stdio.h>

pinios_basic_sw

> 🐉 Binaries

9 int main() {

👘 Includes

printf("hello from NIOS II\n");

10

🗁 obj

11

hello_world.c

12

return 0:

> prios_basic_sw.elf - [alteranios2/le]

13 }

create-this-app

14

Makefile

15

nios_basic_sw.map

nios_basic_sw.objdump

readme.txt

> inios_basic_sw_bsp [nios_basic]

```

- Create Eclipse System

- Compile and run the software

- Select the code file (hello\_world.c)

- Project → Build Project

- Right Click on the project → run as → Nios II Hardware