## Last updated 3/1/21

- SDRAM

- 512Mb : 128Mx4, 64Mx8, 32Mx16

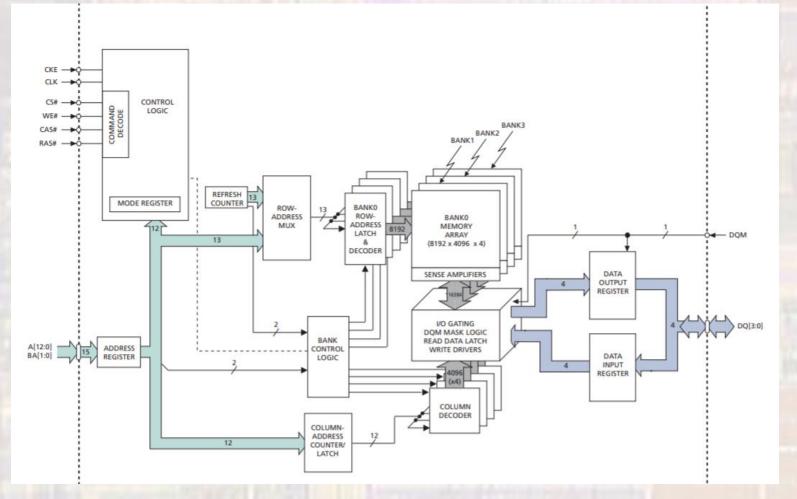

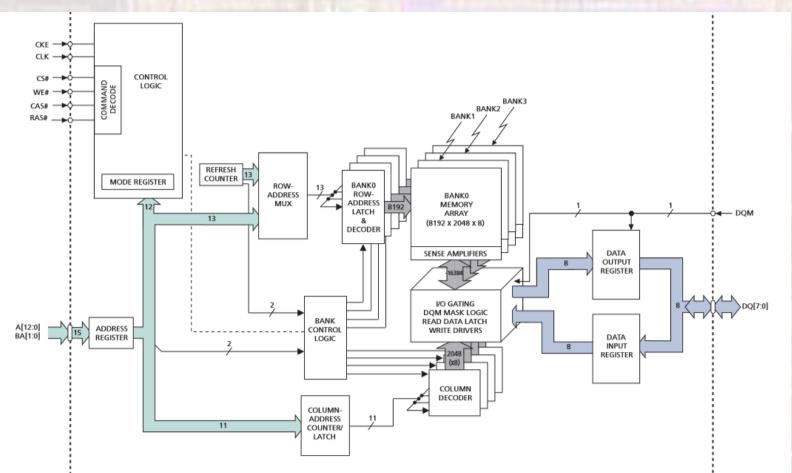

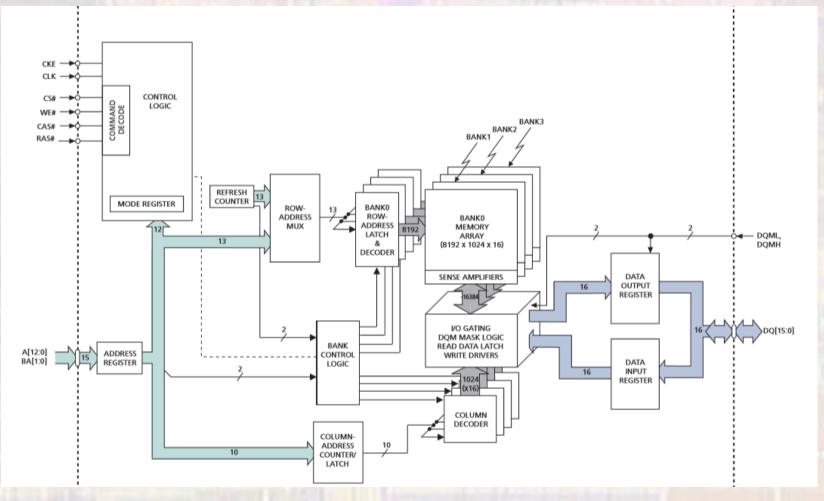

The 512Mb SDRAM is a high-speed CMOS, dynamic random-access memory containing 536,870,912 bits. It is internally configured as a quad-bank DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Each of the x4's 134,217,728-bit banks is organized as 8192 rows by 4096 columns by 4 bits. Each of the x8's 134,217,728-bit banks is organized as 8192 rows by 2048 columns by 8 bits. Each of the x16's 134,217,728-bit banks is organized as 8192 rows by 1024 columns by 16 bits.

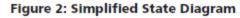

Read and write accesses to the SDRAM are burst-oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command, which is then followed by a READ or WRITE command. The address bits registered coincident with the ACTIVE command are used to select the bank and row to be accessed (BA[1:0] select the bank; A[12:0] select the row). The address bits registered coincident with the READ or WRITE command are used to select the starting column location for the burst access.

- SDRAM

- 512Mb : 128Mx4

The SDRAM provides for programmable read or write burst lengths (BL) of 1, 2, 4, or 8 locations, or the full page, with a burst terminate option. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst sequence.

The 512Mb SDRAM uses an internal pipelined architecture to achieve high-speed operation. This architecture is compatible with the 2n rule of prefetch architectures, but it also allows the column address to be changed on every clock cycle to achieve a highspeed, fully random access. Precharging one bank while accessing one of the other three banks will hide the PRECHARGE cycles and provide seamless, high-speed, random-access operation.

SDRAMs offer substantial advances in DRAM operating performance, including the ability to synchronously burst data at a high data rate with automatic column-address generation, the ability to interleave between internal banks to hide precharge time, and the capability to randomly change column addresses on each clock cycle during a burst access.

- SDRAM

- 512Mb : 128Mx4

- SDRAM

- 512Mb : 64Mx8

- SDRAM

- 512Mb: 32Mx16

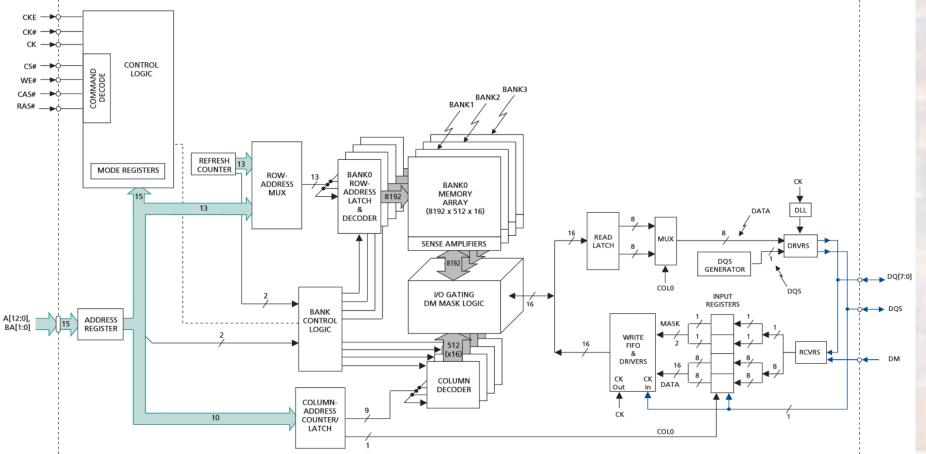

- SDRAM DDR

- 256Mb: 32M x 8

- SDRAM Basic Commands

- ACTIVATE select 1 row in a specific bank (RAS) (open)

- READ/WRITE select a column (CAS)

- PRECHARGE prepare 1 or all banks for activation (close)

- Auto precharge automatically executes precharge after a Read or Write

- NOP do nothing

- Commands are decoded from the CS, RAS, CAS, and WE signals

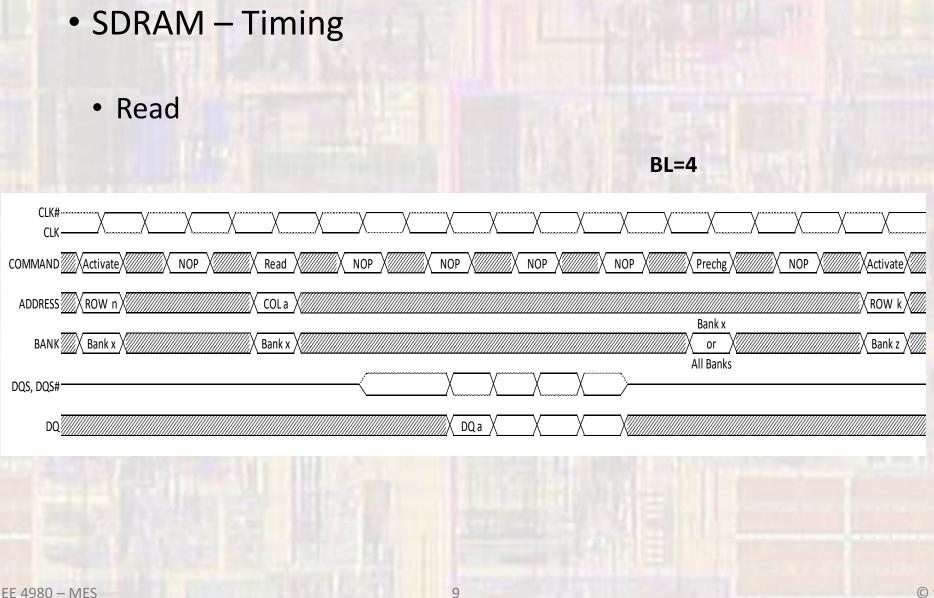

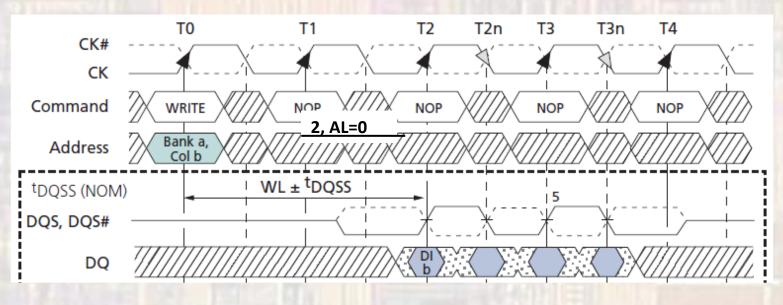

• Write

| CLK#<br>CLK— | X        | X                 | X   | X                | X      | X                | X   | X | X    | X | X   | X | X   | X | X               |          | X   | X                | X        |

|--------------|----------|-------------------|-----|------------------|--------|------------------|-----|---|------|---|-----|---|-----|---|-----------------|----------|-----|------------------|----------|

| COMMAND      | Activate | X                 | NOP | X                | Write  | X                | NOP | X | NOP  | X | NOP | X | NOP | X | Prechg          | <u> </u> | NOP | X <u>IIIII</u> ) | Activate |

| ADDRESS      | ROW n    | X <u>IIIIIIII</u> |     | <u>IIIIIIX</u> X | COLa   | X                |     |   |      |   |     |   |     |   | Bank x          |          |     |                  | (ROW k   |

| BANK         | X Bank x | X <u>IIIIIIII</u> |     | <u>IIIIIIX</u> X | Bank x | X <i>IIIIIII</i> |     |   |      |   |     |   |     |   | Or<br>All Banks |          |     |                  | Bank z   |

| DQS, DQS#    |          |                   |     |                  |        |                  |     | < | X    | X | X   | X |     |   |                 |          |     |                  | -        |

| DQ           |          |                   |     |                  |        |                  |     | X | DQ a |   | /   | X |     |   |                 |          |     |                  |          |

|              |          |                   |     |                  |        | RTS.             |     |   |      |   |     |   |     |   |                 |          |     |                  |          |

|              |          |                   |     |                  |        |                  |     |   |      |   |     |   |     |   |                 |          |     |                  |          |

BL=4

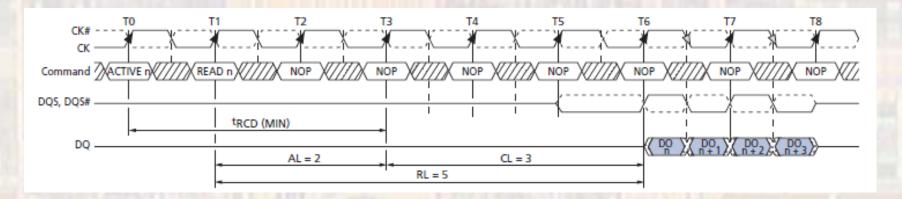

- SDRAM Timing

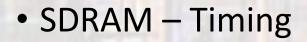

- Read Latency

- CL CAS latency clock cycles from CAS to data out

- AL Additional Latency pipeline commands or match parts

- SDRAM Timing

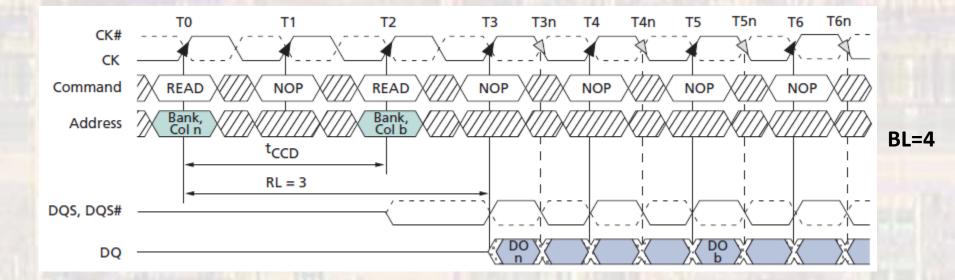

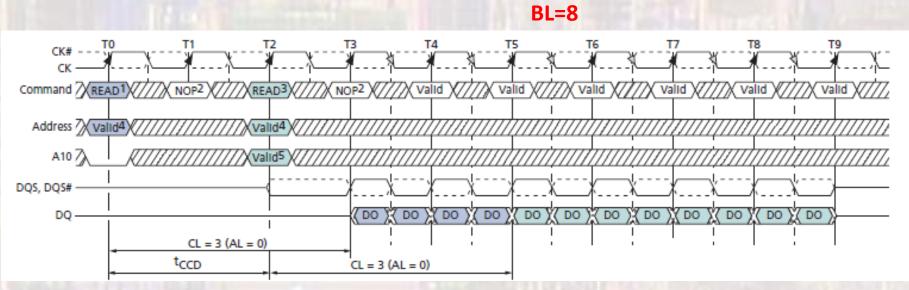

- Non-consecutive Read bursts

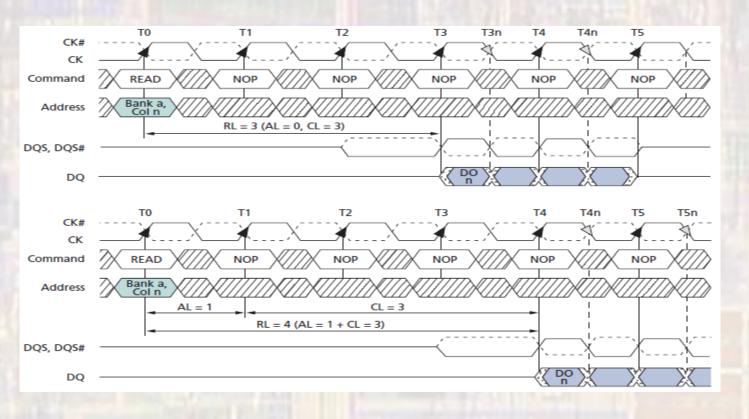

- SDRAM Timing

- Consecutive Read bursts

- SDRAM Timing

- Read interrupted by read

- Valid addresses include

- Same bank, same row w/o precharge

- Different bank assuming precharged

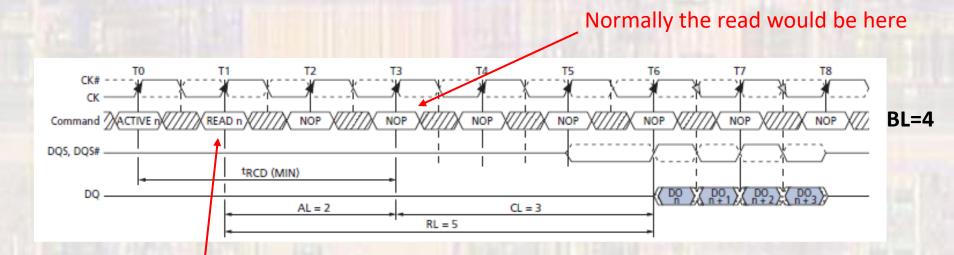

- SDRAM Timing

- POSTED CAS

- For CL=3, set AL=2 and move the READ command forward 2 clocks

Move the read forward to complete the cycle and do something else

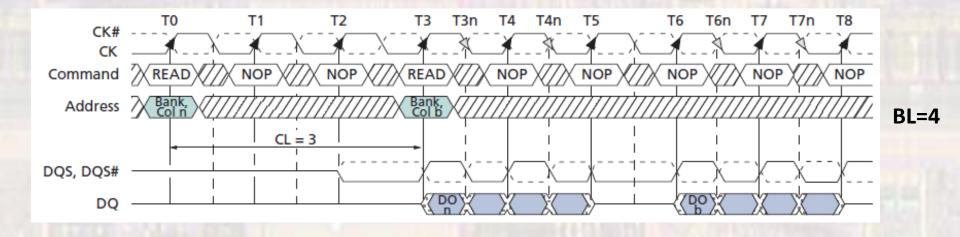

SDRAM – Timing

#### • DQS

- Signal generated by the SDRAM in read mode

- Used by the Memory Management Unit (MMU) to know when to sample the read data

- MMU must sample at halfway point of DQS

BL=4

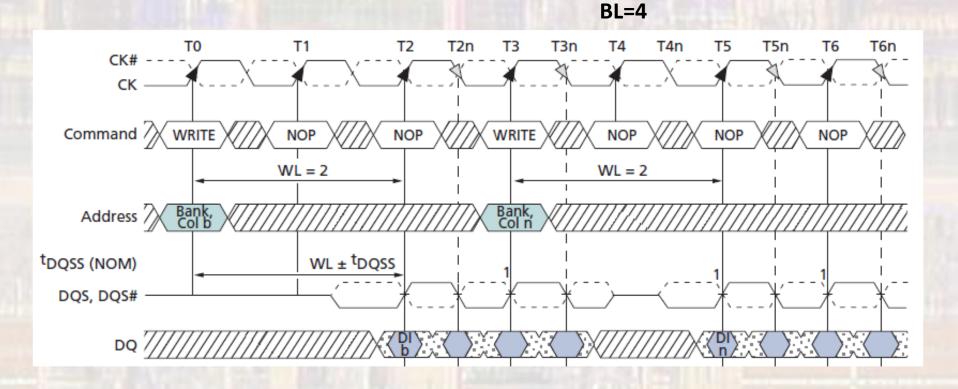

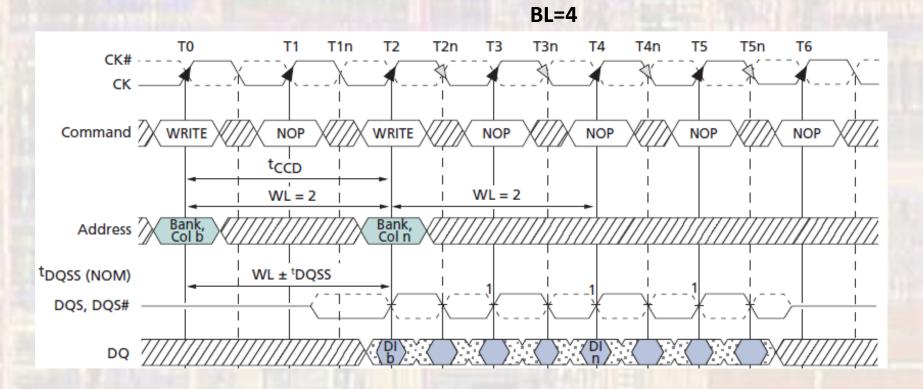

- SDRAM Timing

- Write

- DQS generated by the MMU in write mode

- Edge must match up with the center of valid data

BL=4

- SDRAM Timing

- Non-consecutive Writes

- SDRAM Timing

- Consecutive Writes

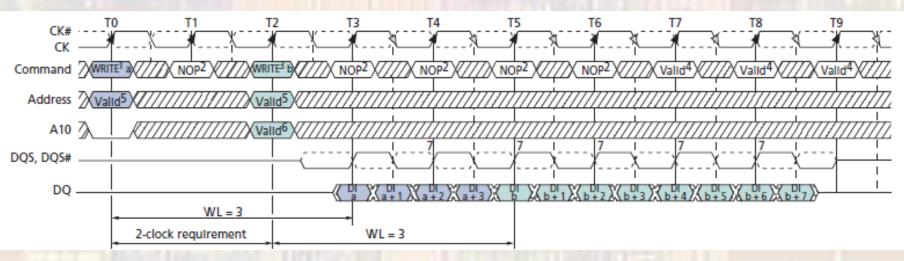

SDRAM – Timing

• Write interrupt by Write

BL=8

### SDRAM – DDR3 spec sheet

1Gb: x4, x8, x16 DDR3 SDRAM Features

### DDR3 SDRAM

MT41J256M4 – 32 Meg x <mark>4</mark> x 8 banks MT41J128M8 – 16 Meg x <mark>8</mark> x 8 banks MT41J64M16 – 8 Meg x <mark>16</mark> x 8 banks

#### Features

- V<sub>DD</sub> = V<sub>DDO</sub> = 1.5V ±0.075V

- 1.5V center-terminated push/pull I/O

- Differential bidirectional data strobe

- 9n-hit profetch architecture

| Options <sup>1</sup>              | Marking |

|-----------------------------------|---------|

| <ul> <li>Configuration</li> </ul> | _       |

| – 256 Meg x 4                     | 256M4   |

| - 128 Meg x 8                     | 128M8   |

| - 64 Meg x 16                     | 64M16   |

- 1Gb:x4 = 256Mx4 = 32Mx4x8 same part

- 1Gb = 256Mx4 = 128Mx8 = 64Mx16 different parts same die

### SDRAM – DDR3 spec sheet

| Table 1: Key | y Timing Parameters |

|--------------|---------------------|

|--------------|---------------------|

| Speed Grade           | Data Rate (MT/s)  | Target <sup>t</sup> RCD- <sup>t</sup> RP-CL | <sup>t</sup> RCD (ns) | <sup>t</sup> RP (ns) | CL (ns)            |

|-----------------------|-------------------|---------------------------------------------|-----------------------|----------------------|--------------------|

| -107 <sup>1, 2</sup>  | <mark>1866</mark> | 13-13 <mark>-13</mark>                      | 13.91                 | 13.91                | <mark>13.91</mark> |

| -107E <sup>1, 2</sup> | 1866              | 12-12-12                                    | 12.84                 | 12.84                | 12.84              |

| -125 <sup>1, 2</sup>  | 1600              | 11-11-11                                    | 13.75                 | 13.75                | 13.75              |

| -15E <sup>1</sup>     | 1333              | 9-9-9                                       | 13.5                  | 13.5                 | 13.5               |

| 187E                  | 1066              | 7-7-7                                       | 13.1                  | 13.1                 | 13.1               |

- 1866MT/s --> 933MHz clock operation

- --> 1.071ns/clock

- --> CL=13 means tCL = 13.93ns delay

### SDRAM – DDR3 spec sheet

| Parameter         | 256 Meg x 4          | 128 Meg x 8          | 64 Meg x 16          |

|-------------------|----------------------|----------------------|----------------------|

| Configuration     | 32 Meg x 4 x 8 banks | 16 Meg x 8 x 8 banks | 8 Meg x 16 x 8 banks |

| Refresh count     | 8K                   | 8K                   | 8K                   |

| Row addressing    | 16K (A[13:0])        | 16K (A[13:0])        | 8K (A[12:0])         |

| Bank addressing   | 8 (BA[2:0])          | 8 (BA[2:0])          | 8 (BA[2:0])          |

| Column addressing | 2K (A[11, 9:0])      | 1K (A[9:0])          | 1K (A[9:0])          |

| Page Size         | 1KB                  | 1KB                  | 2KB                  |

- It appears this memory has

- 8 arrays

Table 2: Addressing

- 8K rows X 16K bitlines 8 X 8K X 16Kb = 1Gb

- x4 and x8 break rows in half

- x4 halves the column

## SDRAM - O

SDRAM –

DDR3

spec sheet

Power applied

### SDRAM – DDR3 spec sheet

#### Table 70: Truth Table - Command

Notes 1-5 apply to the entire table

|                |          |        | C              | KE            |     |      |      |     |             |                  |     |     |               |       |

|----------------|----------|--------|----------------|---------------|-----|------|------|-----|-------------|------------------|-----|-----|---------------|-------|

| Function       |          | Symbol | Prev.<br>Cycle | Next<br>Cycle | CS# | RAS# | CAS# | WE# | BA<br>[2:0] | An               | A12 | A10 | A[11,<br>9:0] | Notes |

| Bank ACTIVAT   | ſE       | ACT    | Н              | Н             | L   | L    | Н    | Н   | BA          | Row address (RA) |     | RA) |               |       |

| WRITE          | BL8MRS,  | WR     | Н              | Н             | L   | Н    | L    | L   | BA          | RFU              | V   | L   | CA            | 8     |

| READ           | BL8MRS,  | RD     | Н              | Н             | L   | Н    | L    | Н   | BA          | RFU              | V   | L   | CA            | 8     |

| Single-bank PF | RECHARGE | PRE    | Н              | Н             | L   | L    | Н    | L   | BA          | V                | V   | L   | V             |       |

| PRECHARGE a    | l banks  | PREA   | Н              | Н             | L   | L    | Н    | L   | V           |                  | V   | Н   | V             |       |

### SDRAM – DDR3 spec sheet

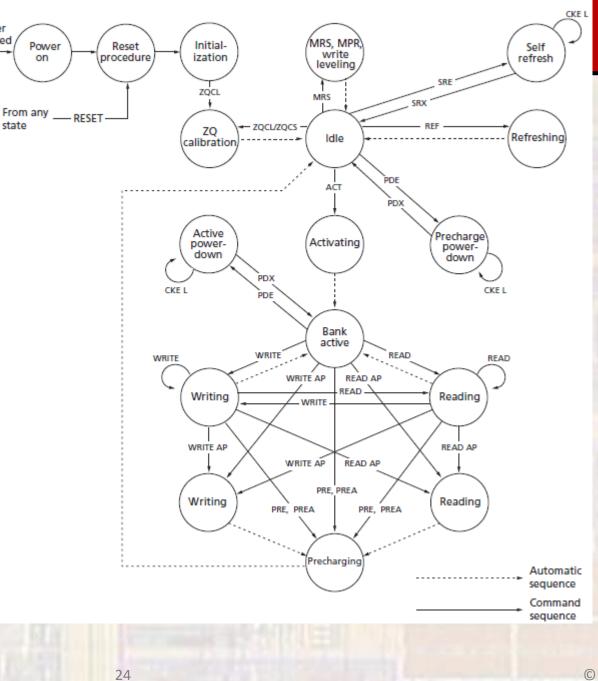

#### Figure 3: 256 Meg x 4 Functional Block Diagram

### SDRAM – DDR3 spec sheet

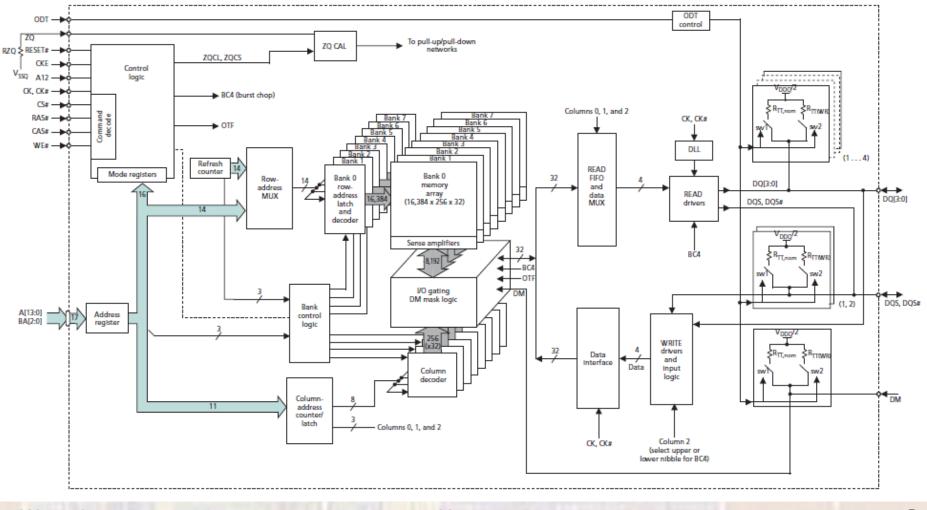

#### Figure 5: 64 Meg x 16 Functional Block Diagram

### • Dimm

- Dual Inline Memory Module

- Multiple memory chips integrated onto a board

- Support 64bit transfers

- Parallel configuration

- Different chip selects

- Word configuration

- Each chip supplies part of a bigger word

- 8, x1 devices  $\rightarrow$  8 bit word

- 8, x4 devices  $\rightarrow$  32 bit word

- use PCx-zzzz where zzzz is max bandwidth (transfer rate in bytes)

- DDR2-800 → pc2-6400 (transfers x # bits /8) = 800M x 64b /8 = 6.4GB/s

© tj

- Dimm

- pc, pc2, pc3 different slot configurations

| SDRAM       | - Operatior     | Memory    | Real Clock | Maximum<br>Theoretical<br>Transfer | Memory<br>Module |

|-------------|-----------------|-----------|------------|------------------------------------|------------------|

| • DDR - Teo | chnology        | DDR200    | 100 MHz    | <b>Rate</b><br>1,600 MB/s          | PC-1600          |

|             |                 | DDR266    | 133 MHz    | 2,133 MB/s                         | PC-2100          |

|             |                 | DDR333    | 166 MHz    | 2,666 MB/s                         | PC-2700          |

|             |                 | DDR400    | 200 MHz    | 3,200 MB/s                         | PC-3200          |

| Technology  | Tunical Valtage | DDR2-400  | 200 MHz    | 3,200 MB/s                         | PC2-3200         |

| Technology  | Typical Voltage | DDR2-533  | 266 MHz    | 4,266 MB/s                         | PC2-4200         |

| DDR         | 2.5 V           | DDR2-667  | 333 MHz    | 5,333 MB/s                         | PC2-5300         |

| DDR2        | 1.8 V           | DDR2-800  | 400 MHz    | 6,400 MB/s                         | PC2-6400         |

| DDR3        | 1.5 V           | DDR2-1066 | 533 MHz    | 8,533 MB/s                         | PC2-8500         |

| DDR4        | 1.2 V           | DDR3-800  | 400 MHz    | 6,400 MB/s                         | PC3-6400         |

| DDR4        | 1.2 V           | DDR3-1066 | 533 MHz    | 8,500 MB/s                         | PC3-8500         |

| DDR5        | 1.1 V           | DDR3-1333 | 666 MHz    | 10,666 MB/s                        | PC3-10600        |

|             |                 | DDR3-1600 | 800 MHz    | 12,800 MB/s                        | PC3-12800        |

### • DDR – Technology

#### • DDR4

| Standard<br>name                                      | Memory<br>clock<br>(MHz) | I/O bus<br>clock<br>(MHz) | Data<br>rate<br>( <u>MT/s</u> ) | Module<br>name | Peak trans-<br>fer rate<br>(MB/s) | Timings<br>CL-tRCD-tRP                       | CAS<br>latency<br>(ns)        |

|-------------------------------------------------------|--------------------------|---------------------------|---------------------------------|----------------|-----------------------------------|----------------------------------------------|-------------------------------|

| DDR4-1600J*<br>DDR4-1600K<br>DDR4-1600L               | 200                      | 800                       | 1600                            | PC4-12800      | 12800                             | 10-10-10<br>11-11-11<br>12-12-12             | 12.5<br>13.75<br>15           |

| DDR4-1866L*<br>DDR4-1866M<br>DDR4-1866N               | 233.33                   | 933.33                    | 1866.67                         | PC4-14900      | 14933.33                          | 12-12-12<br>13-13-13<br>14-14-14             | 12.857<br>13.929<br>15        |

| DDR4-2133N*<br>DDR4-2133P<br>DDR4-2133R               | 266.67                   | 1066.67                   | 2133.33                         | PC4-17000      | 17066.67                          | 14-14-14<br>15-15-15<br>16-16-16             | 13.125<br>14.063<br>15        |

| DDR4-2400P*<br>DDR4-2400R<br>DDR4-2400T<br>DDR4-2400U | 300                      | 1200                      | 2400                            | PC4-19200      | 19200                             | 15-15-15<br>16-16-16<br>17-17-17<br>18-18-18 | 12.5<br>13.32<br>14.16<br>15  |

| DDR4-2666T<br>DDR4-2666U<br>DDR4-2666V<br>DDR4-2666W  | 333.33                   | 1333.33                   | 2666.67                         | PC4-21333      | 21333.33                          | 17-17-17<br>18-18-18<br>19-19-19<br>20-20-20 | 12.75<br>13.50<br>14.25<br>15 |

| DDR4-2933V<br>DDR4-2933W<br>DDR4-2933Y<br>DDR4-2933AA | 366.67                   | 1466.67                   | 2933.33                         | PC4-23466      | 23466.67                          | 19-19-19<br>20-20-20<br>21-21-21<br>22-22-22 | 12.96<br>13.64<br>14.32<br>15 |

| DDR4-3200W<br>DDR4-3200AA<br>DDR4-3200AC              | 400                      | 1600                      | 3200                            | PC4-25600      | 25600                             | 20-20-20<br>22-22-22<br>24-24-24             | 12.5<br>13.75<br>15           |

- DDR Technology

- DDR5

| Feature                      | DDR5 DRAMs                                                                                                                                                      | DDR4 DRAMs                                                                                              |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| Device size                  | 8Gb to 64Gb                                                                                                                                                     | 2Gb to 16Gb                                                                                             |  |  |  |

| Speed                        | Up to 6400 Mbps                                                                                                                                                 | Up to 3200 Mbps                                                                                         |  |  |  |

| Voltage                      | 1.1V DRAM I/O                                                                                                                                                   | 1.2V DRAM I/O                                                                                           |  |  |  |

| Burst length per transaction | 16 beats                                                                                                                                                        | 8 beats                                                                                                 |  |  |  |

| DIMM topology                | <ul> <li>Dual-channel, with each channel being<br/>32-bits wide for data</li> <li>ECC DIMMs are generally 80-bits wide,<br/>with 40 bits per channel</li> </ul> | <ul> <li>Single-channel with a data-width of<br/>64 bits</li> <li>ECC DIMMs are 72-bits wide</li> </ul> |  |  |  |