# SRAM

Last updated 3/1/21

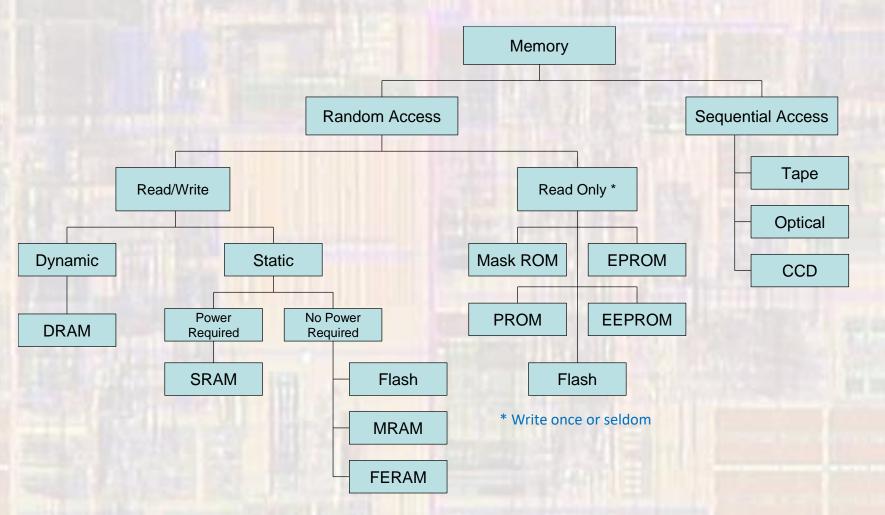

Memory Taxonomy

- SRAM Static Random Access Memory

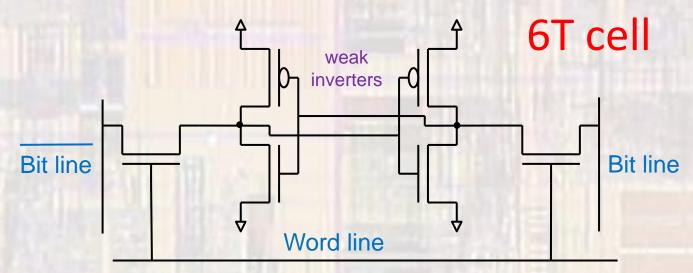

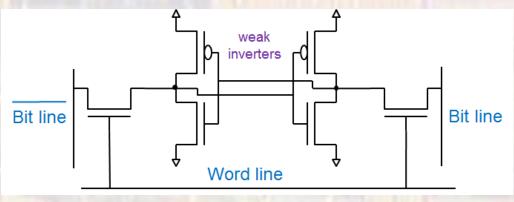

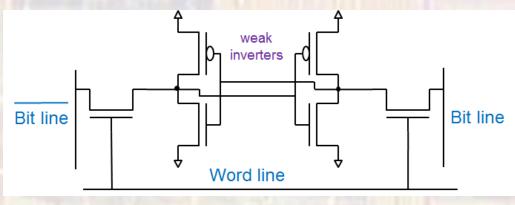

- · Memory cell (1 bit) is based on a feedback circuit

- Bit value is retained as long as power is maintained

- Fastest read/write (R/W)

- Highest power

- Lowest density

- Used in caches and small data memories

- SRAM Static Random Access Memory

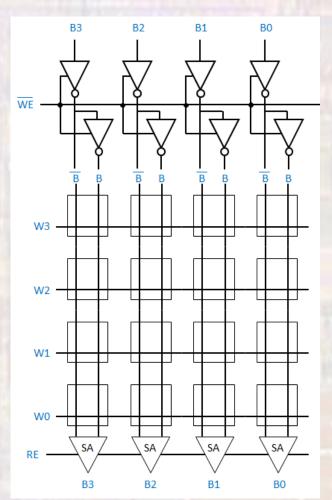

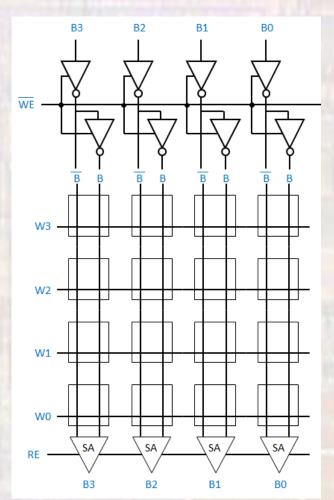

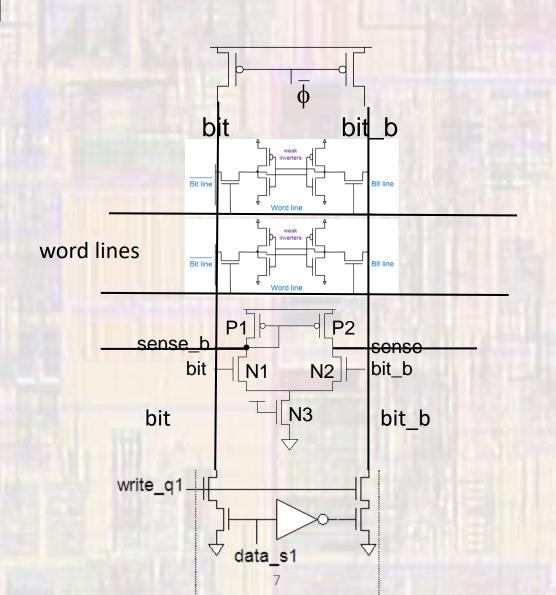

- Write

- All Word lines low

- Read Enable (RE) disabled (low)

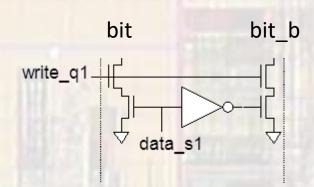

- Place B0, B1, B2, B3 on inputs

- Pull write enable bar (WE) low

- Strobe the desired word line high

- Bit lines override the bit cell inverters and store the new value in the cell

- SRAM Static Random Access Memory

- Read

- All Word lines low

- Write enable bar (WE) high

- inverters tristated

- Read Enable (RE) high

- Strobe the desired word line high

- Bit cell inverters drive the bit lines and sense amplifiers read the value

- SRAM Static Random Access Memory

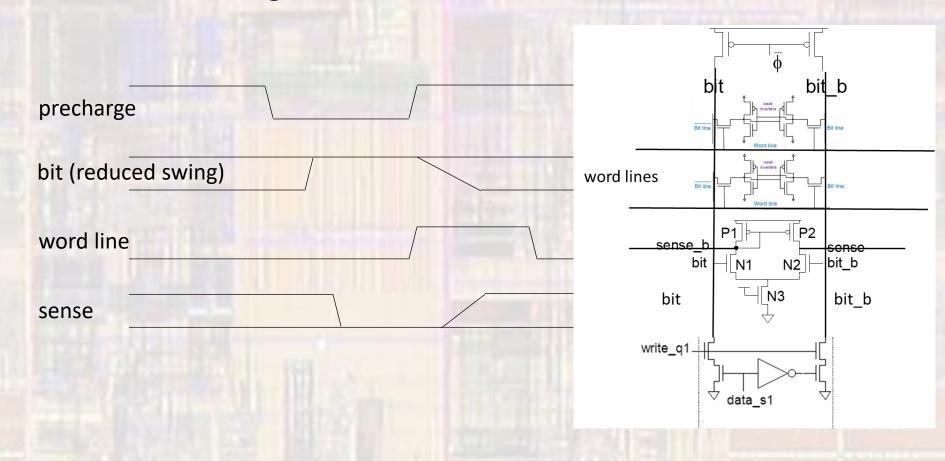

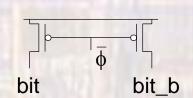

- Pre-charging

- To ensure consistent timing pre-charge bit and bit\_b

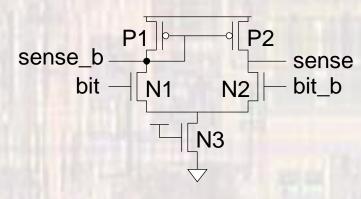

- Sense amplifier

- With large arrays, the bit/bit\_b transition times can be very long

- Use high gain sense amplifiers to make decisions quickly

- Write Enable

SRAM

EE 4980 - MES

© tj

- SRAM Static Random Access Memory

- Circuit timing