## Last updated 4/29/20

#### Serial Peripheral Interface SPI

- SPI Overview

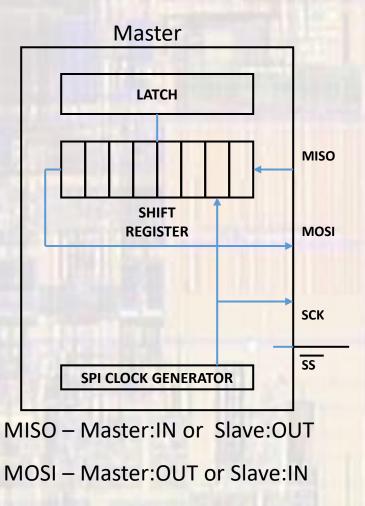

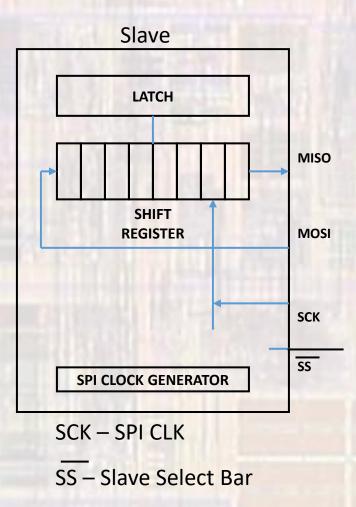

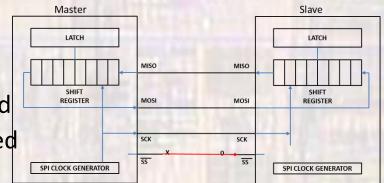

- 8 bit synchronous shift register used to communicate externally

- Most often used to communicate with peripherals

- displays, sensors, converters

- Can be used for inter-processor communication

- Two modes of operation

- Master responsible for providing the clock

- Slave receives clock from the master

SPI Overview

Δ

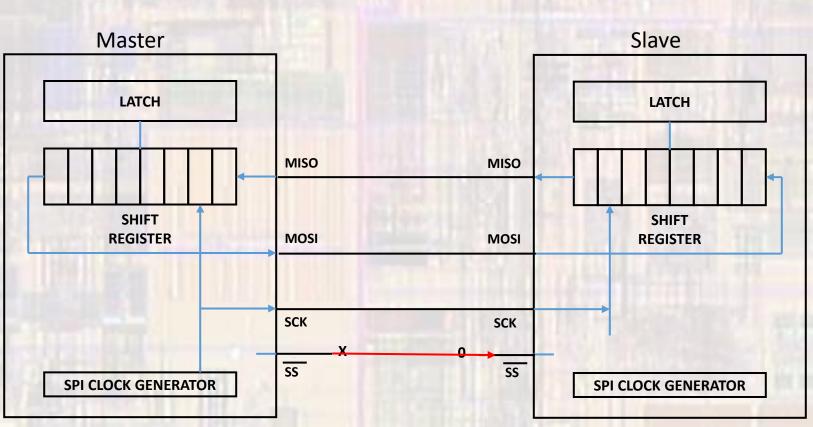

SPI Operation

Latch → Shift Register in both master and slave Master generates 8 clocks → shifts both registers (swaps content) Shift Register → Latch in both master and slave

© tj

- SPI Operation

- Configure 1 device as master

- Configure 1 or more devices as slaves

- Load values into register(s)

- Pull SSbar low on the desired slave device

- Initiate transfer by writing to the data register

- The master will generate the appropriate clocks

- If interrupts are enabled an interrupt will be generated on completion

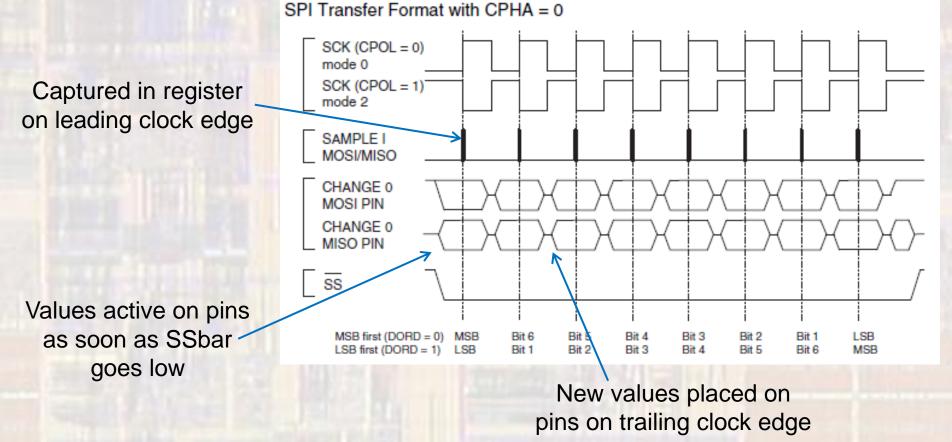

- SPI Operation

- 2 options for clock polarity

- CPOL = 0 → rising edge triggered

- CPOL = 1  $\rightarrow$  falling edge triggered

- 2 options for clock phase

- CPHA =  $0 \rightarrow$  leading edge triggered

- CPHA =  $1 \rightarrow$  trailing edge triggered

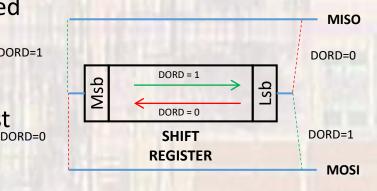

#### DORD=1

- 2 options on transfer direction

- DORD =  $0 \rightarrow$  MSB transferred first

- DORD = 1  $\rightarrow$  LSB transferred first

- SPI Operation

- CPHA = 0

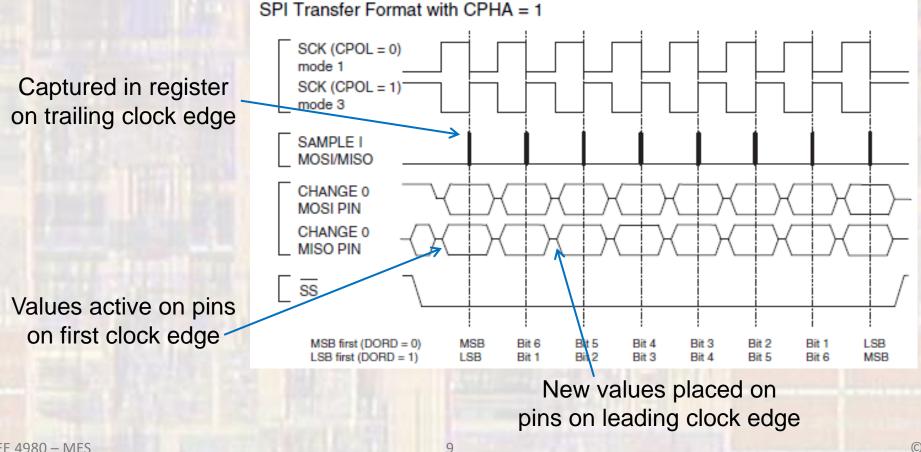

- SPI Operation

- CPHA = 1

- SPI Operation

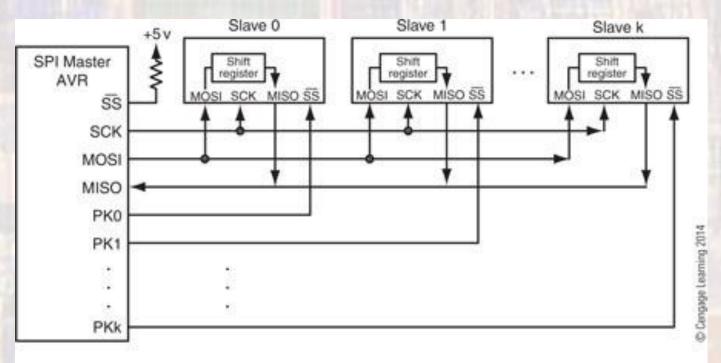

- Multiple Slave Configuration

- SPI Operation

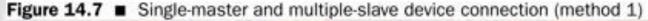

- Multiple Slave Extended Shift Configuration

Figure 14.8 Single-master and multiple-slave device connection (method 2)

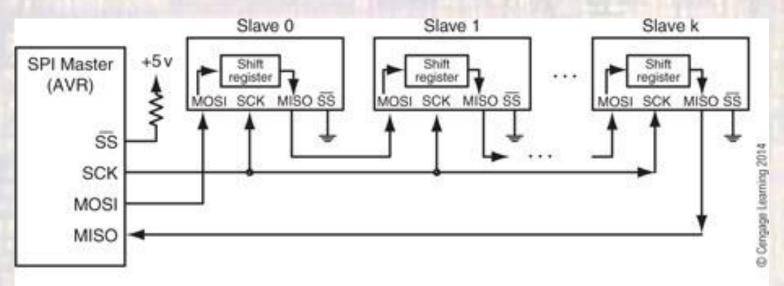

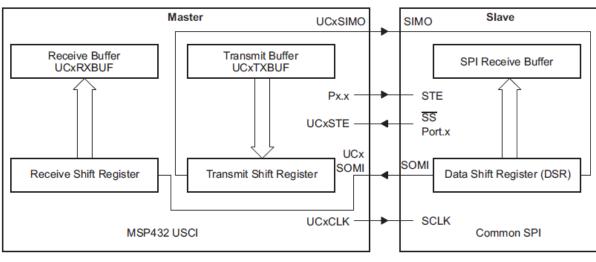

- SPI Master Mode

- Receive/Transmit initiated by writing to TX buffer

- Data is moved to the TX shift register as soon as it is empty – UCTXIFG flag set – transfer is NOT complete

- Transfer is controlled by the state machine

- When complete RX data moved to the RX buffer UCRXIFG flag is set – transfer is complete

Figure 23-2. eUSCI Master and External Slave (UCSTEM = 0)

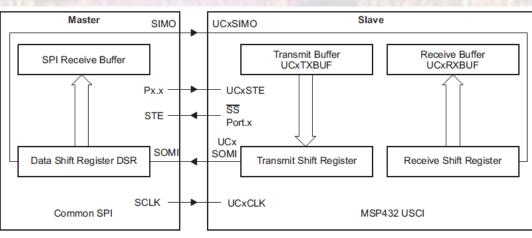

- SPI Slave Mode

- External clock controls the transfer

- Data is moved to the TX shift register as soon as it is empty – UCTXIFG flag set – transfer is NOT complete

- When complete, RX data moved to the RX buffer UCRXIFG flag is set

- UCOE flag is set if the RX buffer has not been read prior to a new completed transfer

Figure 23-3. eUSCI Slave and External Master

#### Two Wire Interface TWI

I<sup>2</sup>C

© tj

#### TWI - Overview

- 8 bit synchronous shift register used to communicate externally

- 9 bit total communication packet

- uni-directional

- Most often used to communicate with peripherals

- displays, sensors, converters

- Supports multiple masters and multiple slaves

- 4 modes of operation

- Master Receive

- Master Transmit

- Slave Receive

- Slave Transmit

© tj

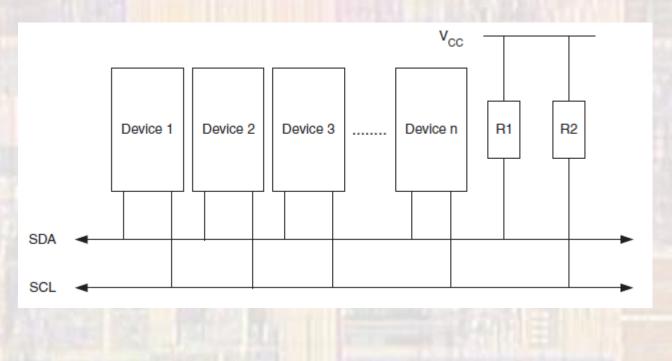

- TWI Overview

- Open drain configuration

- outputs only pull down

- pull up resistors or current sources pull up

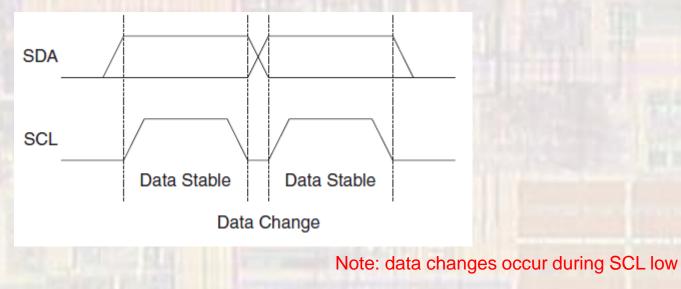

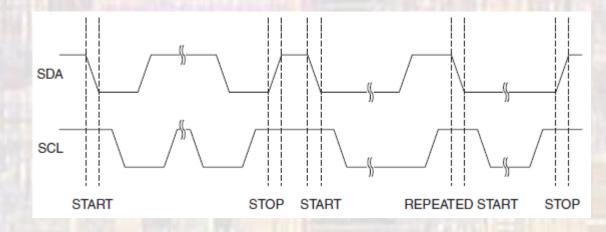

- TWI Timing

- SDA data line

- SCL clock line

- Data must be valid during the entire positive clock cycle time

- TWI Timing

- Special timing requirements for

- start transmission

- stop transmission

- repeated start transition

- master does not relinquish the bus in this mode

#### TWI Timing

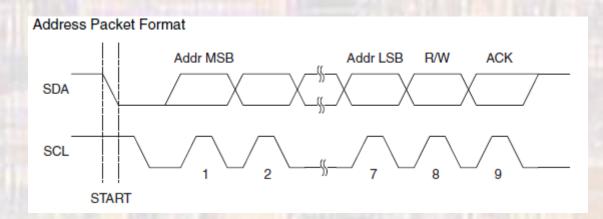

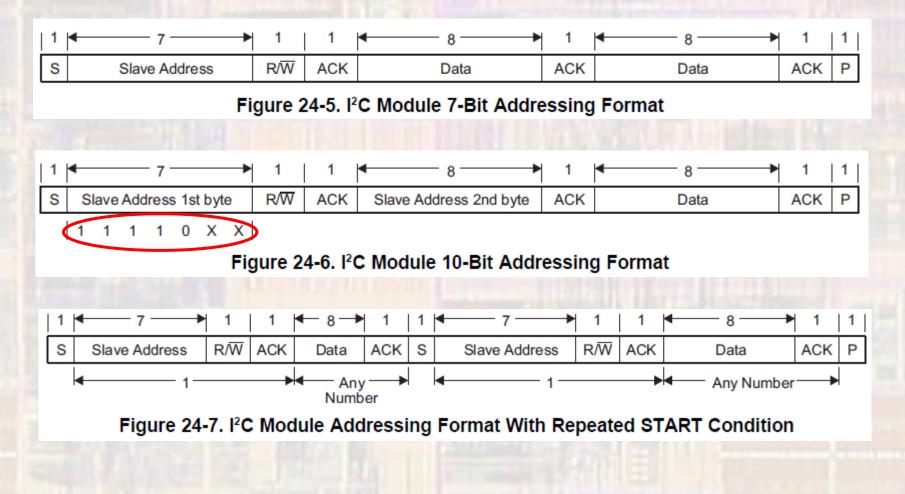

#### Addressing

- Indicate which slave to transmit to or receive from by first transmitting the "address" of the desired device

- Often this value is hardwired via external pins on the slave device

- 7 bits for each address

© tj

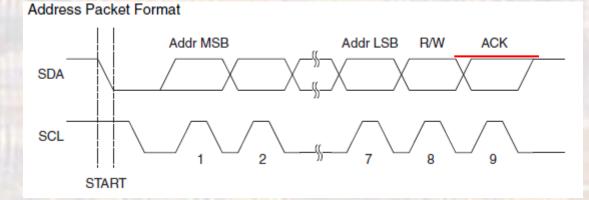

#### TWI Timing

- R/W bit indicates a read or write operation is to follow

- Read is active high

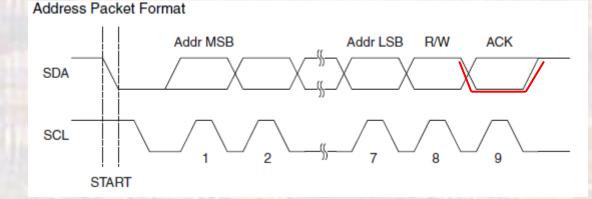

- ACK

- The master drives the data bus from start through the R/W bit and then releases the bus

- The slave then pulls down the bus in the last clock cycle to indicate a completed transmission

- TWI Timing

- ACK cont'd

- If the master fails to see the slave pull down the bus in the 9<sup>th</sup> clock cycle (NACK)

- Transmission failed

- Some sort of error action is required

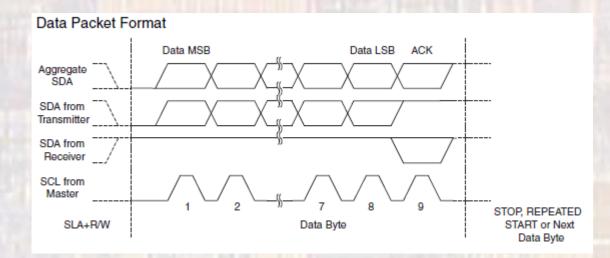

- TWI Timing

- Data packet

- After getting an ACK on the address data can be sent

- 8 bits of data

- 1 bit for a data ACK

- This can be repeated many times

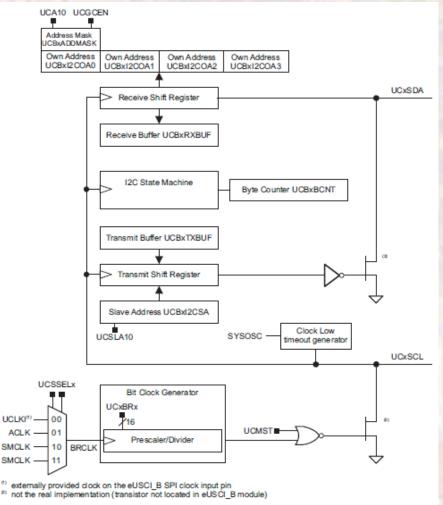

- TWI Implementation

- Separate RX/TX registers

- Separate RX/TX buffers

- State Machine

- Clock divider

- Control register

- Status register

Figure 24-1. eUSCI\_B Block Diagram – I<sup>2</sup>C Mode

TWI Addressing Modes

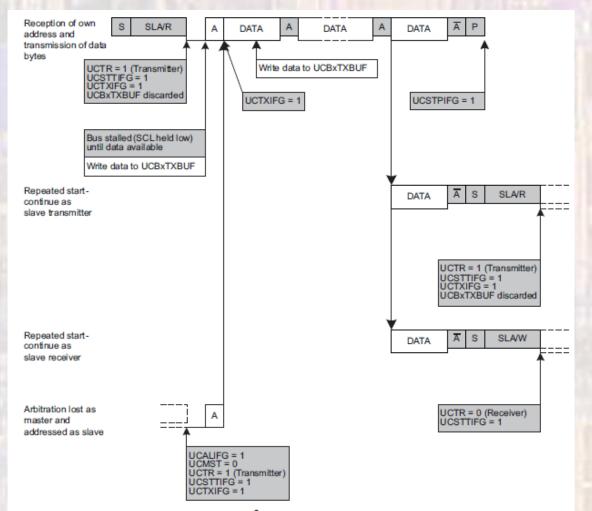

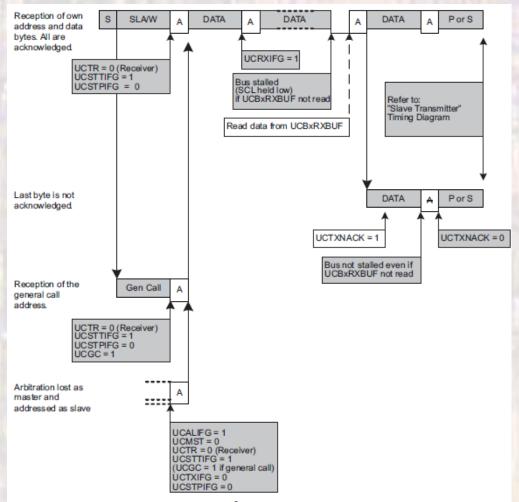

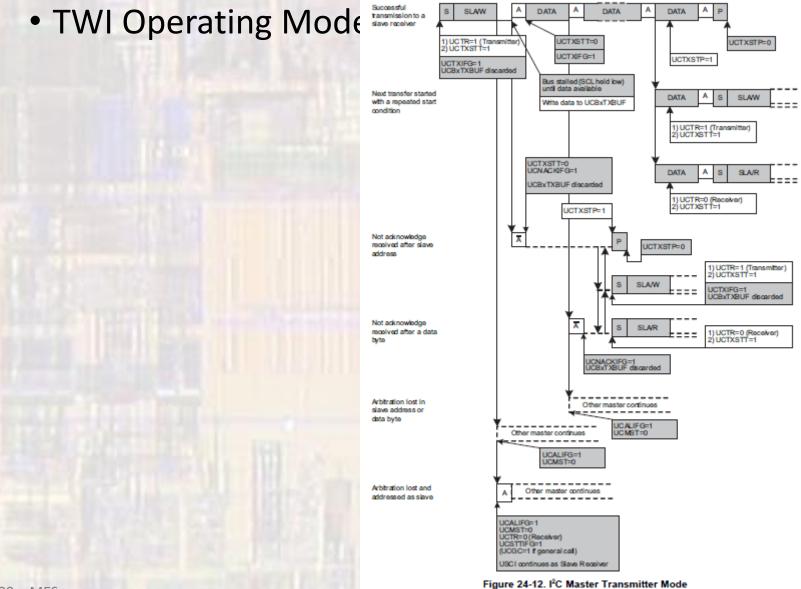

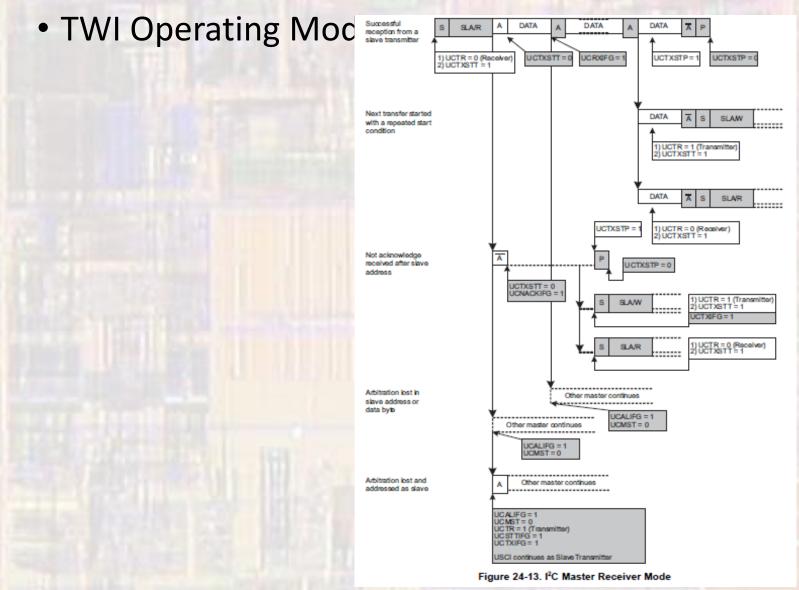

#### TWI Operating Modes

#### Figure 24-9. I<sup>2</sup>C Slave Transmitter Mode

#### TWI Operating Modes

#### Figure 24-10. I<sup>2</sup>C Slave Receiver Mode

© ti

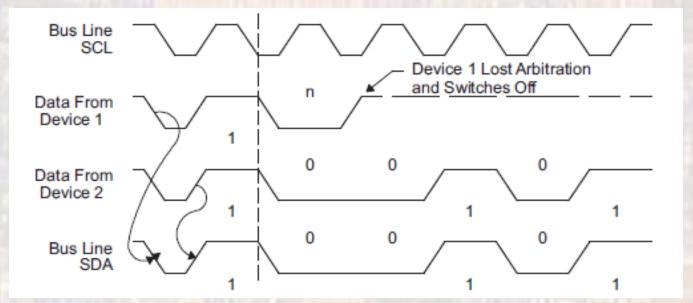

- TWI Multi-Master Arbitration

- First master that attempts to transmit a 1 when the other transmits a 0 loses arbitration and shuts off

#### Universal Synchronous/Asynchronous Receiver/Transmitter USART

- UART/USART

- Serial receiver / transmitter

- Asynchronous and Synchronous versions

- Asynchronous

- 2 pin interface

- RxD receive data pin

- TxD transmit data pin

- Clock recovery system

- Synchronous

- 3 pin interface

- RxD receive data pin

- TxD transmit data pin

- Xck Clock PD4

© tj

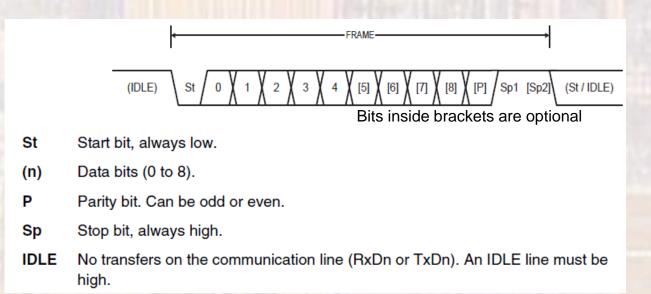

- UART Frame

- 1 start bit

- 5, 6, 7, 8, or 9 data bits typically LSB first

- none, even, or odd parity bit

- 1 or 2 stop bits,

- Overflow, Framing, Parity error detection

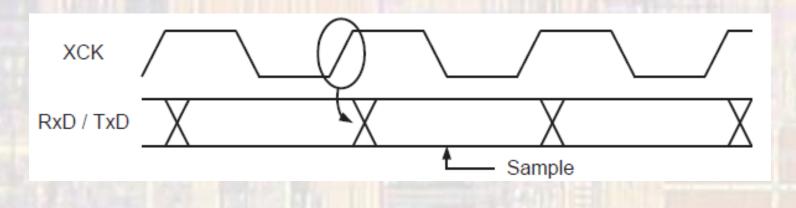

- UART Synchronous mode operation

- Master creates clock signal

- Xck max is typically Clk<sub>system</sub>/4 for timing purposes

- Master and Slave

- Transmit on one clock edge

- Receive (latch data) on the opposite clock edge

- UART Asynchronous mode operation

- Transmit is unchanged

- Xck is disabled

- No Master or Slave

- Must establish an agreed BAUD rate

- Max BAUD rate is typically Clk<sub>system</sub>/16

- Limited by HW clock selection options

- Fixed in SW

- Start at known BAUD rate and agree to go faster/slower

- Receiver circuitry includes:

- Clock recovery block

- Data recovery block

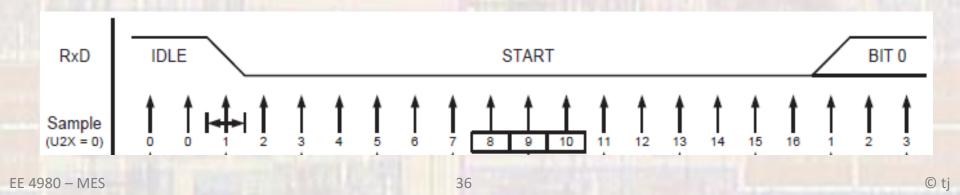

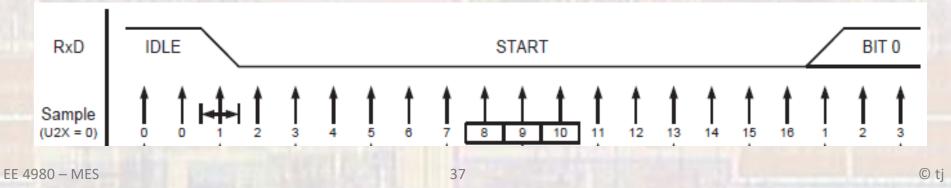

- UART Asynchronous mode operation

- Clock and Data recovery

- Internal clock at 16x BAUD rate

- Sample RxD signal with internal clock

- Detect Start bit falling edge

- Sample RxD after 8,9,10 internal clocks

- Majority determines bit value

- Assuming a valid start all further bits sampled at multiples of 16 clocks

- UART Multi-processor mode

- Multiple processors sharing the same USART signals

- Use the last bit in the data (e.g. bit 9 when using 8 bit data) to indicate an address or data value is in the frame

- If it is an address and it is your address, collect subsequent data frames

- If it is not your address, ignore subsequent data frames

- UART Error detection

- Parity

- Create an error if parity is wrong

- Overflow

- Create an error if new data is ready to be sampled and the last data has not been read from the buffer yet

- Double buffering is common

- Frame error

- Stop bit not detected when expected

- Idle not detected when expected

UART Common BAUD rates

| BAUD<br>Rate | Bit Width | Frame Length<br>start,8bit data,<br>parity, 1 stop | Data     | Rate      |

|--------------|-----------|----------------------------------------------------|----------|-----------|

|              | (us)      | (us)                                               | (Bits/s) | (Bytes/s) |

| 4800         | 208.33    | 2291.67                                            | 3,491    | 436       |

| 9600         | 104.17    | 1145.83                                            | 6,982    | 873       |

| 19200        | 52.08     | 572.92                                             | 13,964   | 1,745     |

| 38400        | 26.04     | 286.46                                             | 27,927   | 3,491     |

| 57600        | 17.36     | 190.97                                             | 41,891   | 5,236     |

| 115200       | 8.68      | 95.49                                              | 83,782   | 10,473    |

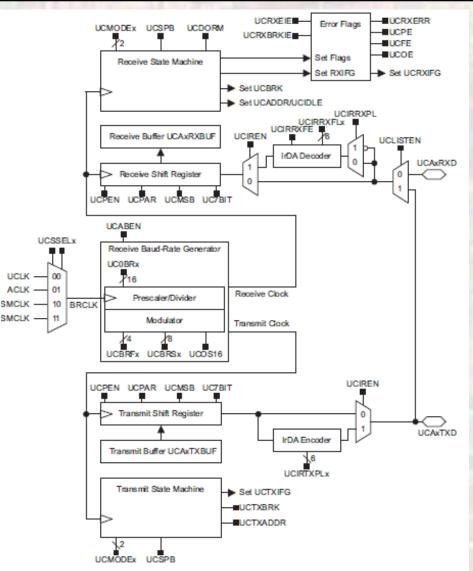

- MSP432 UART

Implementation

- Clock Selector

- Prescaler /baud rate generator

- RX/TX buffers

- RX//TX state machines

- Error detector

- Automatic baud rate detection

Figure 22-1. eUSCI\_Ax Block Diagram – UART Mode (UCSYNC = 0)

40

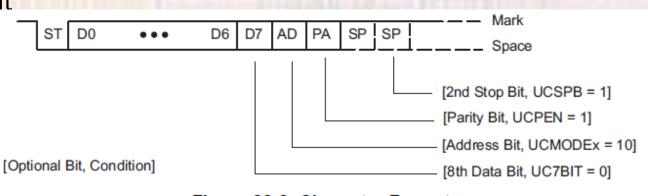

- MSP432 UART Implementation

- Required bits

- start

- Data 0-7

- Stop

- Optional bits

- data bit 8

- address bit (7 bit mode)

- parity bit

- 2<sup>nd</sup> stop bit

Figure 22-2. Character Format

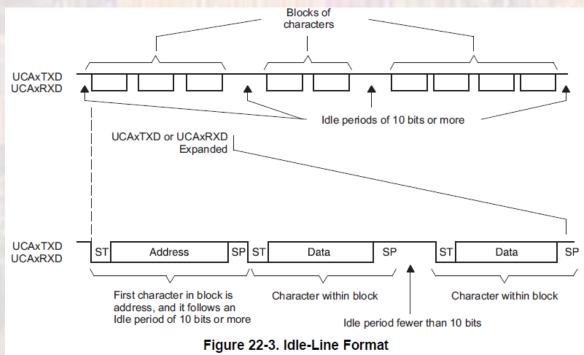

- MSP432 UART Implementation

- Idle Line Microprocessor Format

- Used when more than 2 devices share the signal paths

- Blocks of data separated by at least 10 sequential 1's after a stop

The first block of data following an idle time is an address

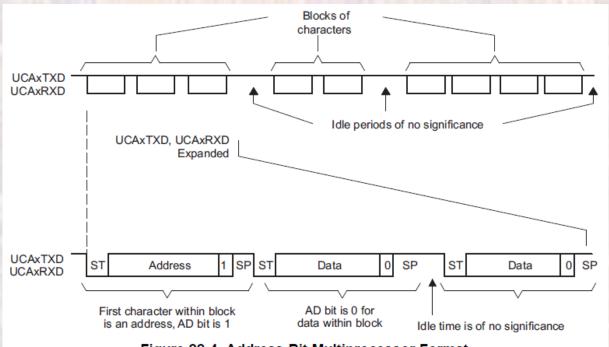

- MSP432 UART Implementation

- Address Bit Microprocessor Format

- Used when more than 2 devices share the signal paths

- The first block of data after a start contains an extra bit to indicate it is an address

#### Figure 22-4. Address-Bit Multiprocessor Format

- MSP432 UART Implementation

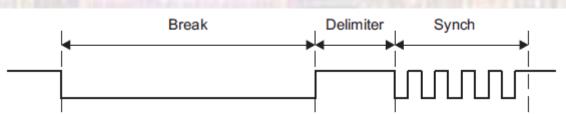

- Automatic baud rate detection

- Break -> delimiter -> sync pulses

- Baud rate is calculated based on the sync pulses

- Max = 1MBaud

- Min normal mode = 244 Baud

- Min low frequency mode = 15Baud

Figure 22-5. Auto Baud-Rate Detection – Break/Synch Sequence

- MSP432 UART Implementation

- Receive Error Detection

| Error Condition | Error Flag | Description                                                                                                                                                                                                                                                                           |  |

|-----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Framing error   | UCFE       | A framing error occurs when a low stop bit is detected. When two stop bits are used, both stop bits are checked for framing error. When a framing error is detected, the UCFE bit is set.                                                                                             |  |

| Parity error    | UCPE       | A parity error is a mismatch between the number of 1s in a character and the value of the parity bit. When an address bit is included in the character, it is included in the parity calculation. When a parity error is detected, the UCPE bit is set.                               |  |

| Receive overrun | UCOE       | An overrun error occurs when a character is loaded into UCAxRXBUF before the prior<br>character has been read. When an overrun occurs, the UCOE bit is set.                                                                                                                           |  |

| Break condition | UCBRK      | When not using automatic baud-rate detection, a break is detected when all data, parity, and stop bits are low. When a break condition is detected, the UCBRK bit is set. A break condition can also set the interrupt flag UCRXIFG if the break interrupt enable UCBRKIE bit is set. |  |

#### Table 22-1. Receive Error Conditions