Last updated 8/23/24

- Addition and subtraction are common functions in digital designs

- Long hand addition and subtraction is very tedious

- VHDL syntheses vendors have provided the ability to do addition and subtraction behaviorally

- Makes no sense for SLV just a collection of wires not supported

- Supported for signed and unsigned signals

- signed + signed

- unsigned + unsigned

- signed signed

- unsigned unsigned

- No overflow/underflow detection

- 4 bit unsigned : 12 + 12 → 8

### 4 bit unsigned adder

#### **Explicit Type Conversions**

```

adder_unsigned_4.vhdl

-- created 8/22/24

-- Adder example for the notes

-- inputs: 2 4 bit inputs

-- outputs: 4 bit output, carry out

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity adder_unsigned_4 is

port (

in std_logic_vector(3 downto 0);

in std_logic_vector(3 downto 0);

i_b :

out std_logic_vector(3 downto 0)

o_sum :

);

end entity:

architecture behavioral of adder_unsigned_4 is

-- type conversions

signal a_sig

: unsigned(3 downto 0);

signal b_sig

: unsigned(3 downto 0);

signal sum_sig : unsigned(3 downto 0);

-- input conversion

a_sig <= unsigned(i_a);</pre>

b_sig <= unsigned(i_b);</pre>

add : process(a_sig, b_sig)

sum_sig <= a_sig + b_sig;

end process;

-- output conversion

o_sum <= std_logic_vector(sum_sig);</pre>

end architecture;

```

#### **In-line Type Conversions**

```

adder_unsigned_4.vhdl

-- created 8/22/24

-- Adder example for the notes

-- inputs: 2 4 bit inputs

-- outputs: 4 bit output, carry out

library ieee:

use ieee std_logic_1164.all;

use ieee.numeric_std.all;

entity adder_unsigned_4 is

port (

in std_logic_vector(3 downto 0);

in std_logic_vector(3 downto 0);

out std_logic_vector(3 downto 0)

o_sum :

end entity:

architecture behavioral of adder_unsigned_4 is

begin

o_sum <= std_logic_vector(unsigned(i_a) + unsigned(i_b));</pre>

end architecture;

```

#### **Identical Results**

© ti

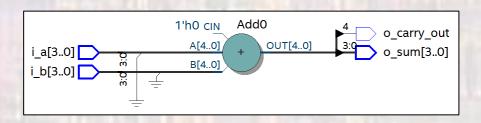

### 4 bit unsigned adder w/ carry out

```

adder_unsigned_co_4.vhdl

-- created 8/22/24

-- tj

-- Adder example for the notes

-- inputs: 2 4 bit inputs

-- outputs: 4 bit output, carry out

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity adder_unsigned_co_4 is

port (

in std_logic_vector(3 downto 0);

i_b :

in std_logic_vector(3 downto 0);

out std_logic_vector(3 downto 0);

o_carry_out : out std_logic

end entity;

architecture behavioral of adder_unsigned_co_4 is

-- type conversions

signal a_sig : unsigned(4 downto 0);

signal b_sig : unsigned(4 downto 0);

signal carry_sig : unsigned(4 downto 0);

-- temporary signal to overflow value

signal tmp_sig : unsigned(4 downto 0);

begin

-- input conversio

a_sig <= unsigned('0' & i_a);

b_sig <= unsigned('0' & i_b);</pre>

add: process(a_sig, b_sig)

tmp_sig <= a_sig + b_sig;</pre>

end process;

-- output conversion

o_sum <= std_logic_vector(tmp_sig(3 downto 0));</pre>

o_carry_out <= tmp_sig(4);

end architecture:

```

### N bit unsigned adder

```

-- adder_unsigned_n.vhdl

-- created 8/22/24

-- tj

-- Adder example for the notes

1'h0 cin

Add0

-- inputs: 2 N bit inputs

A[7..0]

OUT[7..0]

-- outputs: N bit output

i a[7..0]

o sum[7..0]

B[7..0]

i b[7..0]

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity adder_unsigned_n is

generic(

natural := 8

in std_logic_vector((N - 1) downto 0);

in std_logic_vector((N - 1) downto 0);

out std_logic_vector((N - 1) downto 0)

o_sum :

end entity;

architecture behavioral of adder_unsigned_n is

begin

o_sum <= std_logic_vector(unsigned(i_a) + unsigned(i_b));</pre>

end architecture;

```

N bit unsigned subtractor

```

Add0

1'h0 cin

-- subtractor_unsigned_n.vhdl

A[8..0]

OUT[8..0]

o diff[7..0]

-- created 8/22/24

i minuend[7..0]

B[8..0]

-- ti

i subtrahend[7..0]

-- subtractor example for the notes

subtract

\rightarrow

minuend & 1

a bcde fgh1

-- inputs: 2 N bit inputs

~(subtrahend & 1)

j klmn opg0

-- outputs: N bit output

r stuv wxv1

library ieee;

use ieee std_logic_1164.all;

use ieee.numeric_std.all:

diff

entity subtractor_unsigned_n is

generic(

N : natural := 8

subtract

Shift and concatenate 1

2x + 1

in std_logic_vector((N - 1) downto 0);

in std_logic_vector((N - 1) downto 0);

i_minuend :

i_subtrahend :

Shift and concatenate 1 +

^{\sim}(2y) + 1

out std_logic_vector((N - 1) downto 0)

o_diff :

2x - 2v

end entity:

architecture behavioral of subtractor_unsigned_n is

Only select upper bits \rightarrow /2

X - V

begin

o_diff <= std_logic_vector(unsigned(i_minuend) - unsigned(i_subtrahend));

end architecture;

```