Last updated 2/8/24

- Used as individual blocks

- Used inside a block

- Timers delays, time-out, ...

- Collectors cash, presses, ...

- Variations

- Up, Down, Up-Down

- Wrapping, non-wrapping

- Modulo

- Fixed size, n-bit

- Fixed increment, m-increment

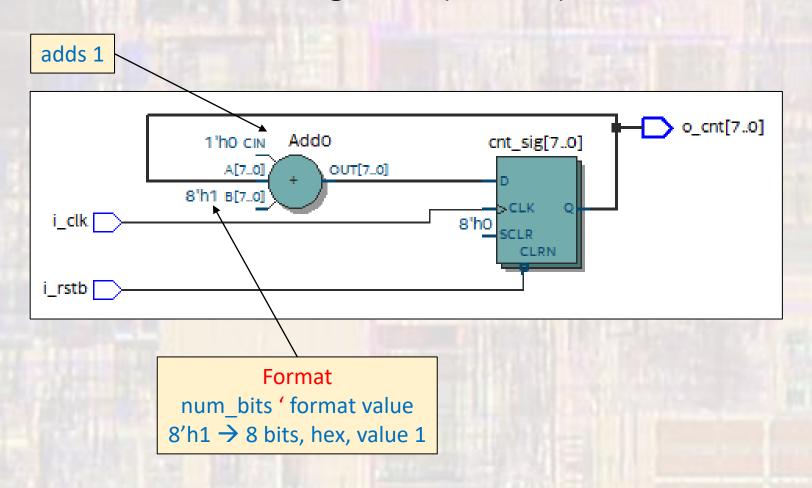

#### Counter - n bit - unsigned

```

-- counter_unsigned_n_bit.vhdl

created 2/29/17

-- ti

-- rev 0

-- n bit unsigned up-counter example

-- Inputs: rstb, clk

-- Outputs: cnt[7:0]

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity counter_unsigned_n_bit is

qeneric(

N: natural := 8

port (

i_clk : in std_logic;

in std_logic;

i_rstb :

o_cnt : out std_logic_vector((N - 1) downto 0)

end entity:

```

```

architecture behavioral of counter_unsigned_n_bit is

-- internal signals

signal cnt_sig: unsigned((N - 1) downto 0);

begin

why?

counter: process(i_clk, i_rstb)

begin

2 - reasons

-- reset

if (i_rstb = '0') then

cnt_sig <= (others => '0');

-- rising clk edge

elsif (rising_edge (i_clk)) then

cnt_sig <= cnt_sig + 1;</pre>

end if:

end process;

-- Output logic

cast

o_cnt <= std_logic_vector(cnt_sig);</pre>

end behavioral;

```

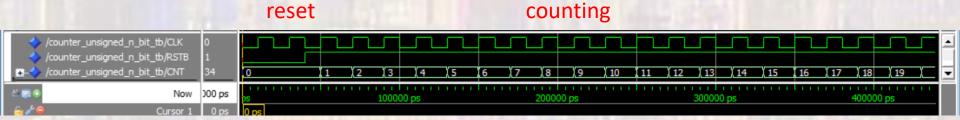

Counter - n bit – unsigned – (default)

- Counter n bit unsigned

- Testbench 6 bit version

```

architecture testbench of counter_unsigned_n_bit_tb is

signal CLK: std_logic;

signal RSTB: std_logic;

signal CNT: std_logic_vector((NUM_BITS - 1) downto 0);

constant PER: time:= 20 ns;

-- Component prototype

COMPONENT counter_unsigned_n_bit

generic(

N: natural := 4

PORT

i_rstb : IN STD_LOGIC;

i_clk : IN STD_LOGIC;

o_cnt : OUT STD_LOGIC_vector((N - 1) downto 0)

END COMPONENT:

-- Device under test (DUT)

DUT: counter_unsigned_n_bit

generic map(

N => NUM_BITS

port map(

i_rstb => RSTB,

i_clk => CLK,

o_cnt => CNT

);

```

```

-- Test processes

-- Clock process

clock: process -- no sensitivity list allowed

begin

CLK <= '0';

wait for PÉR/2;

infinite: loop

CLK <= not CLK; wait for PER/2;

end loop:

end process clock;

-- Reset process

reset: process -- no sensitivity list allowed

RSTB <= '0'; wait for 2*PER;

RSTB <= '1'; wait;

end process reset:

-- Run Process

-- empty

-- End test processes

end architecture;

```

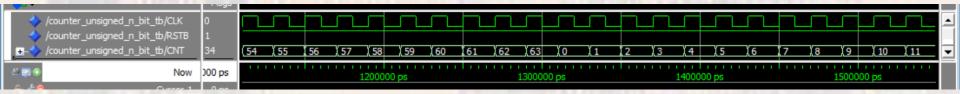

- Counter n bit unsigned

- Testbench 6 bit version

#### wrap

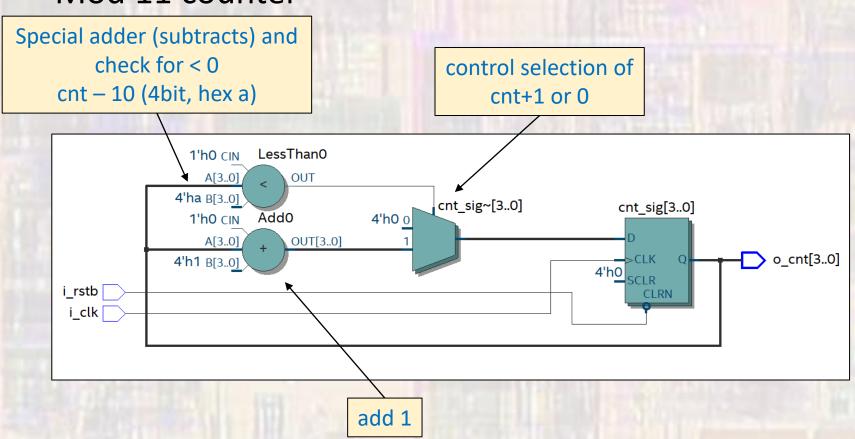

# Mod counter

MOD x counts x times Range 0 - (x - 1)

- Mod 11 counter

- Mod 11 only needs to compare 4 bits, no need to optimize the roll over test

```

-- counter_mod_11.vhdl

-- created 3/17/17

-- tj

-- rev 0

-- mod 11 counter example

-- Inputs: rstb, clk

-- Outputs: cnt[3:0]

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity counter_mod_11 is

port (

i_clk : in std_logic;

i_rstb : in std_logic;

o_cnt : out std_logic_vector(3 downto 0)

);

end entity:

```

```

architecture behavioral of counter_mod_11 is

-- internal signals

signal cnt_sig: unsigned(3 downto 0);

begin

count: process(i_clk, i_rstb)

begin

-- reset

if (i_rstb = '0') then

cnt_sig <= (others => '0');

Why < 10

-- rising clk edge

elsif (rising_edge(i_clk)) then

if (cnt_sig < 10) then \blacktriangleleft

cnt_sig <= cnt_sig + 1;</pre>

cnt_sig <= (others => '0');

end if:

end if;

end process:

-- Output logic

o_cnt <= std_logic_vector(cnt_sig);</pre>

end behavioral:

© ti

```

ELE 3510 8 end be

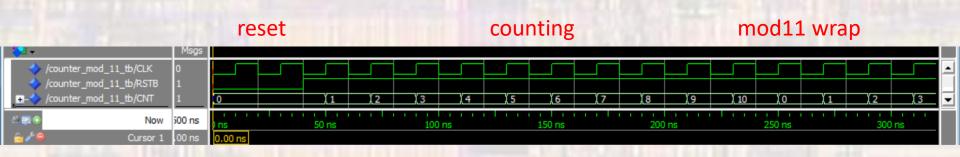

#### Mod 11 counter

- Mod 11 counter

- Testbench results

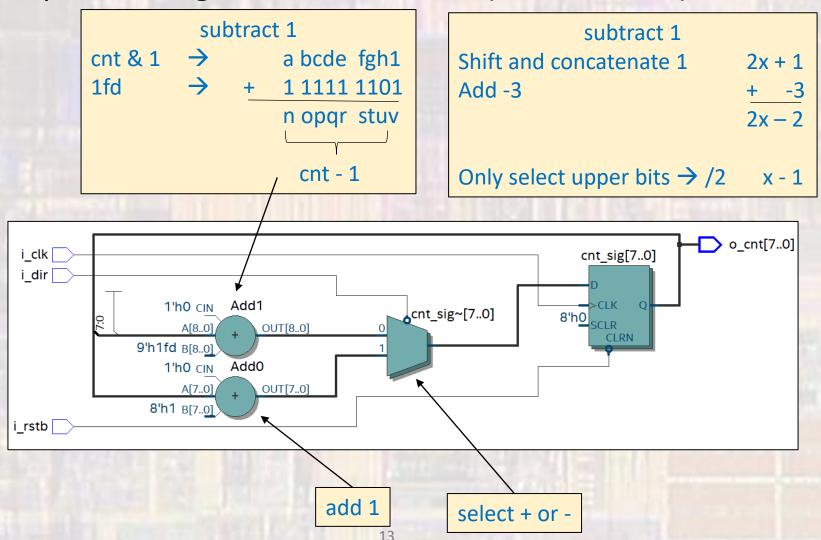

#### up/down signed n-bit counter

```

-- counter_updn_signed_nb.vhdl

-- created 2/29/17

-- ti

-- rev 0

-- n bit up/down signed counter example

-- Inputs: rstb, clk, dir

-- Outputs: cnt[n-1:0]

-- counts up when dir = 0

-- counts down when dir = 1

library ieee;

use ieée std_logic_1164.all;

use ieee.numeric_std.all;

entity counter_updn_signed_nb is

generic(

N: natural := 8

i_clk: in std_logic;

i_rstb: in std_logic;

i_dir: in std_logic;

o_cnt : out std_logic_vector((N - 1) downto 0)

end entity;

```

```

architecture behavioral of counter_updn_signed_nb is

-- internal signals

signal cnt_sig: signed((N - 1) downto 0);

begin

count: process(i_clk, i_rstb)

begin

-- reset

if (i_rstb = '0') then

cnt_sig <= (others => '0');

-- rising clk edge

elsif (rising_edge(i_clk)) then

if(i_dir = '0') then

cnt_sig <= cnt_sig + 1;

cnt_sig <= cnt_sig - 1;</pre>

end if:

end if:

end process;

-- Output logic

o_cnt <= std_logic_vector(cnt_sig);</pre>

end behavioral:

```

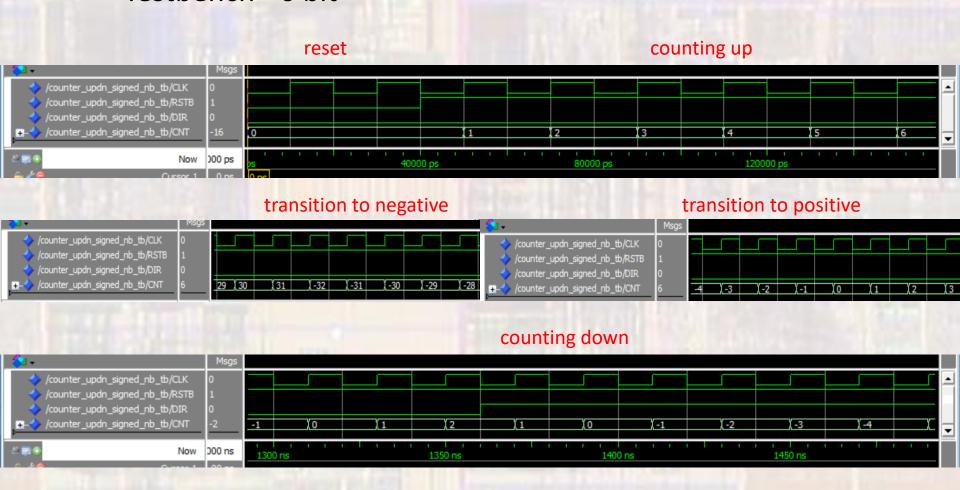

up/down signed n-bit counter (default 8 bit)

© ti

**ELE 3510**

up/down signed n-bit counter

signal

signal

signal

signal CLK: std\_logic;

RSTB: std\_logic;

DIR: std\_logic;

Testbench - 6 bit test

```

constant PER: time:= 20 ns;

-- Component prototype

COMPONENT counter_updn_signed_nb

generic(

N: natural := 8

i_clk: in std_logic;

i_rstb: in std_logic;

i_dir: in std_logic;

o_cnt : out std_logic_vector((N - 1) downto 0)

END COMPONENT:

-- Device under test (DUT)

DUT: counter_updn_signed_nb

deneric map(

n => NUM_BITS

CNT

DUT

port map(

=> CLK,

=> RSTB

=> DIR.

o_cnt

=> CNT

```

architecture testbench of counter\_updn\_signed\_nb\_tb is

CNT: std\_logic\_vector((NUM\_BITS - 1) downto 0);

```

-- Test processes

-- Clock process

clock: process -- no sensitivity list allowed

begin

CLK <= '0';

wait for PER/2:

infinite: loop

CLK <= not CLK; wait for PER/2;

end process clock;

-- Reset process

reset: process -- no sensitivity list allowed

RSTB <= '0'; wait for 2*PER;

RSTB <= '1'; wait;

end process reset:

-- Run Process

-- no sensitivity list allowed

run: process

-- initialize inputs

DIR <= '0':

-- run code

wait for 68*PER;

DIR <= '1';

wait for 68*PER;

end process run:

-- End test processes

end architecture;

```

run

clock

**RSTB**

DIR

- up/down signed n-bit counter

- Testbench 6 bit