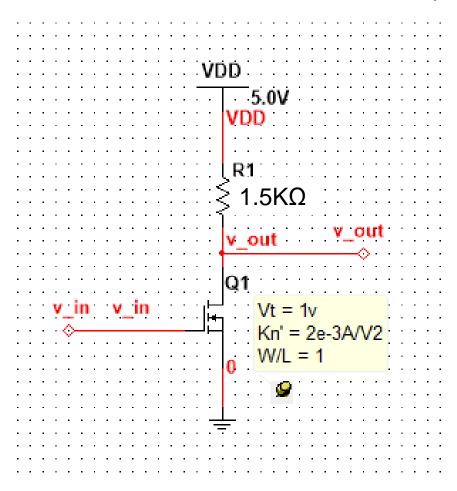

1 – Analysis: Create a table of the calculated expected output voltages for v\_in from 0V to 5V in 0.5V increments.

40pts

Note: be sure to confirm the NMOS operating region

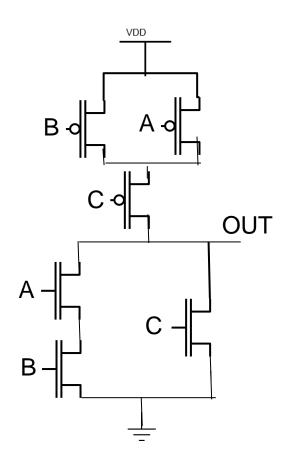

2 – Create a truth table and a SOP or POS logic equation for the circuit below .

This is called a compound gate.

30pts

| A | В | С | OUT |

|---|---|---|-----|

|   |   |   |     |

|   |   |   |     |

|   |   |   |     |

|   |   |   |     |

|   |   |   |     |

|   |   |   |     |

|   |   |   |     |

|   |   |   |     |

3 – Use DeMorgan's theorem to reduce the logic equation in problem 2.

Implement the solution with NANDs, NORs, and Inverters. Compare the 6-transistor solution in problem 2 to your solution above with respect to area and speed