# Measuring Logic Components

# Last modified 1/13/25

# Measuring Logic Components

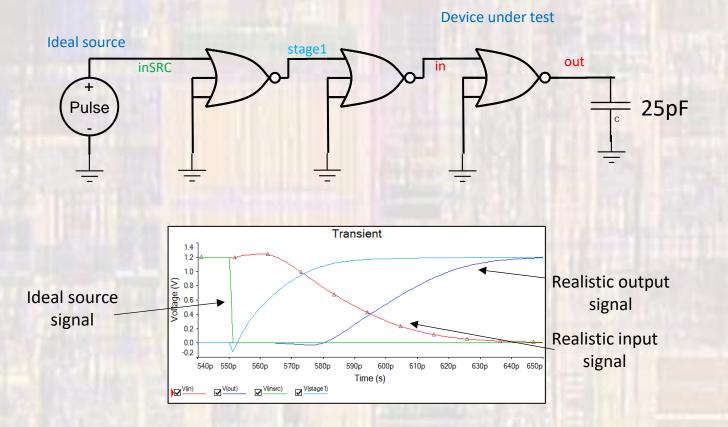

#### Source Effects

- Need to guard against source effects in both simulation and lab testing

- Ideal sources do not exist in real designs

- Unlimited current

- No over/under shoot

- No limits on slew rate

- Load Effects

- The standard for measuring gate delays differs for:

- Designs using discrete parts on a PCB

- Use a fixed load capacitance (10pF, 25pF, 50pf)

- Integrated circuit designs

- Use one input from a minimum 2 input NAND gate

© ti

# Measuring Logic Components

- Discrete: Isolate the source Provide a load

- Chain gates of the same type to isolate the source

Example Input for 3 input NOR

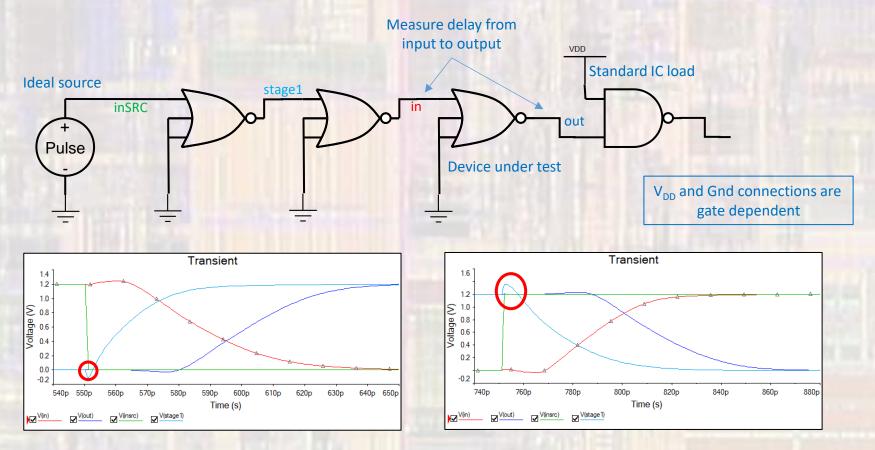

# Measuring Logic Components

- Integrated: Isolate the source standard load

- Chain gates of the same type to isolate the source

Example test for 3 input NOR (IC method)