#### Last updated 7/18/23

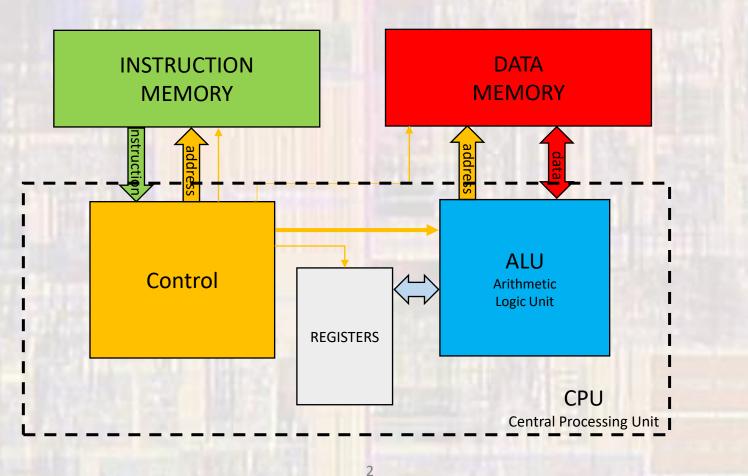

Generalized Structure

- Instruction Set

- Instruction Set Architecture ISA

- Arithmetic Instructions

- Add

- Subtract

- Less Than

- Logical Instructions

- AND

- OR

- NOR

- ALU Implementation

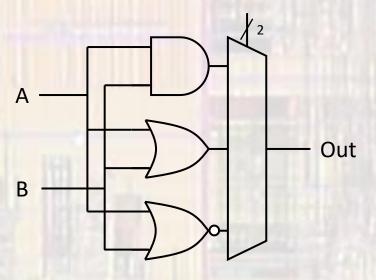

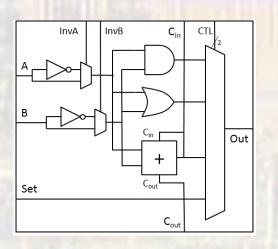

- Logical Instructions

- AND, OR, NOR

- 2 inputs A and B

- 1 output

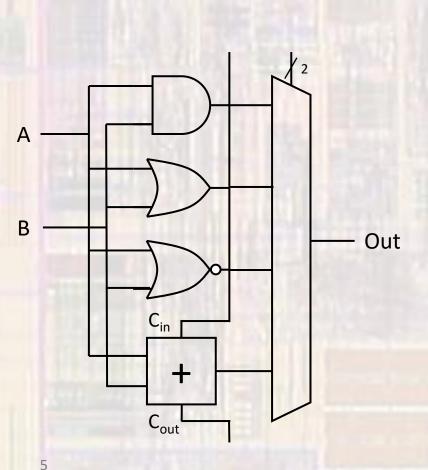

- ALU Implementation

- Arithmetic Instructions

- ADD

- Inputs: A, B, C<sub>in</sub>

- Outputs: Out, C<sub>out</sub>

6

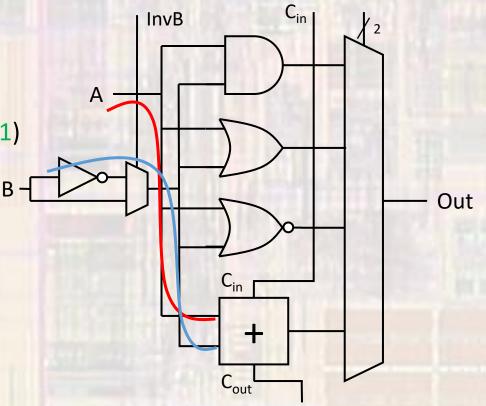

- ALU Implementation

- Arithmetic Instructions

- SUB (2's complement)

- A B = A + (-B)

- =  $A + (\overline{B} + 1)$

- Invert B and add 1 (C<sub>inB0</sub>=1)

- Inputs: A, <mark>B, C<sub>in</sub></mark>

- Outputs: Out, C<sub>out</sub>

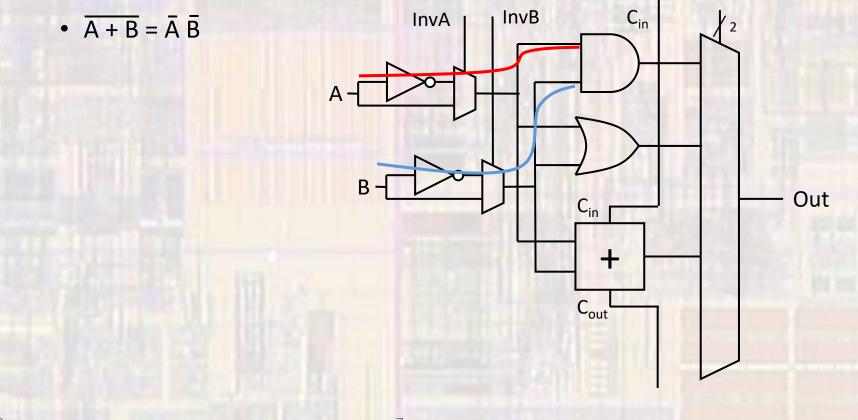

- ALU Implementation

- Revisit NOR

- ALU Implementation

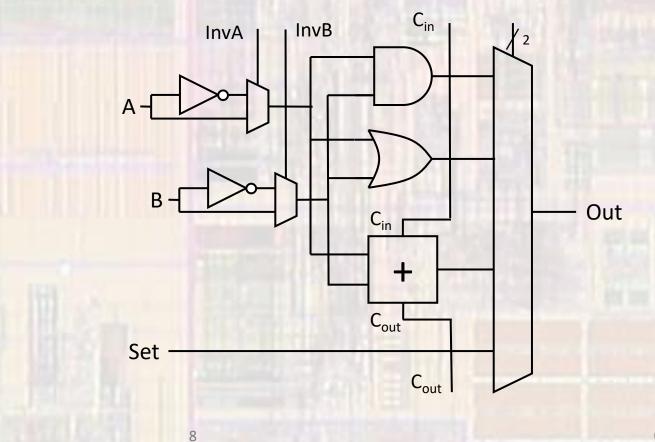

- Pre-plan for set function

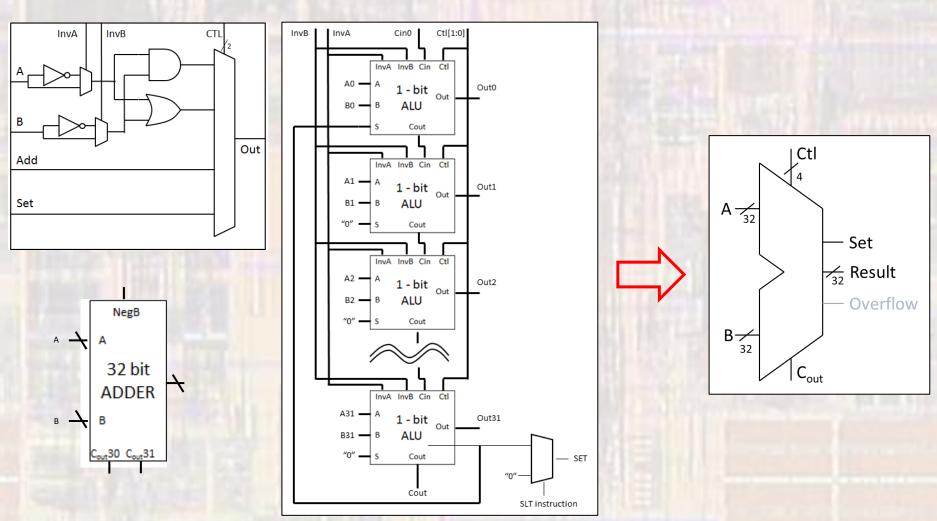

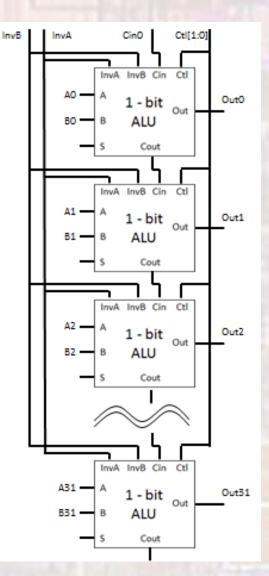

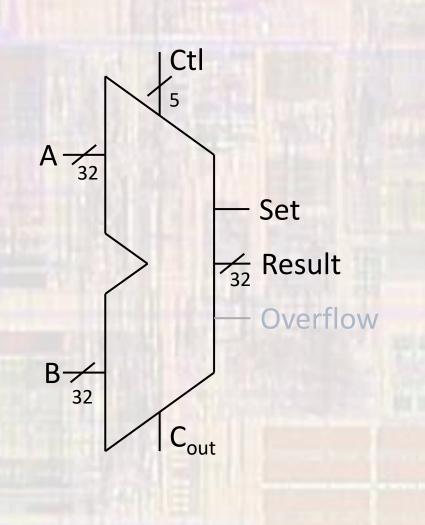

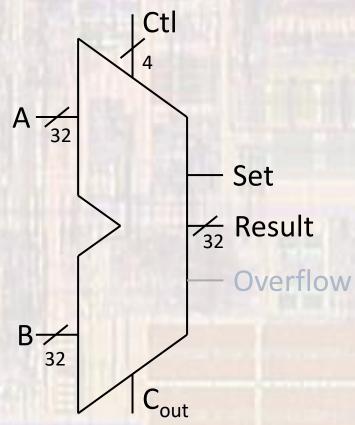

ALU - Implementation

• 32 bits

© tj

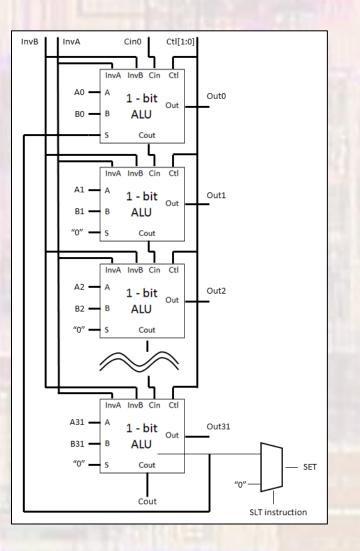

- ALU Implementation

- Determine if A < B

- $A < B \rightarrow (A B) < 0 \rightarrow negative answer$

- Subtraction is implemented by addition

- $A B \rightarrow A + B + 1$

- MSB indicates sign in 2's complement arithmetic

- MSB = 1  $\rightarrow$  negative number

- MSB =  $0 \rightarrow \text{positive number}$

- Set On Less Than instruction

- Use Adder MSB for SLT signal

- If A < B: Out[31:1] = 0, Out[0] = 1

- If A ≥ B: Out[31:0] = 0, Out[0] = 0

- SET = 1

© tj

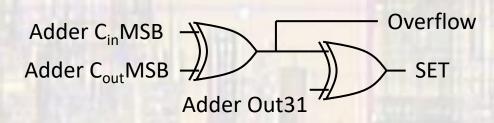

- ALU Implementation

- Set On Less Than cont'd

- Not implementing MSB after subtraction indicates sign

- MSB = 1  $\rightarrow$  negative number

- MSB =  $0 \rightarrow \text{positive number}$

- Exception: Subtraction (addition) is not valid if overflow occurs If overflow occurs, MSB is wrong sign SET becomes MSB xor OVERFLOW

ALU - Implementation

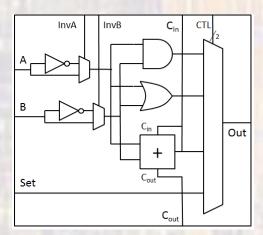

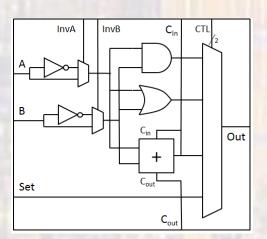

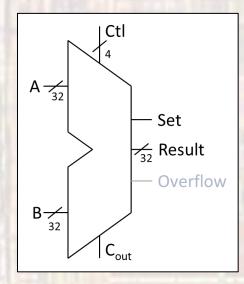

- ALU Implementation

- Control

- invA

- invB

- Cin

- ctl[1:0]

ALU – Implementation

|            | Operation | invA | invB | Cin | ctl[1] | ctl[0] |

|------------|-----------|------|------|-----|--------|--------|

|            | AND       | 0    | 0    | х   | 1      | 1      |

| DeMorgan   | OR        | 0    | 0    | х   | 1      | 0      |

|            | NOR       | 1    | 1    | х   | 1      | 1      |

| Addition - | ADD       | 0    | 0    | 0   | 0      | 1      |

|            | SUB       | 0    | 1    | 1   | 0      | 1      |

|            | SLT       | 0    | 1    | 1   | 0      | 0      |

What other logic function do we get for free

- ALU Implementation

- Note: C<sub>in</sub> and invB can always be the same → combine (negB)

#### Reduces control lines to 4

| Operation | invA | negB | ctl[1] | ctl[0] |

|-----------|------|------|--------|--------|

| AND       | 0    | 0    | 1      | 1      |

| OR        | 0    | 0    | 1      | 0      |

| NOR       | 1    | 1    | 1      | 1      |

| ADD       | 0    | 0    | 0      | 1      |

| SUB       | 0    | 1    | 0      | 1      |

| SLT       | 0    | 1    | 0      | 0      |

© ti

- ALU Implementation

- 3 out of 6 instructions involve addition

Current implementation is very slow – why?

|          | Operation | invA | negB | ctl[1] | ctl[0] |

|----------|-----------|------|------|--------|--------|

|          | AND       | 0    | 0    | 1      | 1      |

|          | OR        | 0    | 0    | 1      | 0      |

|          | NOR       | 1    | 1    | 1      | 1      |

| Г        | ADD       | 0    | 0    | 0      | 1      |

| Addition | SUB       | 0    | 1    | 0      | 1      |

|          | SLT       | 0    | 1    | 0      | 0      |

#### Enhanced Adder