Last updated 7/18/23

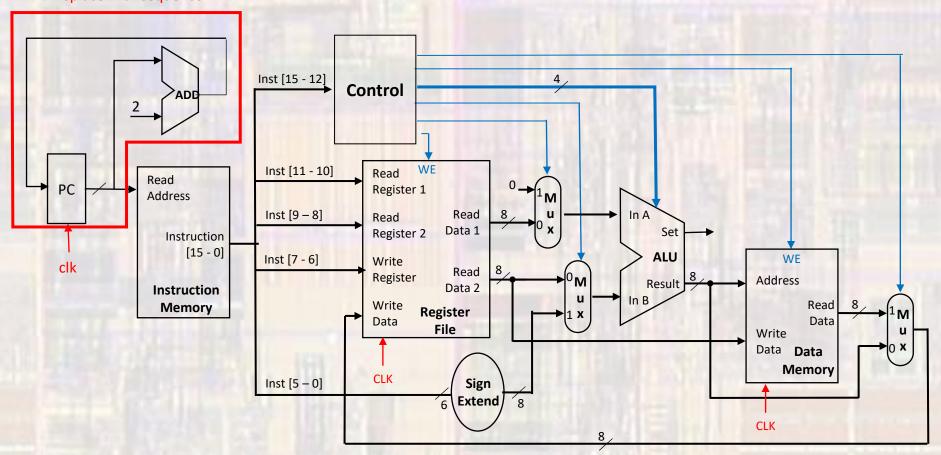

#### Instruction Format

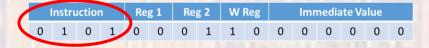

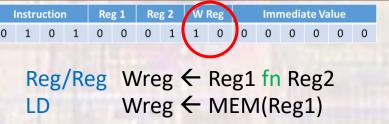

| Instruction                                   |                                                      | Reg 1 | Reg 2    | W Reg | Immediate Value                   |

|-----------------------------------------------|------------------------------------------------------|-------|----------|-------|-----------------------------------|

| or<br>and<br>nor<br>nand<br>add<br>sub<br>slt | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110 |       | > Reg/Re | eg    | Wreg ← Reg1 fn Reg2               |

| ld<br>st<br>ldi                               | 1000<br>1001<br>1100                                 |       | > MEM    |       | Wreg ← MEM(Reg1) MEM(Reg1) ← Reg2 |

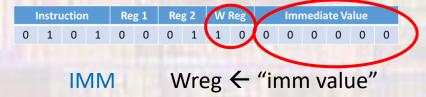

| nop                                           | 1111                                                 |       | - IMM    |       | Wreg ← "imm value"                |

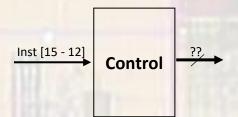

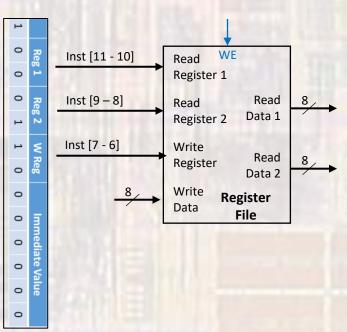

- Decode / Register Access

- Instruction Decode

- Logic to decode the instruction

- Pull off the relevant bits from the instruction

Create logic to drive control signals to other blocks

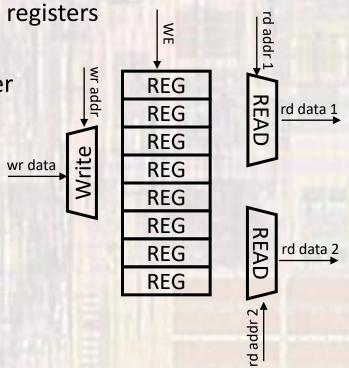

Decode / Register Access

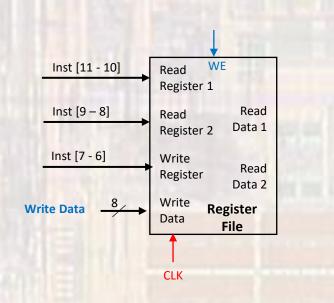

- Register File

- Series of registers

- 2 read multiplexors to select one of the registers for one of 2 outputs

- Write multiplexor to choose one register to write to

- Write data input

- Write enable (or WE\_b)

ELE 3510 4 © tj

- Decode / Register Access

- Register File implementation comments

- Instruction bit mapping to select registers

- Wire specific bits from the instruction to the address ports of the register file.

- 4 registers → 2 bits of address

- Each register 8 bits wide

- No rstb signal

ELE 3510 5 © tj

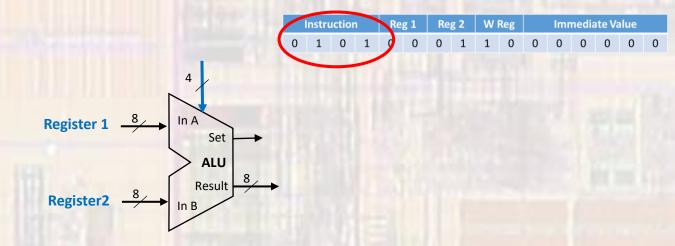

- Execute

- ALU executes all arithmetic and logical instructions

- Inputs are Register outputs

- Control is decoded from instructions

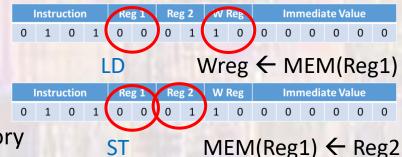

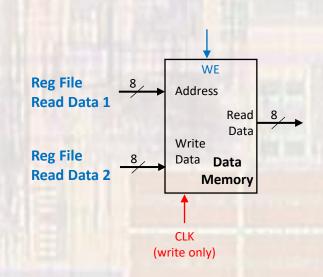

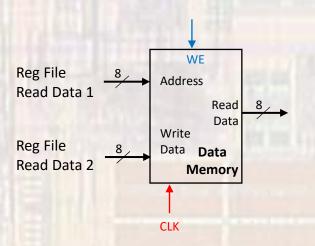

- Memory Access

- Load / Store Instructions

- R/W from registers to data memory

- Address

- Pre-stored in one of the registers

- Accessed from reg file "Read Data 1"

- Added to the immediate value in the instruction (zeros)

- Write Data

- Pre-stored in one of the registers

- Accessed from reg file "Read Data 2"

- Synchronous

- Read Data

- Asynchronous read

© ti

- Memory Access

- Data memory implementation comments

- Inferred RAM

- ?? in a x8 configuration

- → asynchronous address

- → asynchronous read

- → synchronous write

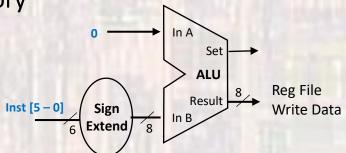

Memory Access

- Load Immediate Instruction

- Load a register from the program memory

- Value

- Stored in the instruction

- Sign-extended from 6 bits to 8 bits

- OR'd with zero in the ALU

- Uses the writeback mechanism to store the value in a register

© ti

Write Back

- Write results or memory value back to a register

- Write data

- Comes from ALU (result or Idi)

or

- Comes from data memory (Id)

- Synchronous

- Missing Pieces

- Program control elements

- Branches

- Jumps

- Hazards

#### Full Data path

Replace with sequencer