Last updated 7/18/23

- Processor Architecture

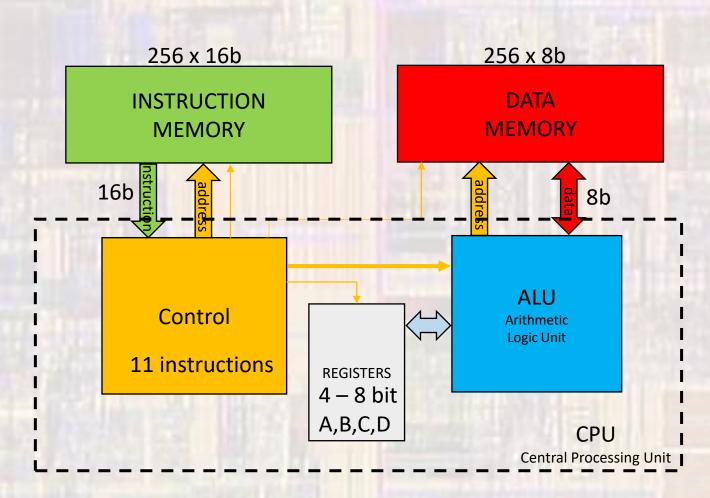

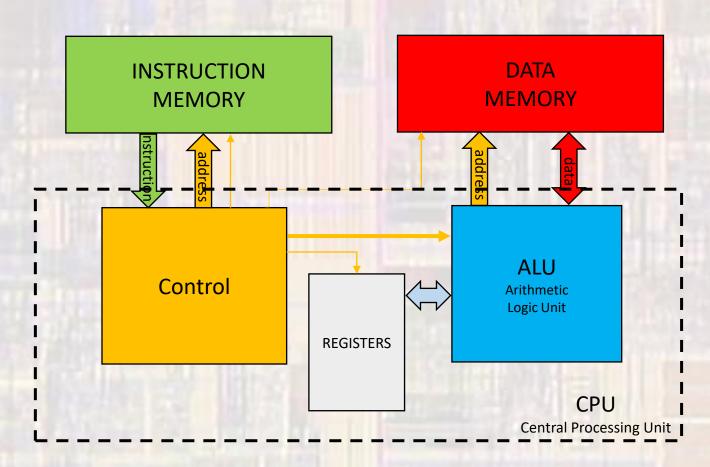

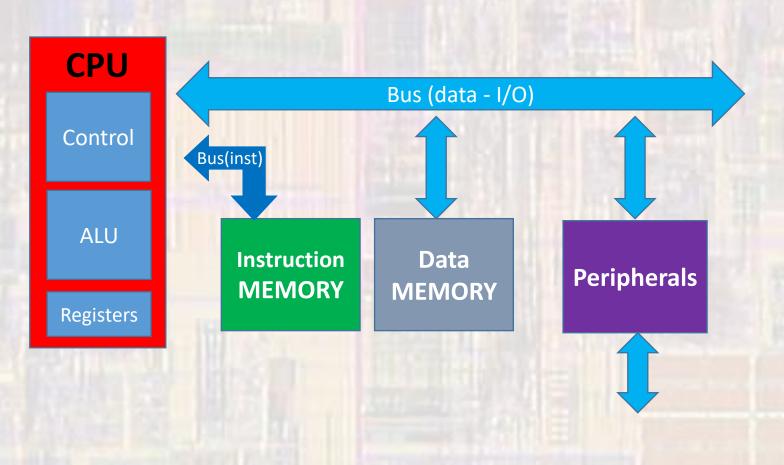

- Harvard separate Instruction and Data memory paths

- RISC Instruction set

- 2 basic types of instructions

- Register based instructions

- Memory instructions

- Register Instructions

- Only require access to the internal registers

- Arithmetic

- Logical

- Control

- Memory Operations

- Read or write to memory/registers

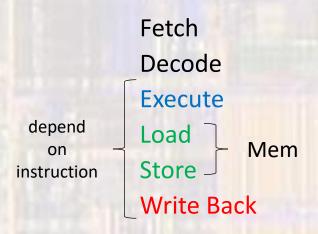

#### Instruction Execution

get next instruction from instruction memory determine what the instruction is if necessary – do what the instruction requires if necessary – get value from data memory if necessary – place value in data memory if necessary – store result in register

- Instruction Sequencing

- Program Counter (PC)

- Register that holds the NEXT instruction memory location to be fetched

- Provides the address for the instruction memory read

- Typically the register is incremented each clock cycle

- Incremented by the size of an instruction

- e.g. for a 16 bit instruction word the PC would be incremented by 2

- Instruction Sequencing

- Program control

- Linear flow increment PC normally

- Function call

- Store the "planned" next instruction address somewhere

- Place the first instruction address for the function in the PC

- Execute linearly in the function until done

- Restore the "planned" next instruction address

### Single Cycle Processor

• 1 line of code

#### Intro

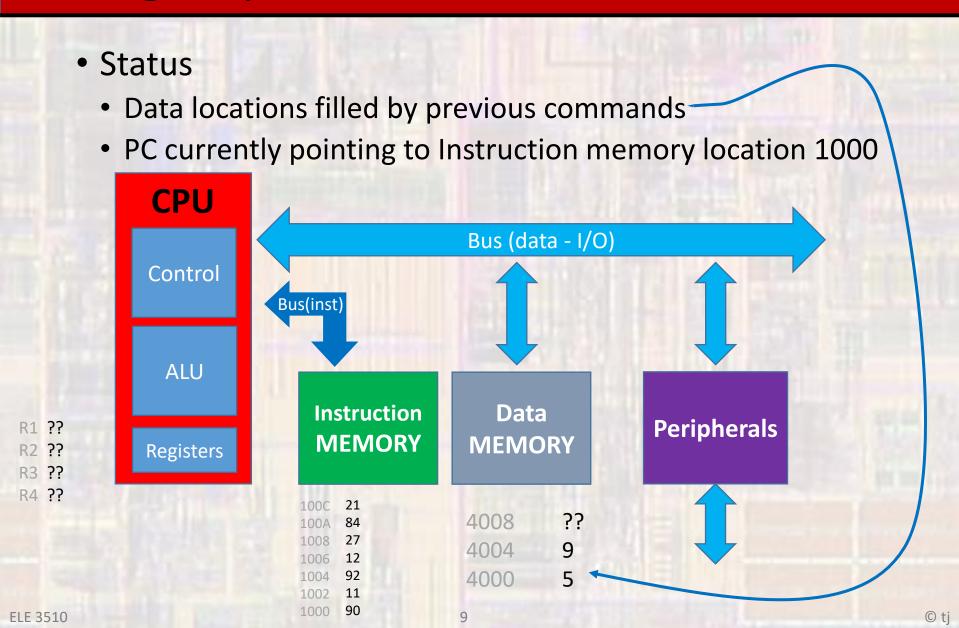

The compiler has assigned

- b to memory location 4000

- c to memory location 4004

- a to memory location 4008

$$a = b + c;$$

The compiler turned the single line into 7 instructions

| Mem loc | Instruction    | Encoding | action                         |

|---------|----------------|----------|--------------------------------|

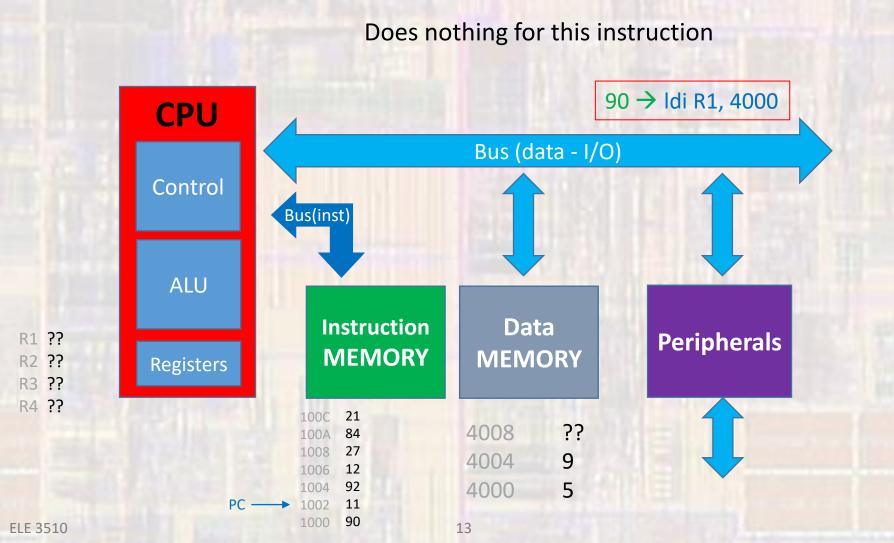

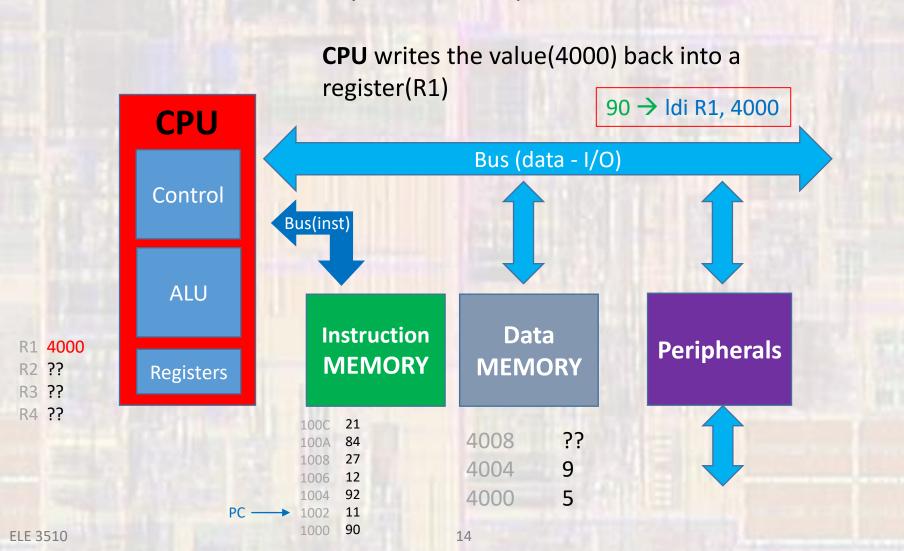

| 1000    | ldi R1, 4000   | 90       | Load loc for B into R1         |

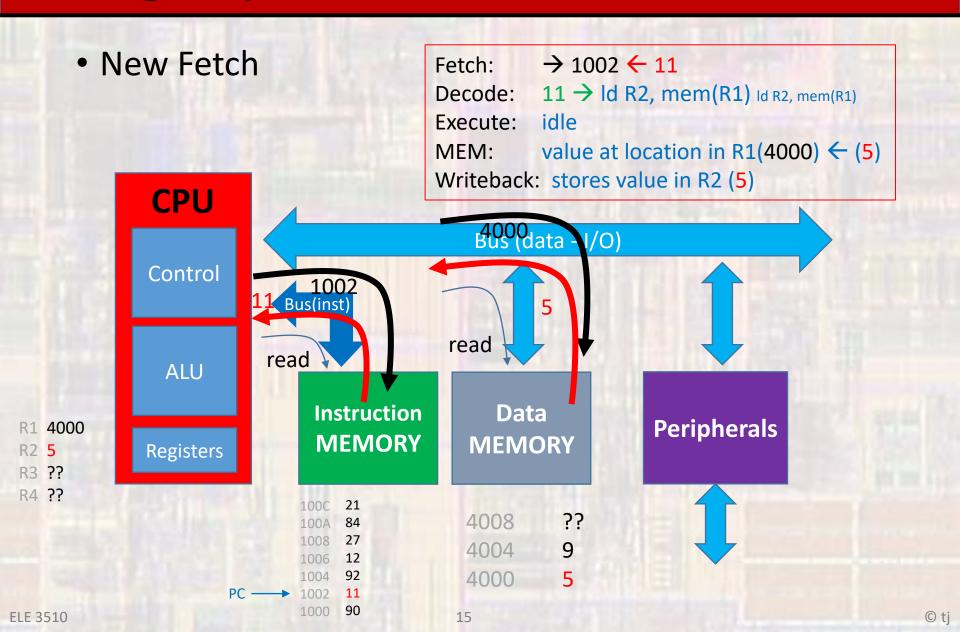

| 1002    | ld R2, mem(R1) | 11       | Put value at loc for B in R2   |

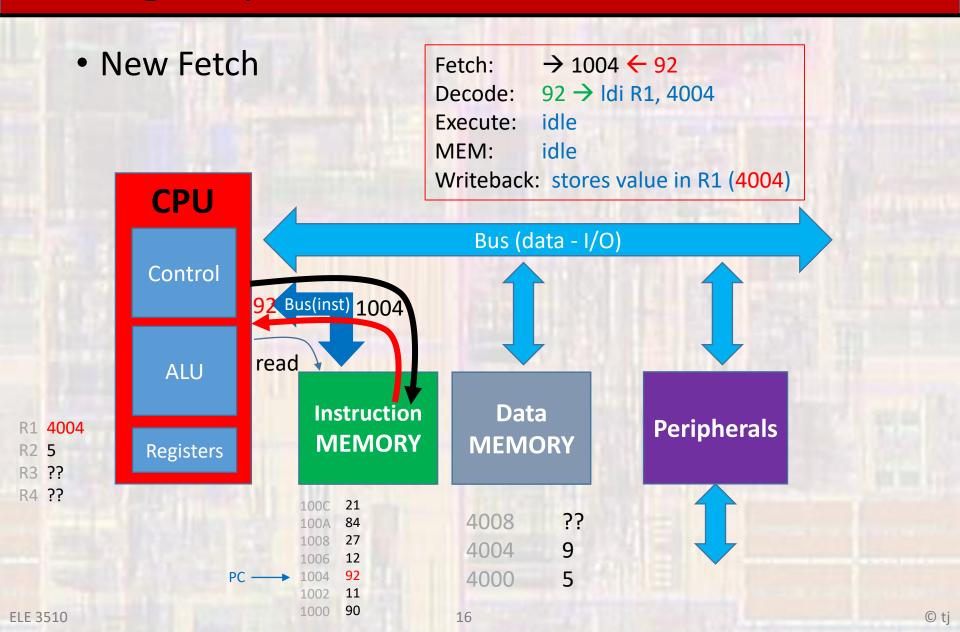

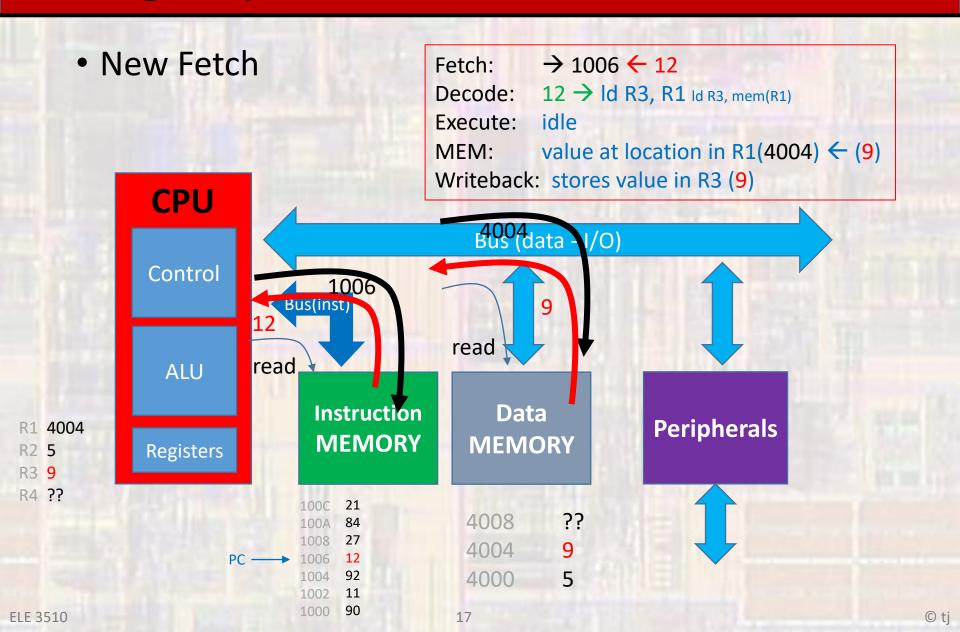

| 1004    | ldi R1, 4004   | 92       | Load loc for C into R1         |

| 1006    | ld R3, mem(R1) | 12       | Put value at loc for C in R3   |

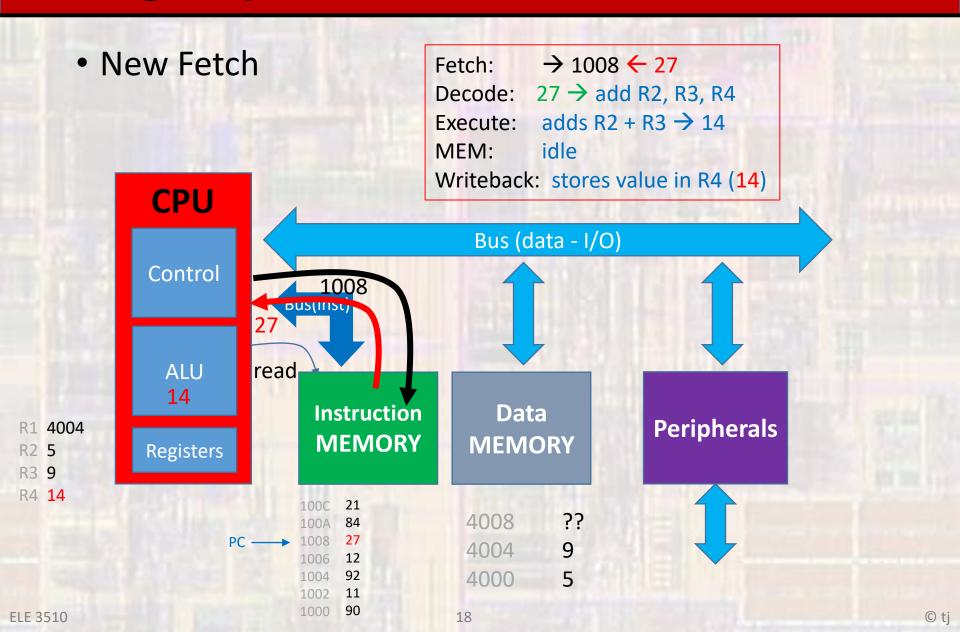

| 1008    | add R2, R3, R4 | 27       | R4 <- R2 + R3                  |

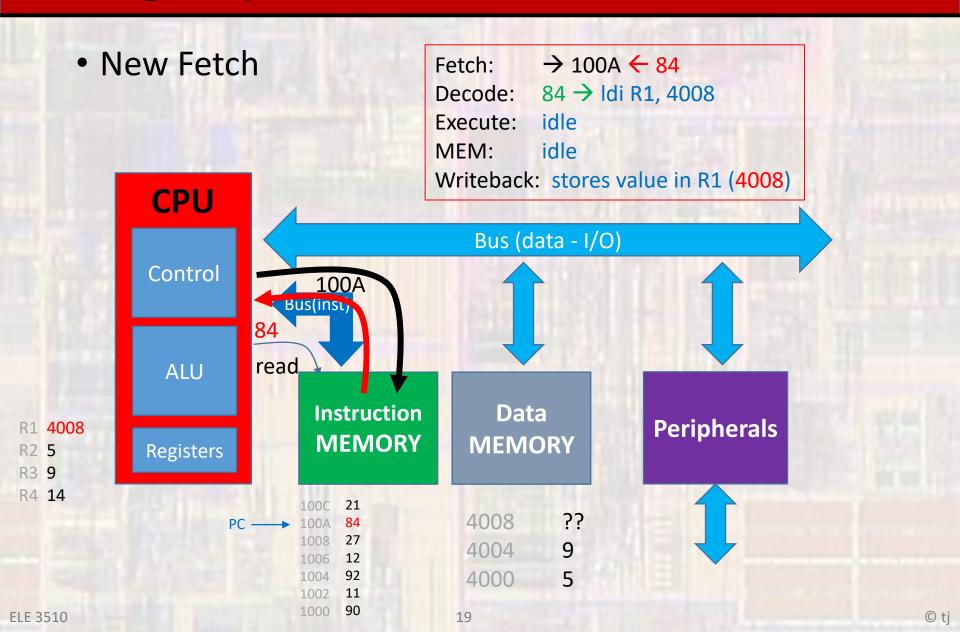

| 100A    | ldi R1, 4008   | 84       | Load loc for A into R1         |

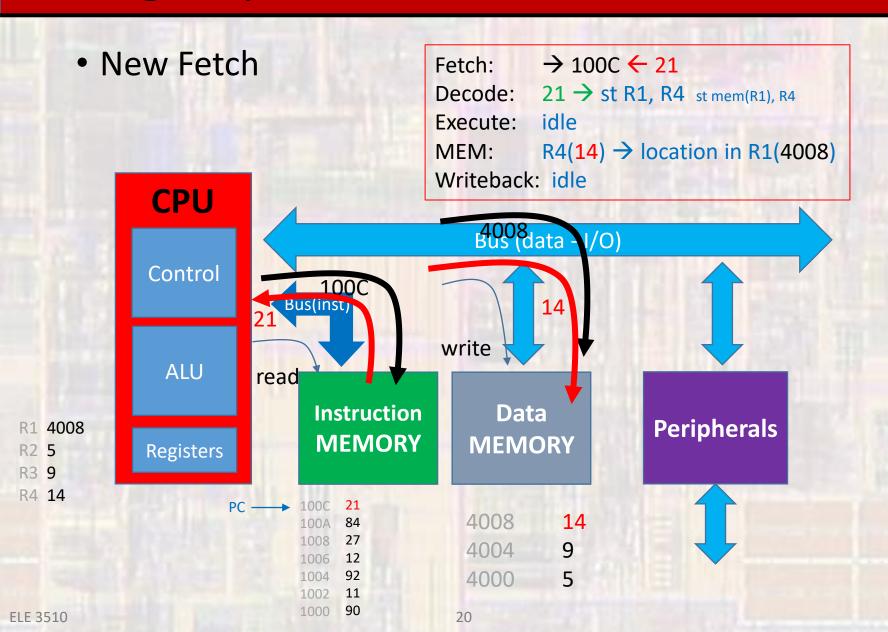

| 100C    | st mem(R1), R4 | 21       | Put value of R4 into loc for A |

Simplified Block Diagram

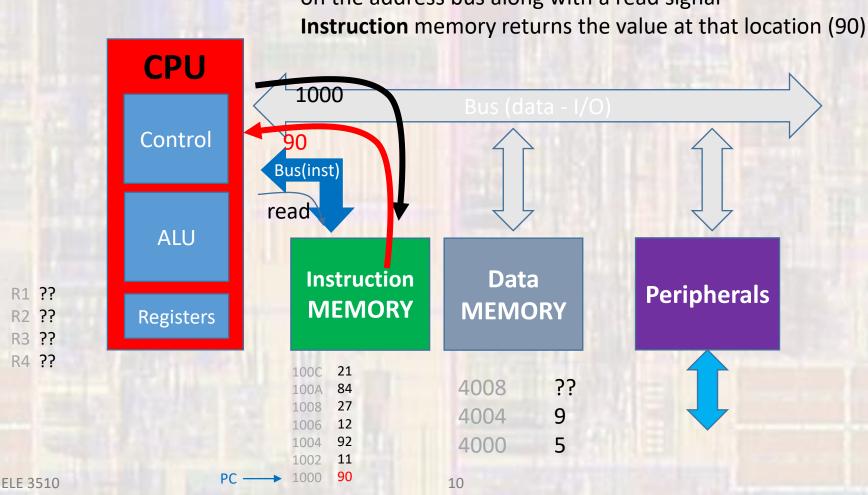

• First Instruction (fetch)

Control puts a memory location (1000) on the address bus along with a read signal Instruction memory returns the value at that location (90)

© ti

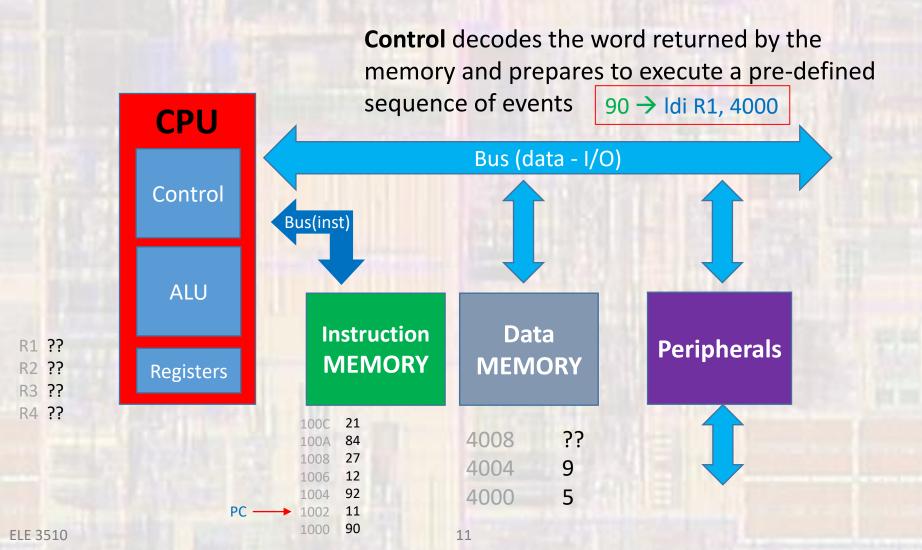

First Instruction (decode)

© ti

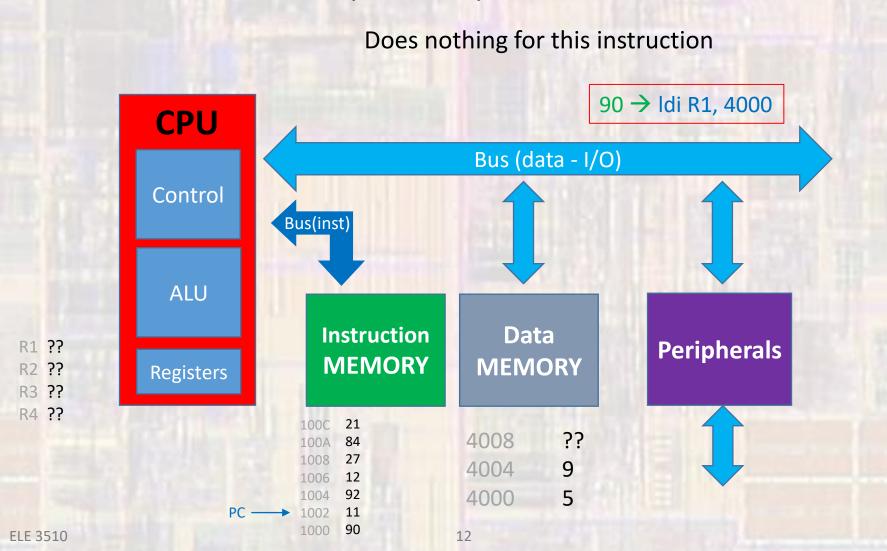

First Instruction (execute)

© tj

First Instruction (mem)

© ti

First Instruction (write back)

© ti

© tj

- Our Processor: Functionality

- Harvard Architecture

- RISC Load/Store Instruction Set

- 16 bit instruction words

- 4 8 bit data registers available for executing instructions (A-B-C-D)

- Support for 16 instructions (11 used)

- 3 memory based instructions

Our Processor