## Last updated 7/14/23

- Testbenches are used to simulate designs

- RTL level

- Gate level

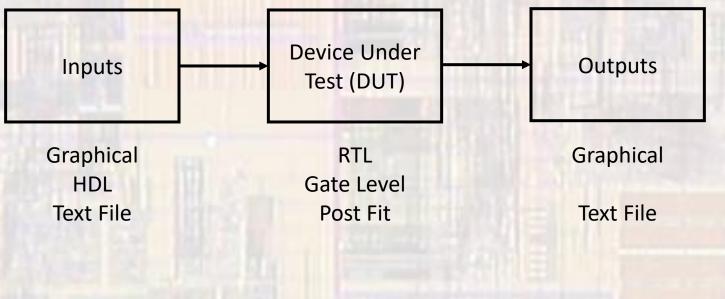

- General Testbench Structure

- Manual Testbench

- Inputs

- Hand coded

- HDL generated

- Expected Outputs

- User generated

- Results

- Compare waveforms to expectations

- Limited to

- Very small systems

- Systems with very few inputs and outputs

- Automated Testbench

- Inputs

- HDL generated

- Read from a file

- Expected Outputs

- HDL generated

- Be careful not to use the same code

- Read from a file

- Be careful not to use the same code

- Results

- Identify errors and document

- Test #, Time, Expected Value, Actual Value, ...

© tj

- VHDL Testbench Code

- General structure

- Define input and output signals

- Connect inputs and outputs to the DUT (device under test)

- Generate input waveforms

- Simulate and verify outputs

- Test benches can contain un-synthesizable code

- Variables

- Time

- After

- Wait for

- Loops

- For

- While-loop

- Quartus Interaction and ModelSim

- To use Quartus to start/run your ModelSim simulation you must setup the simulation in Quartus

- Assignments → Settings → EDA Tool Settings → Simulation → Test Benches :

- Quartus will generate errors on compilation if you set the testbench to the top-level entity

- Use the device under test as the top-level entity

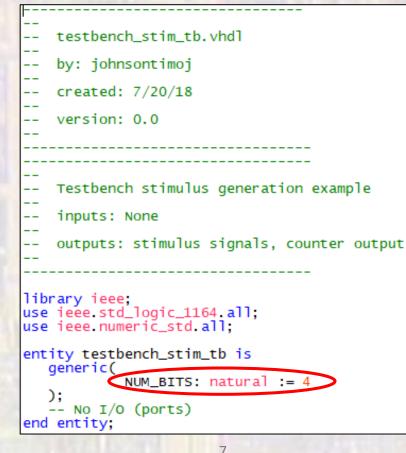

- Documentation, includes and entity

- No ports testbench is self-contained

- Generics are allowed

- Signal Definitions

- Use all caps

- Setup a constant for the clk (PER)

- Only need to change this 1 place when changing the clk frequency

```

architecture testbench of testbench_stim_tb is

-- Input signals

signal

CLK:

std_logic;

std_logic;

signal

RSTB:

std_logic;

signal X_IN:

signal Y_IN:

std_logic_vector(7 downto 0);

signal Z_IN:

std_logic;

std_logic_vector(6 downto 0);

CNT_IN:

signal

-- Output signals

signal CNT_OUT:

std_logic_vector((NUM_BITS - 1) downto 0);

-- clock constant - 50MHz

constant PER: time := 20 ns:

```

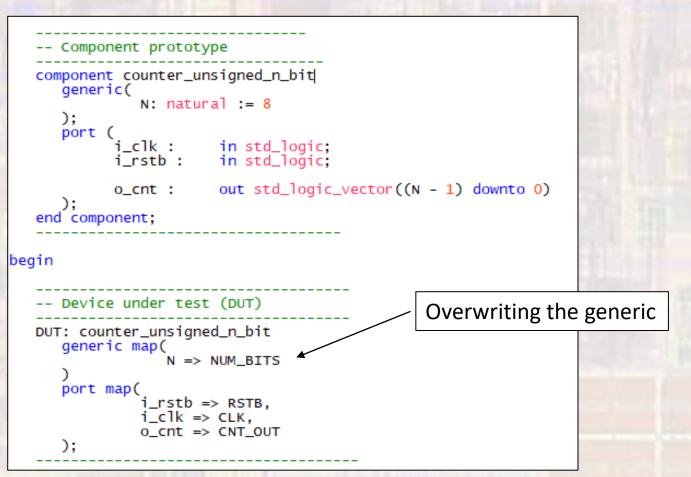

- Device under test

- Component + instantiation

- Signal generation

- Clk and ResetB

```

-- clock process

clock: process -- no sensitivity list allowed

begin

CLK <= '0';

wait for PER/2;

infinite: loop

CLK <= not CLK;

wait for PER/2;

end loop;

end process;

-- Reset process

-- active low, changes on falling edge

resetB: process -- no sensitivity list allowed

begin

RSTB <= '0';

wait for 2*PER;

RSTB <= '1';

-- waits forever

wait:

end process;

```

/testbench\_stim\_tb/CLK

/testbench\_stim\_tb/RSTB

0

- Signal generation

- std\_logic

```

-- Concurrent signal assignment

-- note "after" uses absolute timing within a single statement

'1',

'0' after 20 ns,

Z_IN \leq =

'1' after 25 ns,

'0' after 35 ns;

-- fixed pattern process

fixed: process -- no sensitivity list allowed

constant x_values: std_logic_vector(11 downto 0) := "110101100101";

begin

for i in x_values'range loop

X_IN <= x_values(i);

wait for 10 ns;

end loop;

wait for 20 ns: -- executes repeatedly

end process;

/testbench stim tb/Z IN

0

/testbench stim tb/X IN

0

1

```

- Signal generation

- std\_logic\_vector

```

-- vector non-periodic process

vnp: process -- no sensitivity list allowed

begin

wait for 30 ns;

Y_IN <= std_logic_vector(to_unsigned(22, Y_IN'length));</pre>

wait for 20 ns;

Y_IN <= std_logic_vector(to_unsigned(15, Y_IN'length));</pre>

wait for 10 ns;

Y_IN <= "10100101";

-- executes only once

wait:

end process:

-- counting process

count: process -- no sensitivity list allowed

begin

for i in 0 to 9 loop

wait for 2*PER:

CNT_IN <= std_logic_vector(to_unsigned((i * 10), 7));</pre>

end loop;

end process;

```

| /testbench_stim_tb/Y_IN   | 10100101 | UUUUUUUU |         |                 | 000      | 010110 | 10 | 00001111 | 10100101 |    |

|---------------------------|----------|----------|---------|-----------------|----------|--------|----|----------|----------|----|

| /coucher_oun_u/r_rr       |          |          | 1000101 | <u>10 ,00</u> , | 10100101 |        |    |          |          |    |

| /testbench_stim_tb/CNT_IN | 10 X     |          |         | 0               |          | 10     |    | 20       |          | 30 |

- Additional Information

- Simulation Setup

- Class Website/Labs : Modelsim Testbench Setup

- Simulation Tips

- Restart, Add signals, ...

- Class Website/Labs : Modelsim Simulation Tips