# VHDL Best Practices

## Last updated 2/2/24

#### **VHDL Best Practices**

- Best Practices ???

- Best practices are often defined by company, toolset or device

- In our case Dr. Johnson is setting the "best practices"

- These rules are for Class/Lab purposes. Industry best practices would include a much more extensive list

- I/O synchronization

- Clock domains

- Revision control

- Test coverage

© ti

## VHDL Best Practices – page 1/2

- Use meaningful names for blocks, signals and programs

- Use i xyz for block input signal names and o xyz for block output signal names

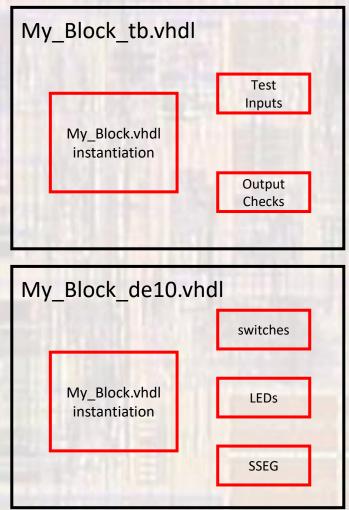

- Use tb and \_de10 name extensions for testbenches and hardware implementations

- <u>1 design file, instantiate it in the testbench and hardware implementation files</u>

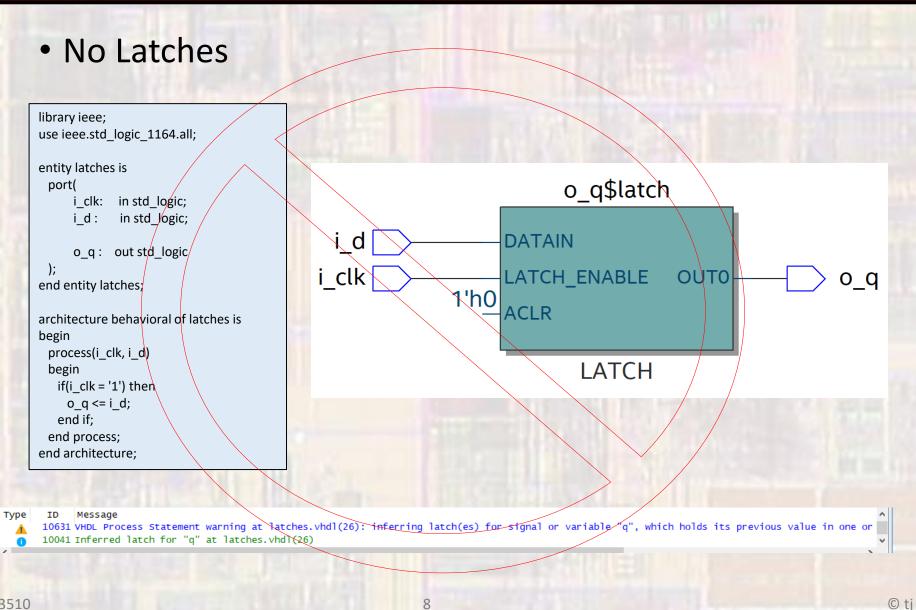

- <u>No latches</u>

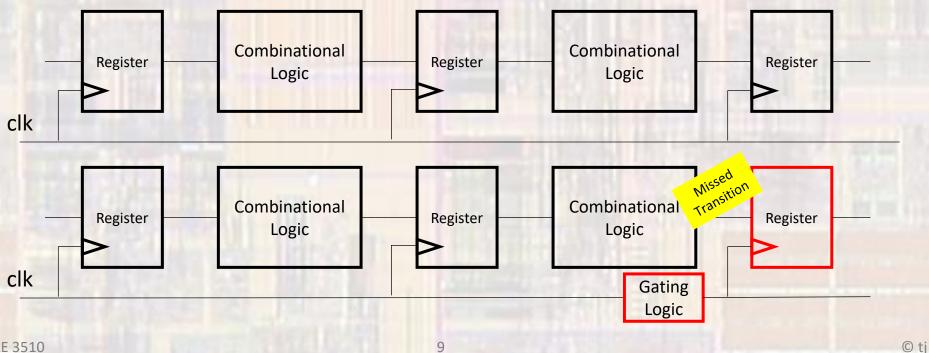

- <u>No Clock Gating</u> <u>Use Enable if Necessary</u>

- Make blocks generic where appropriate

- Use instantiation instead of schematics for hierarchy

- Use explicit port mapping when instantiating components

- No signal initialization in declarations

## VHDL Best Practices – page 2/2

- No variables as signals

- <u>I/O signals are SLV, internal signals are signed/unsigned</u> <u>as appropriate</u>

- Embed conditional signal assignments in processes

- Use rising edge()

- <u>Reset bar for general (control) synchronous logic</u>

- No reset for Data Path FFs and Registers

- <u>Compare to ( < 0) or ( >= 0)</u>

- Clock divider OK for slowing to human speeds

- If your FSM has more than 10 states rethink the problem/solution

- Break FSM designs into separate Next State, Register, and Output Logic(Mealy) sections

- Create a "heartbeat" on your DE10 implementations

### Use meaningful names ...

- Use meaningful names for blocks, signals and programs

- Stoplight with emergency detection for lab 22

lab22.vhdl testbench.vhdl board.vhdl

stoplight\_w\_emergency.vhdl

stoplight\_w\_emergency\_tb.vhdl

stoplight\_w\_emergency\_de10.vhdl

Note: primary function followed by secondary functions

© tj

### Use i\_xyz ...

Use i\_xyz for block input names and o\_xyz for block output names

| port(i_A: | in  | <pre>std_logic_vector(3 downto 0);</pre> |

|-----------|-----|------------------------------------------|

| i_B:      | in  | <pre>std_logic_vector(3 downto 0);</pre> |

| i_CIN:    | in  | std_logic;                               |

| o_SUM:    | out | <pre>std_logic_vector(3 downto 0);</pre> |

| o_COUT:   | out | std_logic                                |

| );        |     |                                          |

**Exception:** When using the pin-names from the QSF file for DE10 implementations, the names must

match exactly

| entity lab_4_de10 is |     |                                          |  |

|----------------------|-----|------------------------------------------|--|

| port(                |     |                                          |  |

| CLOCK_50 :           | in  | std_logic;                               |  |

| SW:                  | in  | <pre>std_logic_vector(9 downto 0);</pre> |  |

| HEX0:                | out | <pre>std_logic_vector(7 downto 0);</pre> |  |

| HEX1:                | out | <pre>std_logic_vector(7 downto 0);</pre> |  |

| HEX2:                | out | <pre>std_logic_vector(7 downto 0);</pre> |  |

| HEX3:                | out | <pre>std_logic_vector(7 downto 0)</pre>  |  |

| );                   |     |                                          |  |

| end entity;          |     |                                          |  |

## 1 design file, instantiate ...

• 1 design file, instantiate it in the testbench and HW implementation files

#### No Changes to the design

### **No Latches**

=

S

## **No Clock Gating**

- Our concept of sequential logic requires that all registers are updated at the same time

- Clock gating introduces delays in some paths and not in others  $\rightarrow$  possibility of clocks not occurring at the same time

9

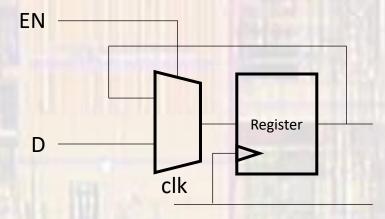

## No Clock Gating – Use Enable

- No Clock Gating Use Enable if Necessary

- We can "stop" the clock to some registers by using an enable signal

- Does not provide full power savings

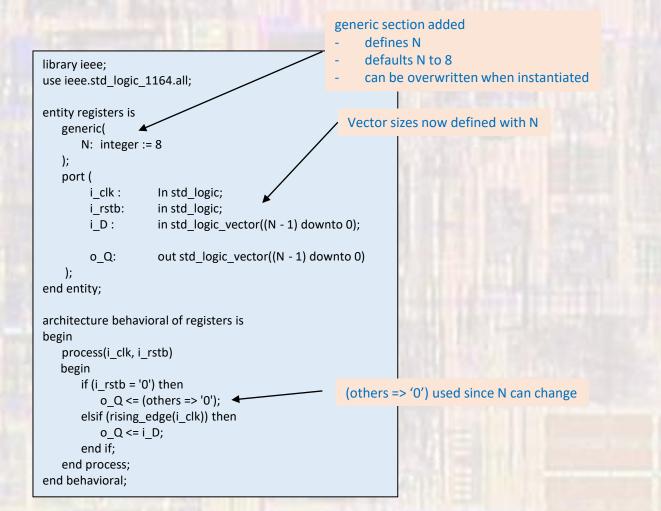

#### **Make Blocks Generic**

Make blocks generic whenever possible

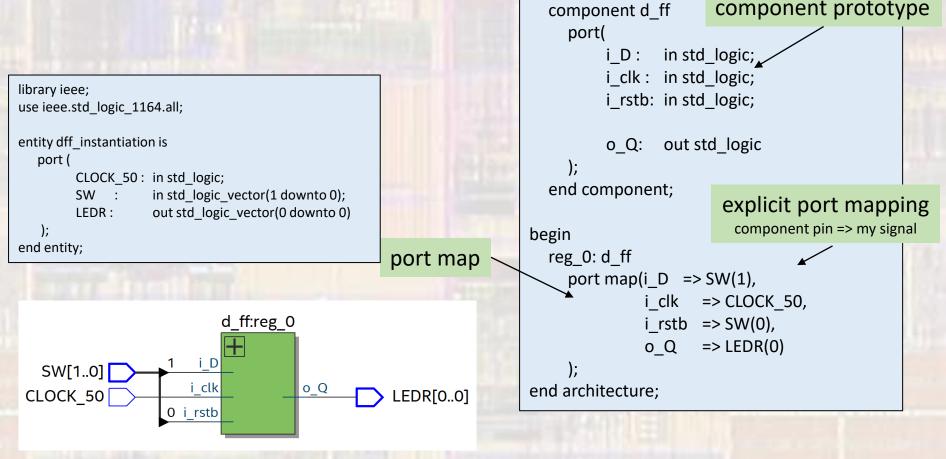

## **Use Explicit Port Mapping**

• Always use explicit port mapping on component instantiation architecture structural of dff\_instantiation is

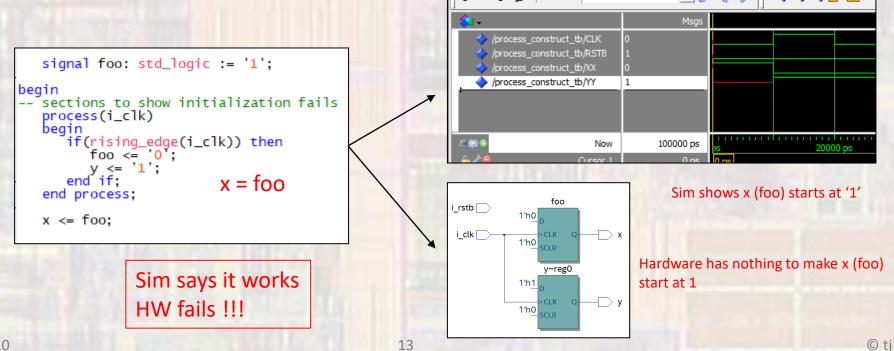

## **No Signal Initialization**

- No signal initialization in declarations

- It is not possible to implement signal initialization in hardware

- Rely on reset for any required initialization in hardware

signal foo: std\_logic : ??';

### No Variables as Signals

- No variables as signals

- We are using HDL code to represent HARDWARE

- Variables do not have a HARDWARE analog

- Variables are treated differently than signals

- Variables are updated immediately in a process

- Signals are only updated at the end of a process

- Variable are appropriate for compile time calculations

- Generate

- Test Benches

## I/O signals are ...

- I/O signals are SLV, internal signals are signed/unsigned as appropriate

- We are using HDL code to represent HARDWARE

- I/O ports are represented by std\_logic or std\_logic\_vectors

- They are interpreted as connections

- Internal signals

- Use std\_logic to represent single wires

- Use unsigned to represent unsigned bus signals and structural buses (memory addresses, ...)

- Use signed to represent signed bus signals

## Embed conditional signal ...

- Embed conditional signal assignments in processes

- Processes allow for a more structured design

- Processes allow the use of more flexible constructs

- if-else

- case

- Basic forms of If-else and Case statements create the same RTL as When-else and With-select

- Simple signal assignments do not need to be placed in a process

- A <= (B or C);

© ti

## Use Rising\_Edge()

- Use Rising\_Edge()

- (rising\_edge(clk)) instead of (clk'event and clk = '1') in register (FF designs)

- Also use (falling\_edge(clk))

- These do better multi-state checking in simulation

clk'event includes things like  $Z \rightarrow 1$  $U \rightarrow 1$

rising\_edge only includes  $0 \rightarrow 1$

```

process(i_clk, i_rstb)

begin

if (i_rstb = '0') then

o_Q <= '0';

elsif (rising_edge(i_clk)) then

o_Q <= i_D;

end if;

end process;</pre>

```

### Reset\_bar for general ...

- Reset\_bar for general (control) synchronous logic

- All non-data path registers will have a rstb signal

```

library ieee;

use ieee.std logic 1164.all;

entity d ff is

port (

i clk: in std logic;

i rstb:in std logic;

in std_logic;

iD:

out std logic

o Q:

);

end entity;

architecture behavioral of d ff is

begin

process(i_clk, i_rstb)

begin

if (i rstb = '0') then

o Q <= '0';

elsif (rising edge(i clk)) then

o Q <= i D;

end if;

end process;

end behavioral:

```

```

library ieee;

use ieee.std logic 1164.all;

entity registers is

generic(

N: integer := 8

);

port (

i clk: in std logic;

i rstb: in std logic;

iD:

in std logic vector((N - 1) downto 0);

out std logic vector((N - 1) downto 0)

o Q:

);

end entity;

architecture behavioral of registers is

begin

process(i clk, i rstb)

begin

if (i rstb = '0') then

o Q <= (others => '0');

elsif (rising_edge(i_clk)) then

o Q <= i D;

end if:

end process;

end behavioral;

```

## Compare to ( < 0) or ( >= 0)

- Compare to ( < 0) or ( >= 0)

- These comparisons only require checking the MSB

### Create a DE10 heartbeat output

- Lots of things can go wrong on the way to getting to a DE10 implementation

- An easy check that you have programmed the DE10 implementation properly is to bring out your DE10 clock signal to an LED

- Assuming you have created a clock divider and the divided signal is called something like clk\_sig

- Add something like

LEDR(9) <= clk\_sig;</pre>

in the output section of your DE10 implementation

Then you can be sure your programming succeeded based on the "heartbeat"