# Last updated 2/19/25

- Four major VHDL memory solutions

- Mux based

- Only applicable for ROMs

- FlipFlop based

- Very large only acceptable for very small memories

- Inferred

- Memory is implemented in a pre-built memory block

- Memory block must exist in the platform

- Tightly coupled memory small but very fast

- General memory large and not as fast

- External

- The memory interface is implemented

- The memory itself is a separate chip

© ti

- VHDL solution for memories

- An array of std\_logic\_vectors

N words x M bits/word N array elements x SLV

- Coded just like the non-optimized long array of data words

- Array construct

- New type, that has array type as its basis type my\_new\_type is array (0 to depth) of some\_vhdl\_type

- Memory construct

- Uses std\_logic\_vector

- No understanding of the values (signed/unsigned) is assumed, just bits

type my\_memory is array (0 to depth) of std\_logic\_vector((wordwidth - 1) downto 0);

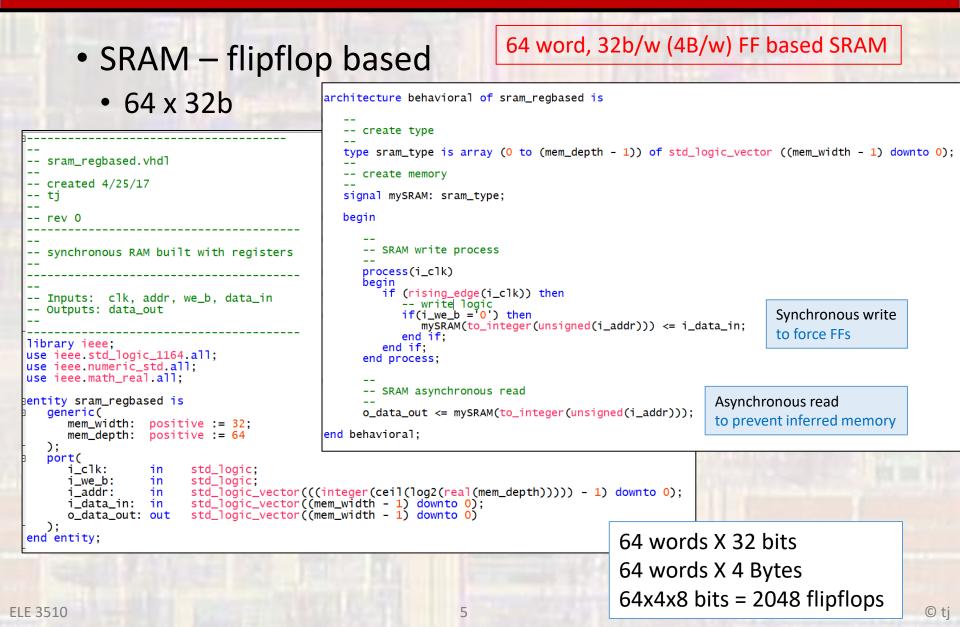

- SRAM flipflop based

- Using flipflops as our memory storage element

- The inferred memories on our FPGA all require synchronous read paths

- To force a flipflop based memory the read path must be asynchronous

- Since we want flipflops, we must have some clock controlling the memory

- Make the write path synchronous

- Outputs of the flipflops are always available

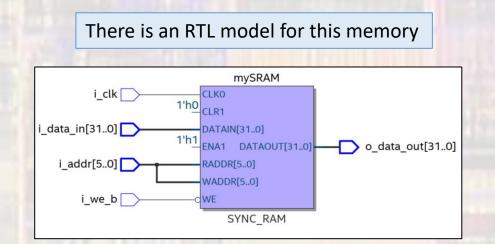

- SRAM register based

- 64x32b

#### The implementation is in flipflops

| Flow Summary                       |                              |

|------------------------------------|------------------------------|

| < <filter>&gt;</filter>            |                              |

| Flow Status                        | Successful - Fri May 15 11:1 |

| Quartus Prime Version              | 19.1.0 Build 670 09/22/20    |

| Revision Name                      | Class_Examples               |

| Top-level Entity Name              | sram_regbased                |

| Family                             | MAX 10                       |

| Device                             | 10M50DAF484C7G               |

| Timing Models                      | Final                        |

| Total logic elements               | 3,472                        |

| Total registers                    | 2048                         |

| Total pins                         | 2                            |

| Total virtual pins                 | 0                            |

| Total memory bits                  | 0                            |

| Embedded Multiplier 9-bit elements | 0                            |

| Total PLLs                         | 0                            |

| UFM blocks                         | 0                            |

| ADC blocks                         | 0                            |

(0)

ELE 3510

+ - 1

/sram\_128b\_tb/DATA\_IN

💶 🌙 /sram\_128b\_tb/DATA\_OUT

45

( 30

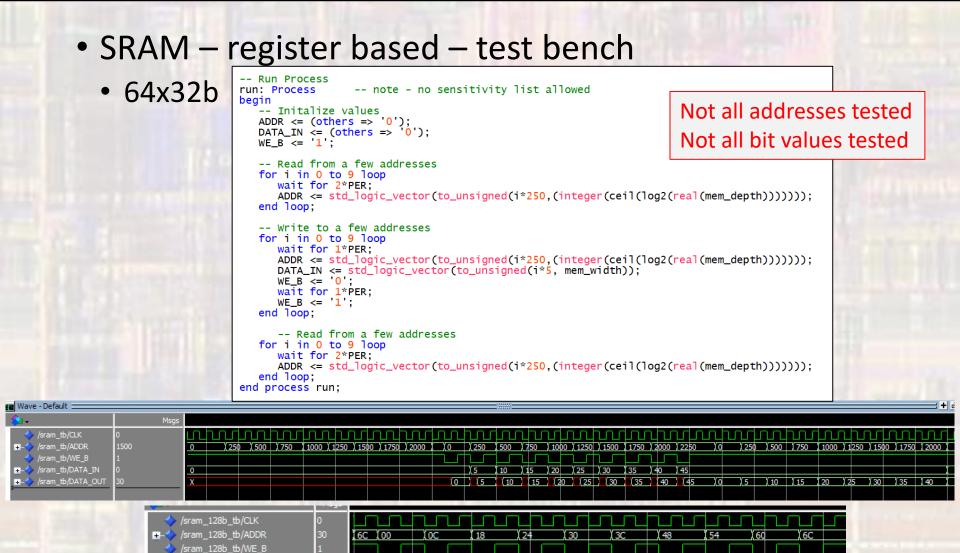

- Memory Test Benches

- A proper memory testbench would test:

- All addresses

- All bits 0 and 1

- Read ROMs, R/W for RAMs

- Write\_enable\_bar functionality