Last updated 8/20/24

This is not a programming language It is a hardware description language

- A VHDL signal represents a wire

- A single wire is identified as a std\_logic signal

#### Declaration

```

signal in1: std_logic;

signal in2: std_logic;

signal out1: std_logic;

```

in1 ——

in2 ——

out1 ——

#### **Behavior**

out1 <= in1 AND in2;

- A VHDL signal represents a wire

- A bus (collection of wires) is identified as a std\_logic\_vector signal

- Includes the dimension of the bus in wire order 7 6 5 4 3 2 1 0

- Format: std logic vector((n-1) downto 0)

#### Declaration

inA 8/

inB 8/

out\_AB 8/

#### Behavior

out\_AB <= inA OR inB;

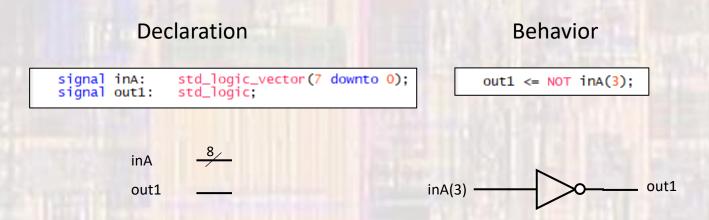

- Individual wires in a bus can be identified

- signal\_name(wire number)

- Contiguous wires in a bus can be identified

- signal\_name(wire range)

- Format: signal\_name(n downto m)

### Declaration

### Behavior

```

signal inA: std_logic_vector(7 downto 0);

signal out1: std_logic_vector(3 downto 0);

```

```

out1 <= NOT inA(6 downto 3);

```

© ti

```

inA \frac{8}{} out1 \frac{4}{}

```

- Wires and buses can be combined to create a new signal (bus) <u>name</u>

- No new wires are created just connected to an additional name

- Concatenation operator &

### Declaration

#### Behavior

new\_bus <= inA & in1 & inB;

new\_bus: inA(7), inA(6), ... inA(0), in1, inB(3), ...inB(0)