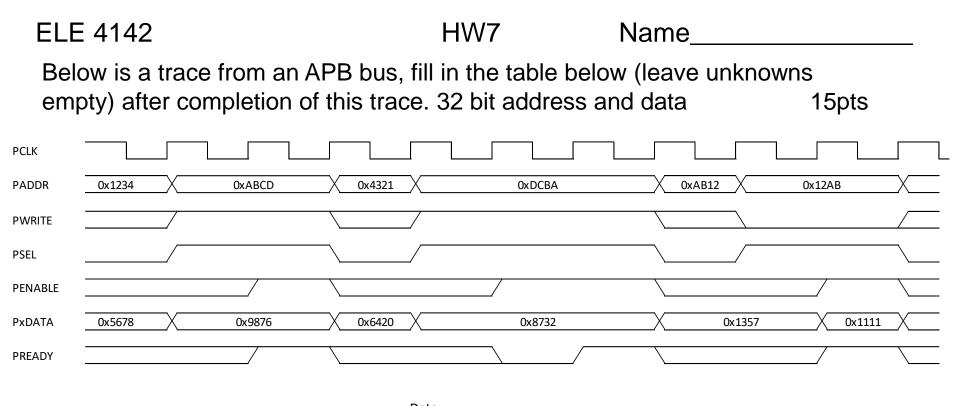

DataAddressMaster (via the bridge)Slave (peripheral)0x12340x12340x11110x12AB0x11110x11110x43210x11110x11110xAB120x98760xABCD0x8732

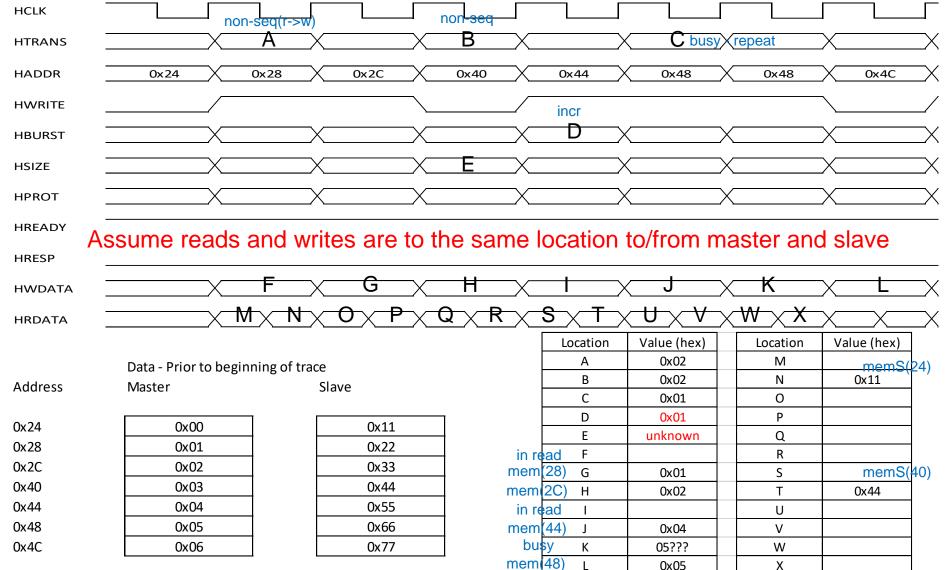

## ELE 4142HW7Name\_\_\_\_\_Below is a trace from an AHB-Lite bus, fill in the values below (leave unknowns<br/>empty)35 pts

ELE 4142

Assume a PCIe Link operating a 8GT/s

## HW7

Name\_

30pts

a) In a 1x configuration what is the Link bandwidth using 8b/10b encoding (don't use the table from the notes – it will not be right)

8GT/s \* (8b/10T) = 6.4Gb/s → 800MB/s

b) In a 4x configuration what is the Link BW using 128b/130b encoding

$(8GT/s * 4) * (128b/130T) = 31,507,692b/s \rightarrow 3,938,462B/s$

c) Assuming a 1x configuration, 8b/10b encoding, a 4DW header, 32 Bytes of data and no ECRC or End, how many bits would transfer in a single read request?

32 Bytes of data + 16 bytes of header + 2 bytes of sequence + 4 bytes of LCRC + 2 bytes of STP = 56 bytes = 448 bits 448 bits \*10T/8b = 560 bits

d) Assuming a 4x configuration, 8b/10b encoding, a 4DW header, 32 Bytes of data and no ECRC or End, how long would a single read request take?

560 bits from part C split across 4 lanes = 140 bits / lane (simultaneous) 140bits / (8GT/s / 2) = 35ns

## ELE 4142 Search and Think

20 pts

Name

Identify and <u>explain</u> 3 advantages of using differential signaling

- 2x signal swing at the same supply voltage

- $\rightarrow$  better noise immunity

- $\rightarrow$  opportunity to operate at lower voltages

Matched signals create less electromagnetic interference EMI

Matched signals are less susceptible to electromagnetic interference EMI

HW7

No required common mode voltage

Identify at least 1 disadvantage of differential signaling

Requires 2 wires or twice the board space + any addition spacing to protect 2 wires