Last updated 1/18/24

- Processor Cost Overview

- Key Components building to part cost

- Wafer Cost

- 300mm wafers range from \$5000/wafer (early) down to \$1200/wafer (mature)

- Cost reductions associated with process maturity

- Wafer Yield = number of wafers that make it through the process with working transistors

- Die Cost

- Based on the number of full die that can fit on a wafer

- Good Die Cost

- Based on the number of die that are fully functional (may include redundancy)

- Packaged Part Cost

- Add the cost of package and packaging process

- Good Packaged Part Cost

- Based on the number of fully functional packaged parts (may include redundancy)

- Margin

- Additional \$ to cover R&D, facilities, ... AND profit

#### Processor Cost Overview

- Wafer Cost

- 45nm, 300mm wafers ~ \$2000/wafer

- Typical "lot" of 25 wafers

- Typical wafer yield of 95%

- Losses are a combination of single wafers and whole lots

- Die Cost

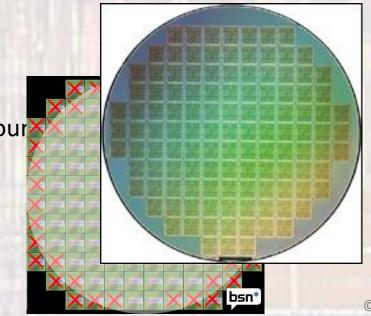

- # of full die that will fit on a wafer

- Various approaches to maximize die cour

- Die Cost = Wafer Cost / # of Die

ELE 4142 3

Processor Cost Overview

- Processor Cost Overview

- Good Die Cost

- Based on the number of die that are fully functional

- 2 primary yield components

- Parametric Yield

- Process Yield

- Parametric Yield

- Parts that fail to meet a performance measure

- Typically max frequency or current drain

- Can be mitigated by binning (have a fast version of the part and a slow version)

- Typically 95% on digital parts

- Process Yield

- Dominated by defects in the manufacturing process

- $Y = Y_o(1 + \frac{D_0 A}{\alpha})^{-\alpha}$  NB negative binomial model

- Y<sub>0</sub> portion of area subject to defects (0.8-0.95)

- D<sub>0</sub> defect density (100defects/cm<sup>2</sup> (early) 0.15defects/cm<sup>2</sup> (mature))

- A die area (20mm² 400mm²)

- α cluster factor (10 20)

#### Processor Cost Overview

- Packaged Part Cost

- Add the cost of package and packaging process

- \$0.20 for small simple packages

- \$2 \$4 for complex BGAs

- \$1 for POP

- Good Packaged Part Cost

- Based on the number of fully functional packaged parts

- Package yield is typically 95% 99+%

- Margin

- Additional \$ to cover R&D, facilities, ... AND profit

- 20% for mature products

- 50% for new products

- Processor Cost Example

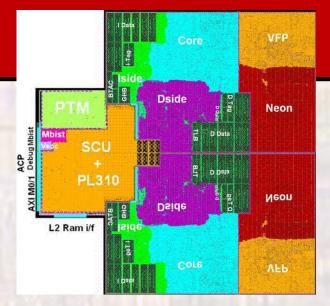

- Arm Cortex A9

- 32kB I/D Cache

- 26M transistors

- 500mW @ 2GHz

- 5mm<sup>2</sup> in 45nm process technology

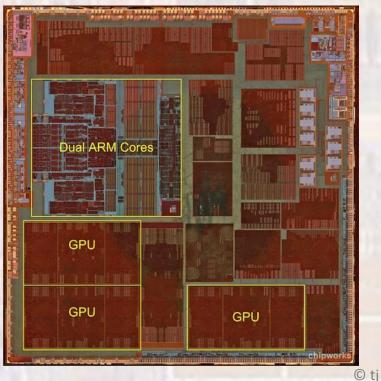

- Apple A5

- Dual Arm Cortex A9s

- 45nm Samsung Process

- Die size = 122mm<sup>2</sup>

- 1300 pin POP BGA

- Samsung 45nm process

- 300mm wafers

- $D_0 = 0.25 \text{ defects / cm}^2$

- $\alpha = 10$

- $Y_0A5 = 0.95$

- Processor Cost Example

- Wafer Cost

- 300mm, 45nm → \$2000 / wafer

- Wafer yield 95% → \$2105 / wafer

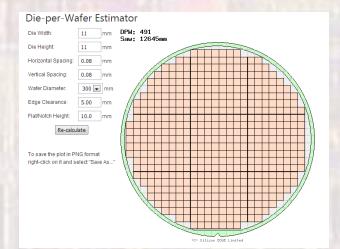

- Die Cost

- 122mm2 → 491 die/wafer → \$4.29 / die

- Good Die Cost

- $Y = Y_o (1 + \frac{D_0 A}{\alpha})^{-\alpha} = 0.95 (1 + \frac{(0.25 \text{ defects/cm}^2)(122 \text{mm2} \times (\frac{1 \text{cm}}{10 \text{mm}})^2)^{-10}}{10} = 0.703$

- Defect driven die cost = \$4.29/die / 0.703 = \$6.10 / die

- Parametric yield  $-0.98 \rightarrow $6.22$  / die

- Packaged Part Cost

- 1300 pin POP-BGA =  $\$3 \rightarrow 9.22$  / part

- Processor Cost Example

- Good Packaged Part Cost

- 98% yield → 9.41 / part

- Margin

- If this was not an Apple design

- Margin = 50% → Part cost = \$18.82

- Apple can cover the margin costs at the final product level

- → Part Cost = \$9.41

- Gut feel cost before margin = \$6.50