# Flash Operation

Last updated 2/8/24

#### NAND

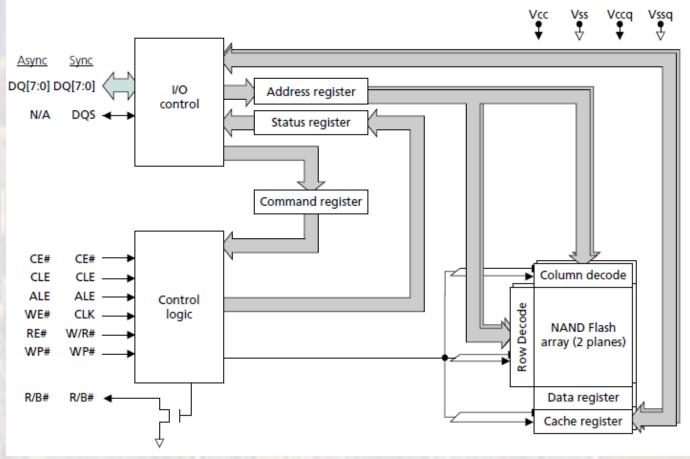

Configuration

© ti

NAND

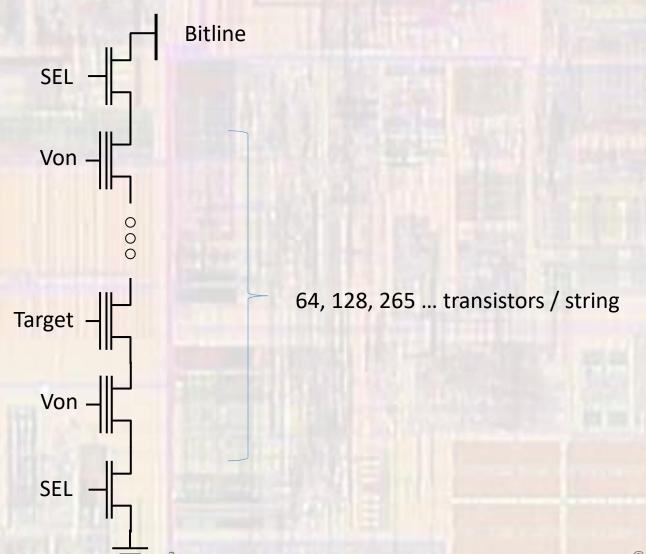

Nand String

**ELE 4142**

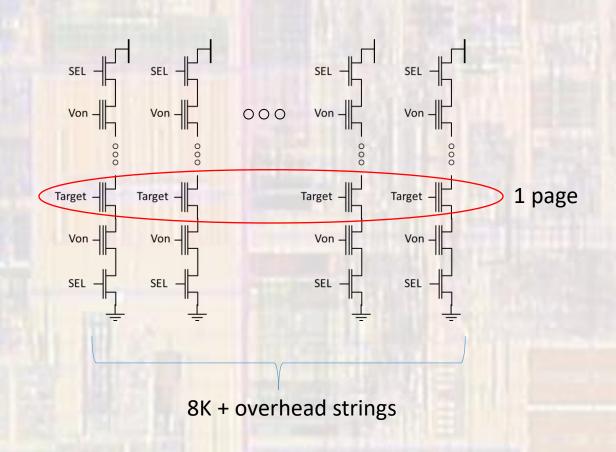

- NAND

- Page

- X 8 to give 8KB + OH / page

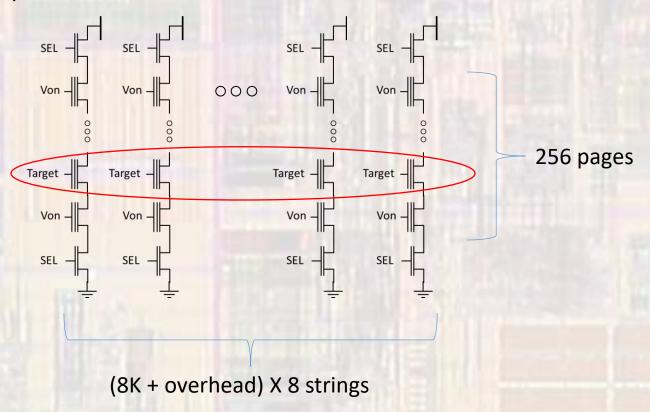

- NAND

- Block

- (8KB + OH)/page X 256 pages

- 2MB +OH / block

- NAND

- 64Gb

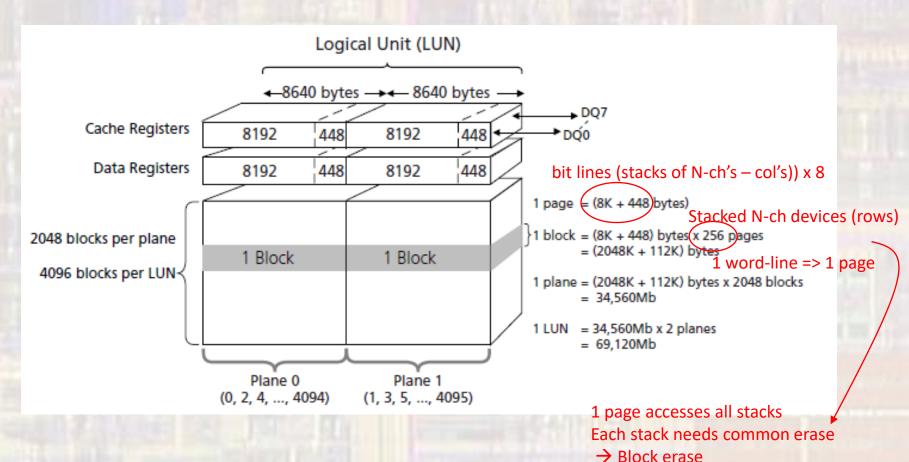

- Blocks, Planes, LUN

#### NAND

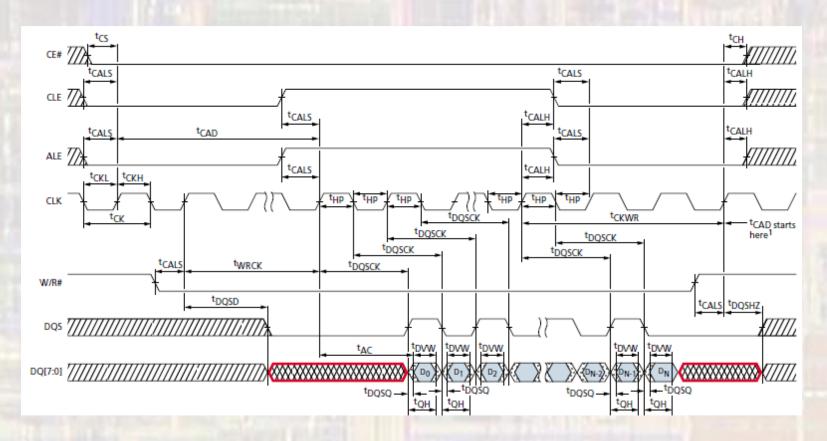

- Key Signals

- CE# Chip Enable bar

- CLE Command Latch Enable

- ALE Address Latch Enable

- WE# Write Enable bar

- RE# Read Enable bar

- RDY Ready

- DQx Output Data, Command Input, Address Input

- DQS Data Strobe

- CLK Clock only used in Synchronous mode

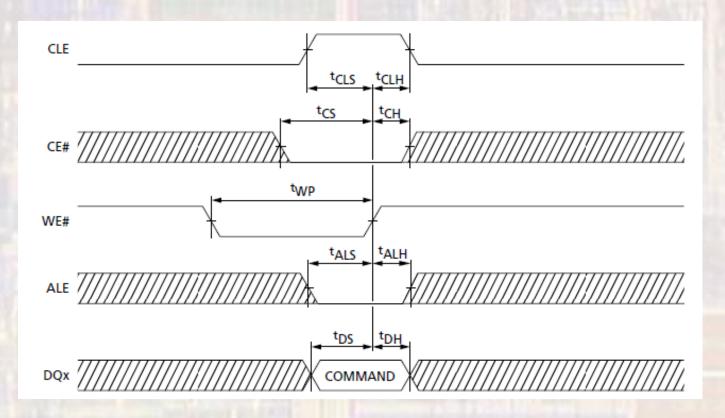

- NAND

- Asynchronous Command

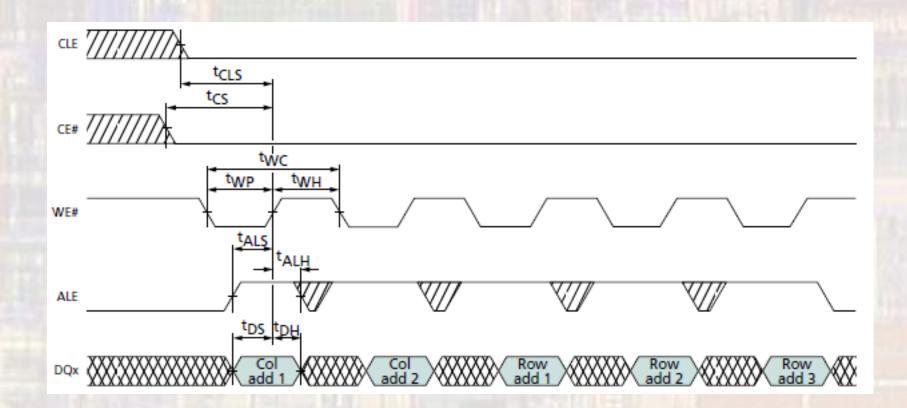

- NAND

- Asynchronous Address

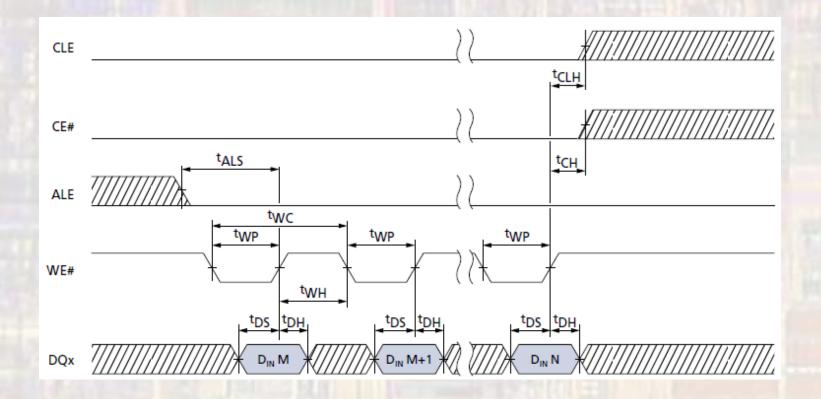

- NAND

- Asynchronous Data In to Cache

- NAND

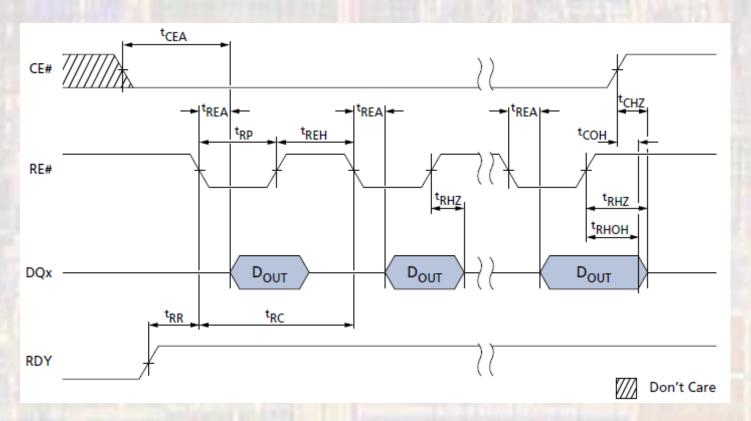

- Asynchronous Data Out from Cache

NAND

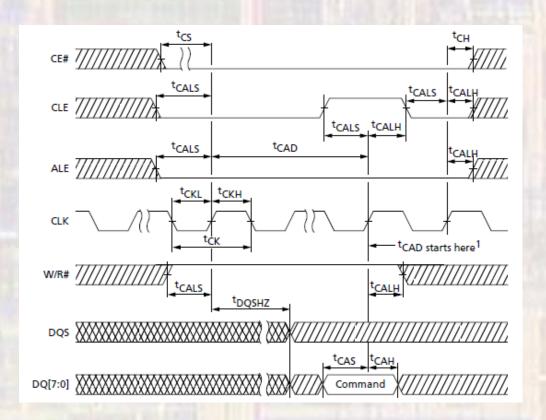

Synchronous Command

NAND

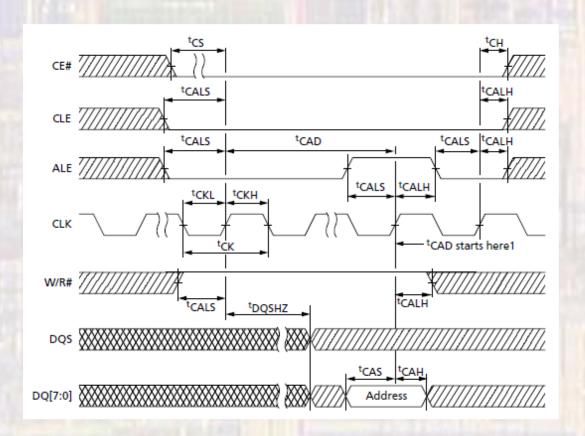

Synchronous Address

- NAND

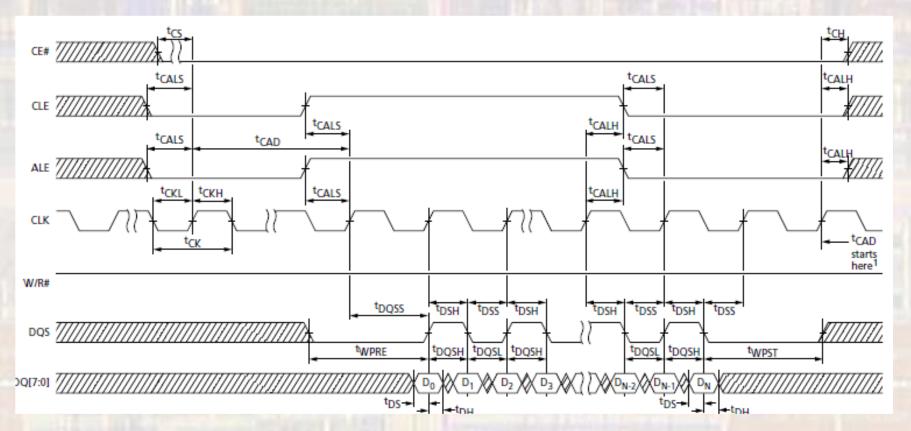

- Synchronous Data In DDR to cache

NAND

Synchronous Data Out – DDR - from cache

#### NAND

Command Based Interface

| Command                       | Command<br>Cycle #1 | Number of<br>Valid<br>Address<br>Cycles | Data<br>Input<br>Cycles | Command<br>Cycle #2 | Valid While<br>Selected LUN<br>is Busy <sup>1</sup> | Valid While<br>Other LUNs<br>are Busy <sup>2</sup> | Notes |

|-------------------------------|---------------------|-----------------------------------------|-------------------------|---------------------|-----------------------------------------------------|----------------------------------------------------|-------|

| Column Address Operations     |                     |                                         |                         |                     |                                                     |                                                    |       |

| CHANGE READ COLUMN            | 05h                 | 2                                       | _                       | E0h                 |                                                     | Yes                                                |       |

| CHANGE READ COLUMN ENHANCED   | 06h                 | 5                                       | _                       | E0h                 |                                                     | Yes                                                |       |

| CHANGE WRITE COL-<br>UMN      | 85h                 | 2                                       | Optional                | -                   |                                                     | Yes                                                |       |

| CHANGE ROW ADDRESS            | 85h                 | 5                                       | Optional                | _                   |                                                     | Yes                                                | 5     |

| Read Operations               |                     |                                         |                         |                     |                                                     |                                                    |       |

| READ MODE                     | 00h                 | 0                                       | _                       | _                   |                                                     | Yes                                                |       |

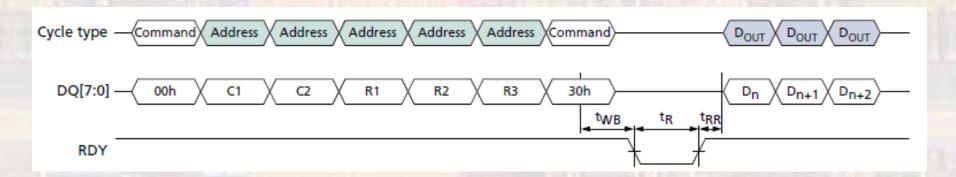

| READ PAGE                     | 00h                 | 5                                       | _                       | 30h                 |                                                     | Yes                                                | 6     |

| READ PAGE MULTI-<br>PLANE     | 00h                 | 5                                       | _                       | 32h                 |                                                     | Yes                                                |       |

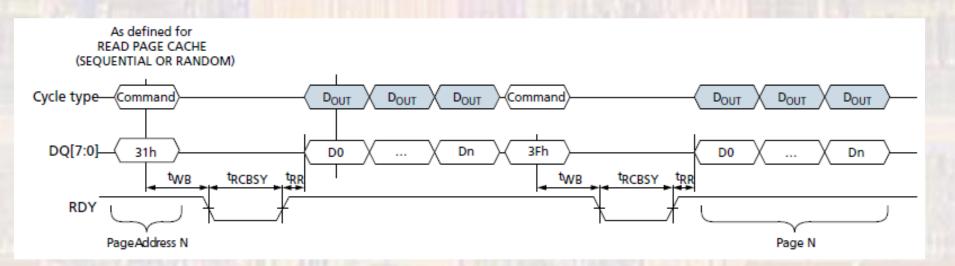

| READ PAGE CACHE<br>SEQUENTIAL | 31h                 | 0                                       | _                       | _                   |                                                     | Yes                                                | 7     |

| READ PAGE CACHE<br>RANDOM     | 00h                 | 5                                       | -                       | 31h                 |                                                     | Yes                                                | 6,7   |

| READ PAGE CACHE LAST          | 3Fh                 | 0                                       | _                       | _                   |                                                     | Yes                                                | 7     |

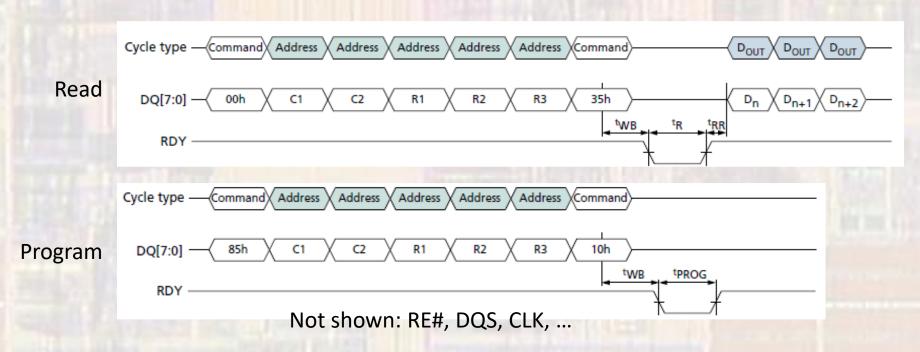

NAND

Read

Page Based – moves data for an entire page into the cache

- NAND

- Read Page

- NAND

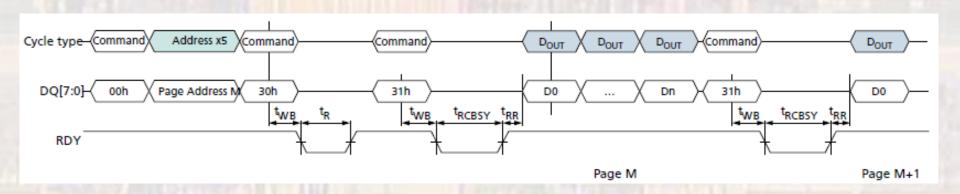

- Read Page Cache Sequential

- Increments the page address with each 31h command

- Can be executed during a page read out

- NAND

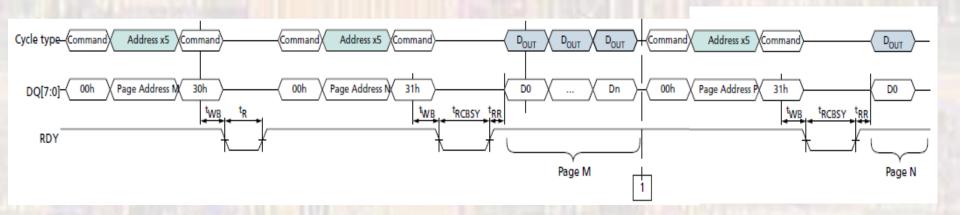

- Read Page Cache Random

- Provide a new page address during current data read out

- NAND

- Read Page Cache Last

- Indicates the last page to read

- NAND

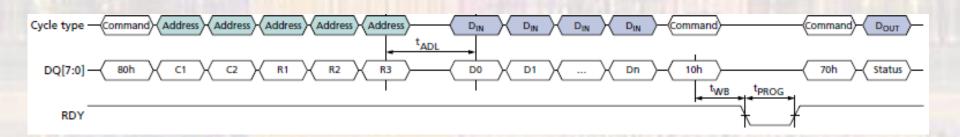

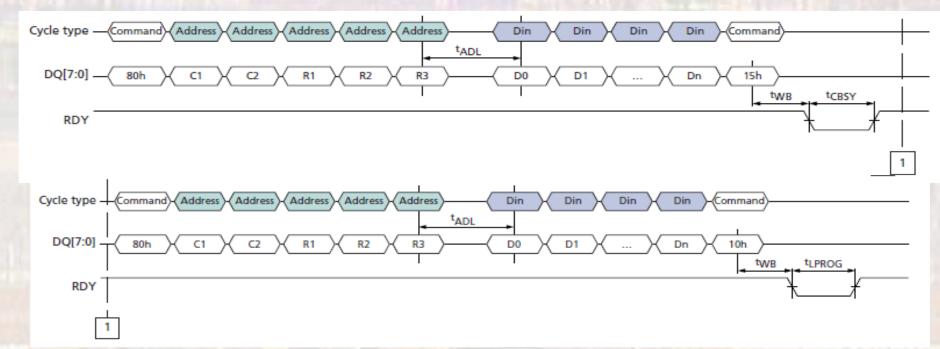

- Program

- Move data from Cache to the array

- All Programming is Page based

- Pages in a block must be programmed sequentially

- Program operations must be checked for error codes

- Failure

- Dis-allowed data values

- NAND

- Program Page

- No cache utilization

- NAND

- Program Page Cache

- Loads data into cache for later programming

- NAND

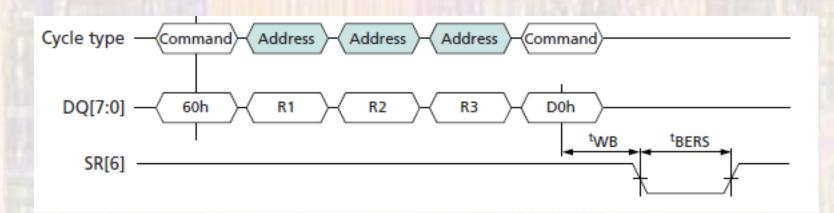

- Block Erase

#### NAND

- Copyback

- Copies a block to a new location

- Used for wear leveling

- NOR Parallel

- Similar to NAND

- Command based actions

- Synchronous and asynchronous versions

- Page based read/program supported

- Block Erase

- WORD based read/program possible

- NOR Serial

- Low pin count SPI interface

- Command based actions

- Serial Read/Program operations

- Page Program

### Memory - Flash

- Performance Issues

- Can 1 bad array element ruin an entire part?

- Use redundant rows and columns in the array

- Any bad cells are programmed out at final test

- Some Memory Management Units (MMUs) can detect poorly performing cells and modify the virtual to physical address translation to remove them from the memory map