# ELE 655 Microprocessor System Design

#### Class 3 – ISA

- 3 applications areas

- Desktop

- Performance is key

- Code size is no longer a concern

- → both integer and floating point instructions

- Servers

- Focus is on database, file server and WEB applications

- Integers and characters are primary data types

- → little emphasis on floating point

- Mobile / Embedded

- Power and code size are critical

- Floating point is optional

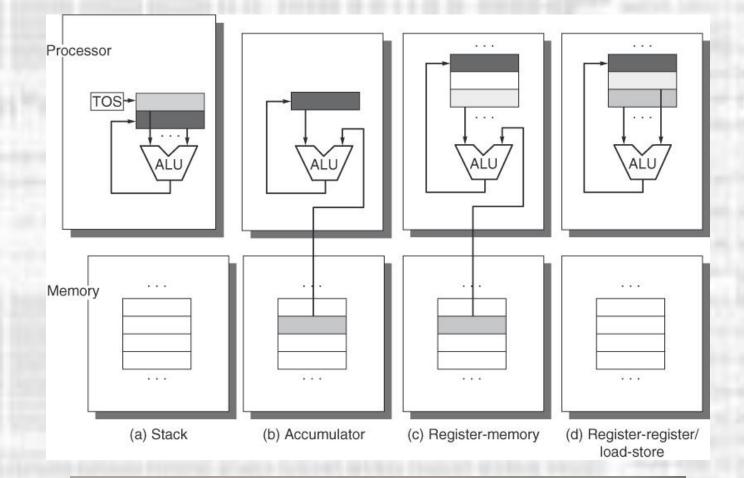

Figure A.1 Ope or the result of t shade indicates operand below. point to the resu operand is a re architecture, car

| Stack  | Accumulator      | Register<br>(register-memory) | Register (load-store) |

|--------|------------------|-------------------------------|-----------------------|

| Push A | Load A           | Load R1,A                     | Load R1,A             |

| Push B | Add B            | Add R3,R1,B                   | Load R2,B             |

| Add    | Store C          | Store R3,C                    | Add R3,R1,R2          |

| Рор С  | Indiana Makerine | " is somethinkes calified in  | Store R3,C            |

operand is an input inputs, and the dark combined with the d TOS is updated to alt. In (c), one input and, like the stack or (d).

© tj

#### GPR architectures dominate

- Registers are fast

- Local to processor

- Logic based instead of memory based

- Registers enhance compiler options

- Reorder calculations

- Not possible on a stack based machine

#### • Memory as an operand

| Number of<br>memory<br>addresses | Maximum number<br>of operands<br>allowed | Type of architecture | Examples                                                   |

|----------------------------------|------------------------------------------|----------------------|------------------------------------------------------------|

| 0                                | 3                                        | Load-store           | Alpha, ARM, MIPS, PowerPC, SPARC, SuperH, TM32             |

| 1                                | 2                                        | Register-memory      | IBM 360/370, Intel 80x86, Motorola 68000,<br>TI TMS320C54x |

| 2                                | 2                                        | Memory-memory        | VAX (also has three-operand formats)                       |

| 3                                | 3                                        | Memory-memory        | VAX (also has two-operand formats)                         |

| Туре                              | Advantages                                                                                                                                                 | Disadvantages                                                                                                                                                                                                                                                 |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register-register<br>(0, 3)       | Simple, fixed-length instruction encoding.<br>Simple code generation model. Instructions<br>take similar numbers of clocks to execute<br>(see Appendix C). | Higher instruction count than architectures with<br>memory references in instructions. More instructions<br>and lower instruction density lead to larger<br>programs.                                                                                         |

| Register-memory<br>(1, 2)         | Data can be accessed without a separate load<br>instruction first. Instruction format tends to<br>be easy to encode and yields good density.               | Operands are not equivalent since a source operand<br>in a binary operation is destroyed. Encoding a<br>register number and a memory address in each<br>instruction may restrict the number of registers.<br>Clocks per instruction vary by operand location. |

| Memory-memory<br>(2, 2) or (3, 3) | Most compact. Doesn't waste registers for temporaries.                                                                                                     | Large variation in instruction size, especially for<br>three-operand instructions. In addition, large<br>variation in work per instruction. Memory accesses<br>create memory bottleneck. (Not used today.)                                                    |

- Interpreting Memory Addresses

- Big vs Little Endian

- SDRAEKCAB

- Byte Addressed

- Byte / word aligned

| Property of         | Value of 3 low-order bits of byte address |                  |         |         |         |         |            |            |

|---------------------|-------------------------------------------|------------------|---------|---------|---------|---------|------------|------------|

| Width of object     | 0                                         | 1                | 2       | 3       | 4       | 5       | 6          | 7          |

| 1 byte (byte)       | Aligned                                   | Aligned          | Aligned | Aligned | Aligned | Aligned | Aligned    | Aligned    |

| 2 bytes (half word) | Alig                                      |                  | Alig    | ned     | Alig    | ned     | Alig       | ned        |

| 2 bytes (half word) |                                           | Misaligned Misal |         | igned   | Misali  | gned    | Misaligned |            |

| 4 bytes (word)      | 19 1118.00 10                             | Aligned          |         |         | Alig    | ned     |            |            |

| 4 bytes (word)      |                                           | Misaligned       |         |         |         |         | Misaligned |            |

| 4 bytes (word)      |                                           | Misaligned       |         |         |         | Misa    | ligned     |            |

| 4 bytes (word)      |                                           |                  |         |         | Misa    | ligned  |            | Misaligneo |

#### Addressing Modes

| Addressing mode       |                    | Meaning                                                                                                                                                                                                                                                                                       | When used                                                                                                                                              |

|-----------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register              | Add R4,R3          | Regs[R4] ← Regs[R4]<br>+ Regs[R3]                                                                                                                                                                                                                                                             | When a value is in a register.                                                                                                                         |

| Immediate             | Add R4,#3          | $Regs[R4] \leftarrow Regs[R4] + 3$                                                                                                                                                                                                                                                            | For constants.                                                                                                                                         |

| Displacement          | Add R4,100(R1)     | Regs[R4] ← Regs[R4]<br>+ Mem[100 + Regs[R1]]                                                                                                                                                                                                                                                  | Accessing local variables<br>(+ simulates register indirect,<br>direct addressing modes).                                                              |

| Register indirect     | Add R4,(R1)        | $\begin{array}{rcl} Regs[R4] & \leftarrow & Regs[R4] \\ & + & Mem[Regs[R1]] \end{array}$                                                                                                                                                                                                      | Accessing using a pointer or a computed address.                                                                                                       |

| Indexed               | Add R3,(R1 + R2)   | $\begin{array}{l} \operatorname{Regs}[R3] \leftarrow \operatorname{Regs}[R3] \\ + \operatorname{Mem}[\operatorname{Regs}[R1] + \operatorname{Regs}[R2]] \end{array}$                                                                                                                          | Sometimes useful in array<br>addressing: R1 = base of array;<br>R2 = index amount.                                                                     |

| Direct or<br>absolute | Add R1,(1001)      | Regs[R1] ← Regs[R1]<br>+ Mem[1001]                                                                                                                                                                                                                                                            | Sometimes useful for accessing static data; address constant may need to be large.                                                                     |

| Memory indirect       | Add R1,0(R3)       | Regs[R1] ← Regs[R1]<br>+ Mem[Mem[Regs[R3]]]                                                                                                                                                                                                                                                   | If R3 is the address of a pointer $p$ , then mode yields $*p$ .                                                                                        |

| Autoincrement         | Add R1,(R2)+       | $\begin{array}{rrr} \texttt{Regs}[\texttt{R1}] & \leftarrow & \texttt{Regs}[\texttt{R1}] \\ & + & \texttt{Mem}[\texttt{Regs}[\texttt{R2}]] \\ \texttt{Regs}[\texttt{R2}] & \leftarrow & \texttt{Regs}[\texttt{R2}] + d \end{array}$                                                           | Useful for stepping through arrays<br>within a loop. R2 points to start of<br>array; each reference increments<br>R2 by size of an element, <i>d</i> . |

| Autodecrement         | Add R1, -(R2)      | $\begin{array}{rrr} \operatorname{Regs}[\operatorname{R2}] &\leftarrow \operatorname{Regs}[\operatorname{R2}] &- d \\ \operatorname{Regs}[\operatorname{R1}] &\leftarrow \operatorname{Regs}[\operatorname{R1}] \\ &+ \operatorname{Mem}[\operatorname{Regs}[\operatorname{R2}]] \end{array}$ | Same use as autoincrement.<br>Autodecrement/-increment can<br>also act as push/pop to implement<br>a stack.                                            |

| caled                 | Add R1,100(R2)[R3] | Regs[R1] ← Regs[R1]<br>+ Mem[100 + Regs[R2]<br>+ Regs[R3] * d]                                                                                                                                                                                                                                | Used to index arrays. May be<br>applied to any indexed addressin<br>mode in some computers.                                                            |

it examples meaning, and usage. In autoincrement/-decrement

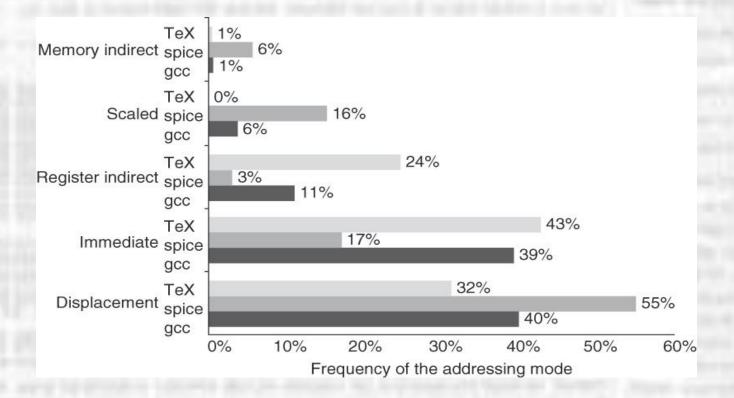

#### Addressing Modes

Addressing Modes

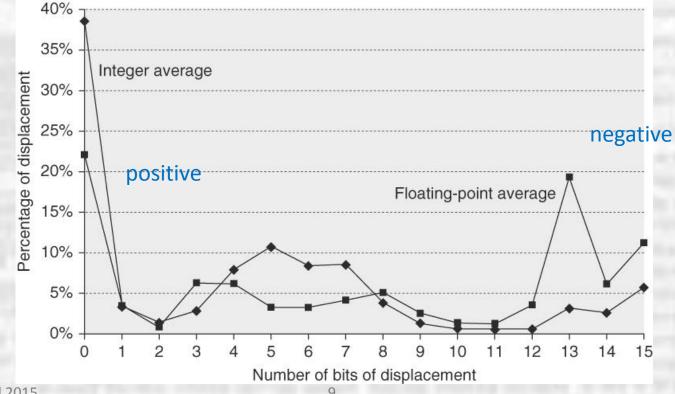

#### What does a displacement of 0 mean?

Displacement – How big?

- Addressing Modes

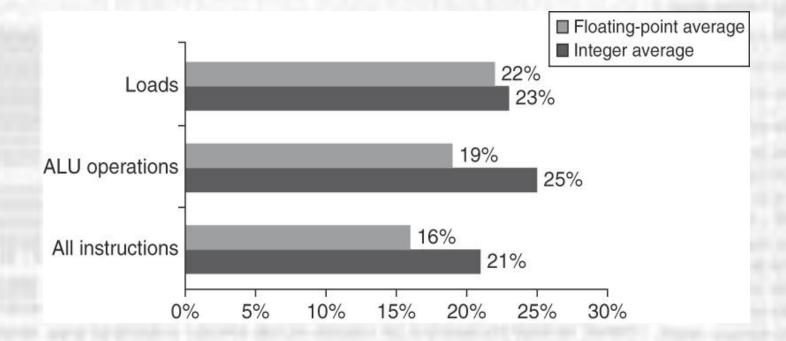

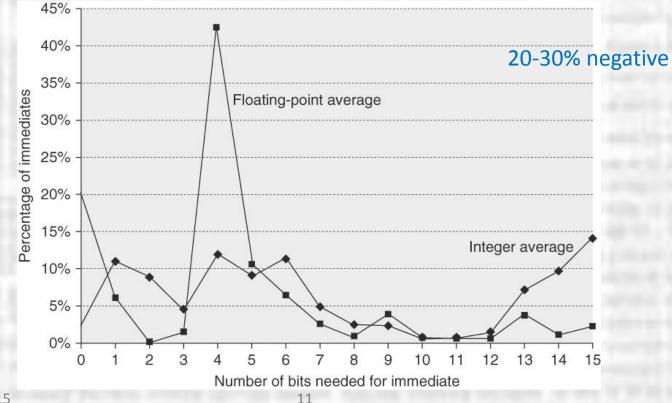

- Immediates how often?

- Addressing Modes

- Immediates how big?

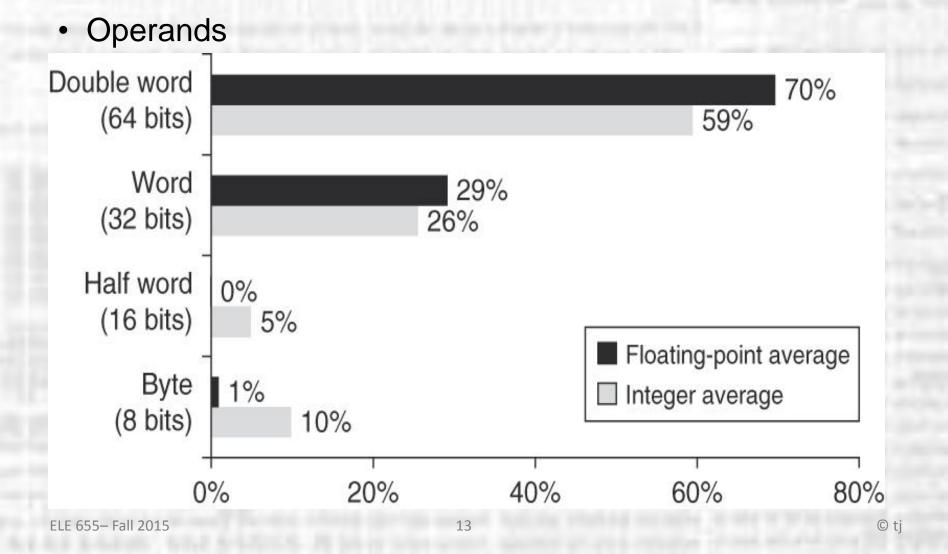

- Operands

- Integers

- 2's compliment

- Byte(8), half word(16), word(32), doubleword(64)

- Floating Point

- IEEE 754 standard

- Single precision (32), double precision (64)

- Characters

- ASCII 8 bits

- Unicode 16 bits

- BCD

#### Operations

| Operator type          | Examples                                                                            |  |  |

|------------------------|-------------------------------------------------------------------------------------|--|--|

| Arithmetic and logical | Integer arithmetic and logical operations: add, subtract, and, or, multiply, divide |  |  |

| Data transfer          | Loads-stores (move instructions on computers with memory addressing)                |  |  |

| Control                | Branch, jump, procedure call and return, traps                                      |  |  |

| System                 | Operating system call, virtual memory management instructions                       |  |  |

| Floating point         | Floating-point operations: add, multiply, divide, compare                           |  |  |

| Decimal                | Decimal add, decimal multiply, decimal-to-character conversions                     |  |  |

| String                 | String move, string compare, string search                                          |  |  |

| Graphics               | Pixel and vertex operations, compression/decompression operations                   |  |  |

#### Operations

| Rank  | 80x86 instruction                                                                                               | Integer average<br>(% total executed |

|-------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 1     | load                                                                                                            | 22%                                  |

| 2     | conditional branch                                                                                              | 20%                                  |

| 3     | compare                                                                                                         | 16%                                  |

| 4     | store                                                                                                           | 12%                                  |

| 5     | add                                                                                                             | 8%                                   |

| 6     | and                                                                                                             | 6%                                   |

| 7     | sub                                                                                                             | 5%                                   |

| 8     | move register-register                                                                                          | 4%                                   |

| 9     | call                                                                                                            | 1%                                   |

| 10    | return                                                                                                          | 1%                                   |

| Total | and prices of the second se | 96%                                  |

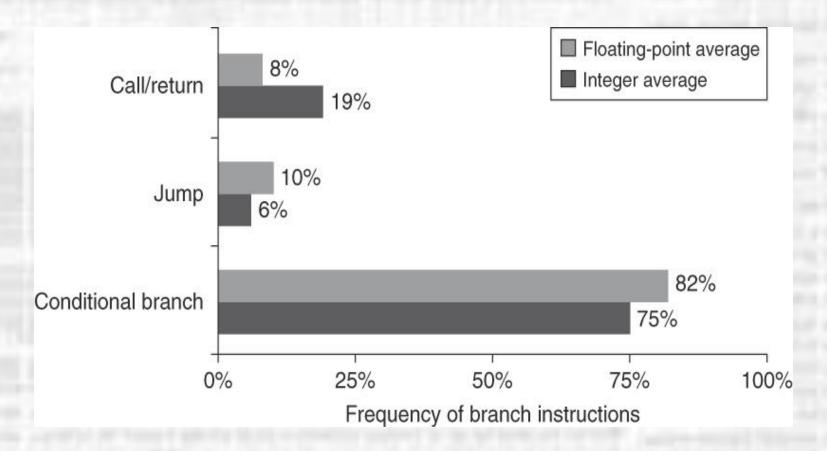

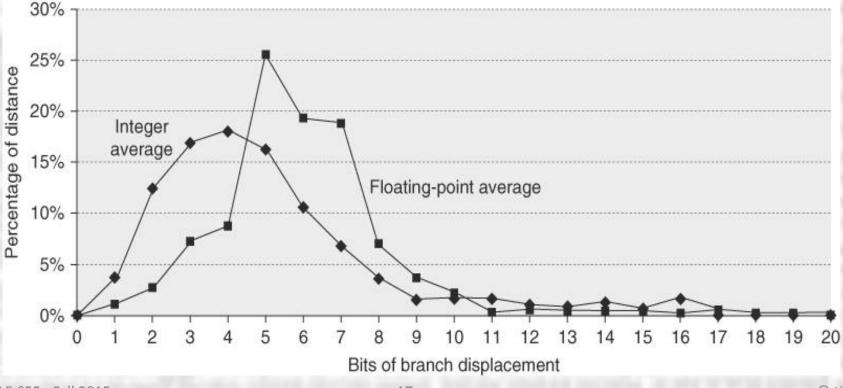

#### Operations – control flow

- Operations control flow

- Branches addresses are known at compile time PC relative

#### Operations – condition testing

| Name                   | Examples                                 | How condition is tested                                                         | Advantages                                    | Disadvantages                                                                                                                                       |

|------------------------|------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Condition<br>code (CC) | 80x86, ARM,<br>PowerPC,<br>SPARC, SuperH | Tests special bits set by<br>ALU operations, possibly<br>under program control. | Sometimes condition is set for free.          | CC is extra state. Condition<br>codes constrain the ordering of<br>instructions since they pass<br>information from one instruction<br>to a branch. |

| Condition<br>register  | Alpha, MIPS                              | Tests arbitrary register<br>with the result of a<br>comparison.                 | Simple.                                       | Uses up a register.                                                                                                                                 |

| Compare<br>and branch  | PA-RISC, VAX                             | Compare is part of the<br>branch. Often compare is<br>limited to subset.        | One instruction rather than two for a branch. | May be too much work per<br>instruction for pipelined<br>execution.                                                                                 |

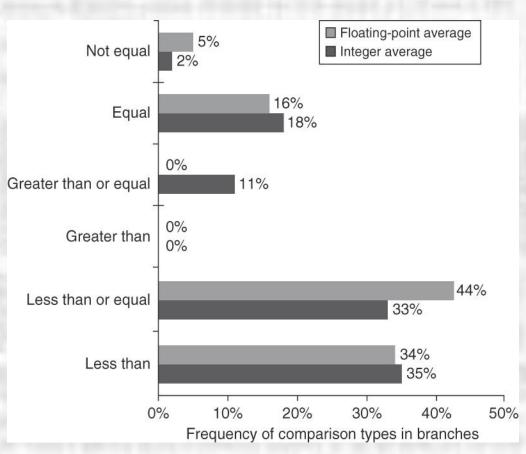

#### Operations – condition testing

#### Instruction Encoding

- Flexibility

- Code Size

#### Implementation of decode

| Operation and Address Address<br>no. of operands specifier 1 field 1 | Address specifier <i>n</i> | Address<br>field <i>n</i> |

|----------------------------------------------------------------------|----------------------------|---------------------------|

|----------------------------------------------------------------------|----------------------------|---------------------------|

(a) Variable (e.g., Intel 80x86, VAX)

| Operation | Address | Address | Address |

|-----------|---------|---------|---------|

|           | field 1 | field 2 | field 3 |

(b) Fixed (e.g., Alpha, ARM, MIPS, PowerPC, SPARC, SuperH)

| Operation | Address   | Address |

|-----------|-----------|---------|

|           | specifier | field   |

| Operation | Address     | Address     | Address |

|-----------|-------------|-------------|---------|

|           | specifier 1 | specifier 2 | field   |

#### 40% code size reduction

| Operation | Address   | Address | Address |

|-----------|-----------|---------|---------|

|           | specifier | field 1 | field 2 |

(c) Hybrid (e.g., IBM 360/370, MIPS16, Thumb, TI TMS320C54x)

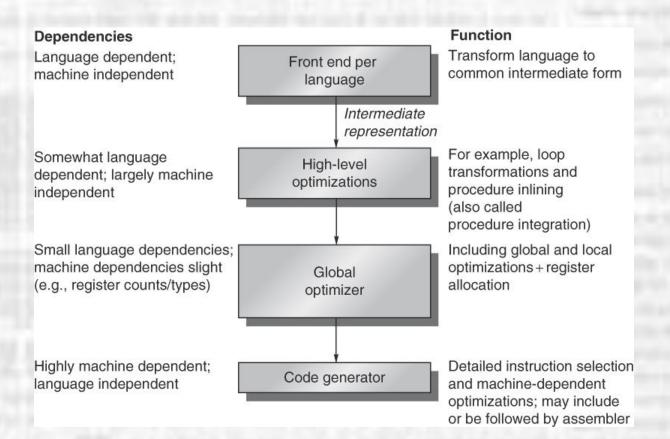

#### Compilers

- A.5

- A.8

- A.10

- A.11

- A.22

#### • A.5

- A = B + C ;The operands here are given, not computed

- by the code, so copy propagation will not

- transform this statement.

- 2. B = A + C ;Here A is a computed value, so transform

- the code by substituting

- A = B + C to get

- = B + C + C ;Now no operand is computed

- 3. D = A B; Both operands are computed so substitute

- for both to get

- = (B + C) (B + C + C); Simplify algebraically to get

#### • A.8

|                        | addr[11:10]                   | addr[9:5]          | addr[4:0]         |

|------------------------|-------------------------------|--------------------|-------------------|

| 3 two-address instr.   | '00', '01', '10'              | '00000' to '11111' | '00000' to '11111 |

| Other instructions     | '11'                          | '00000' to '11111' | '00000' to '11111 |

|                        | addr[11:10]                   | addr[9:5]          | addr[4:0]         |

| 3 two-address instr.   | '00', '01', '10'              | '00000' to '11111' | '00000' to '11111 |

| 30 one-address instr.  | '11'                          | '00000' to '11101' | '00000' to '11111 |

| 45 zero-address instr. | '11'                          | '11110'            | '00000' to '11111 |

|                        | '11'                          | '11111'            | '00000' to '01100 |

|                        | addr[11:10]                   | addr[9:5]          | addr[4:0]         |

| 3 two-address instr.   | '00', '01', '10'              | '00000' to '11111' | '00000' to '11111 |

| 24 zero-address instr. | '11'                          | '00000'            | '00000' to '10111 |

| X one-address instr.   | '11'                          | '00001' to '11111' | '00000' to '11111 |

| LE 655– Fall 2015      | The state of the state of the | 24                 |                   |

#### • A.10

Reasons to increase the number of registers include:

1. Greater freedom to employ compilation techniques that consume registers, such as loop unrolling, common subexpression elimination, and avoiding name dependences.

2. More locations that can hold values to pass to subroutines.

3. Reduced need to store and re-load values.

Reasons not to increase the number of registers include:

1. More bits needed to represent a register name, thus increasing the overall size of an instruction or reducing the size of some other field(s) in the instruction.

2. More CPU state to save in the event of an exception.

3. Increased chip area and increased power consumption.

- A.11

- $44 \rightarrow 40$

- 56  $\rightarrow$  48

| Data type | Data size on 32-bit<br>machine (bytes) | Data size on 64-bit<br>machine (bytes) |

|-----------|----------------------------------------|----------------------------------------|

| char      | 1                                      | 1                                      |

| bool      | 1                                      | 1                                      |

| int       | 4                                      | 4                                      |

| long      | 4                                      | 8                                      |

| double    | 8                                      | 8                                      |

| short     | 2                                      | 2                                      |

| float     | 4                                      | 4                                      |

| pointer   | 4                                      | 8                                      |

| a. |    |    |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|----|

|    | 43 | 4F | 4D | 50 | 55 | 54 | 45 | 52 |

|    | С  | 0  | М  | Р  | U  | Т  | Е  | R  |

| b. |    |    |    |    |    |    |    |    |

|    | 45 | 52 | 55 | 54 | 4D | 50 | 43 | 4F |

|    | Е  | R  | U  | Т  | М  | Р  | С  | 0  |

c. 4F4D, 5055, and 5455. Other misaligned 2-byte words would contain data from outside the given 64 bits.

d. 52 55 54 4D, 55 54 4D 50, and 54 4D 50 43. Other misaligned 4-byte words would contain data from outside the given 64 bits.