WEEK 2 LEARNING OBJECTIVES

Day 1

- Define synchronous sequential circuit.

- Define state.

- Define finite state machine.

- Draw the Moore and Mealy FSM models

- Compare and contrast the Mealy

and Moore models.

- Compare and contrast

current and next state.

- Define state diagram.

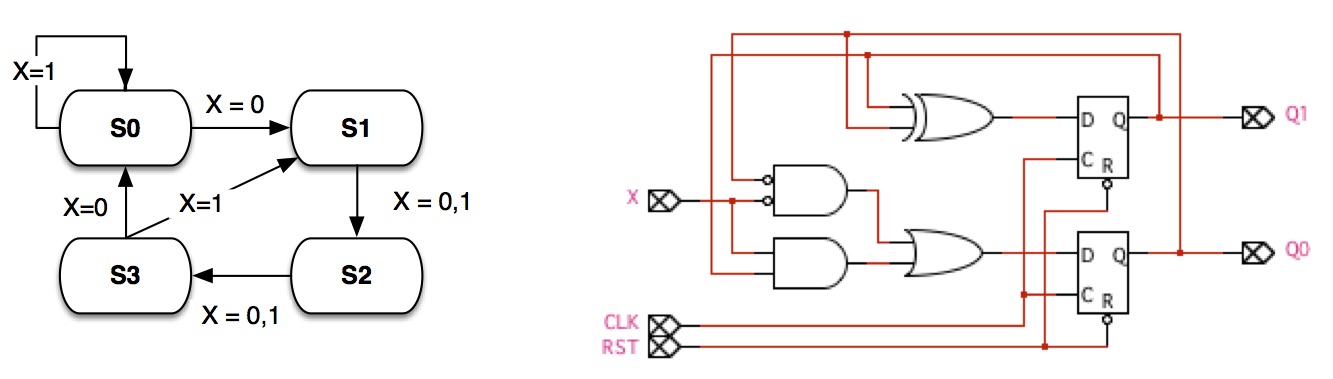

- Draw the state diagram for a Moore FSM to

be designed.

- Convert the design state diagram into a

design state table.

- Convert the design state table into a truth

table using standard binary encoding.

- Derive the next state and output

equations from the design truth table.

- Draw the state machine schematic using logic

symbols on paper.

Day 2

- Draw the state diagram for a Moore FSM to

be designed.

- Convert the design state diagram into a

design state table.

- Convert the design state table into a truth

table using standard binary encoding.

- Derive the next state and output

equations from the design truth table.

- Draw the state machine schematic using logic

symbols on paper.

- Draw a timing diagram that illustrates

asynchronous reset followed by operational FSM behavior as inputs

change.

- Implement the FSM as a Quartus schematic.

- Simulate the FSM in Quartus.

Day 3

- Draw the state diagram for a Moore FSM to

be designed.

- Convert the design state diagram into a

design state table.

- Convert the design state table into a truth

table using standard binary encoding.

- Derive the next state and output

equations from the design truth table.

- Draw the state machine schematic using logic

symbols on paper.

- Draw a timing diagram that illustrates

asynchronous reset followed by operational FSM behavior as inputs

change.

- State the standard flip-flop and register

components from the 7400 logic family.

- Draw the FSM as a 7400 logic family

schematic. Note that this schematic must show

the chips as rectangles with power, ground, inputs, outputs, and

interconnection wires shown.