WEEK 3 LEARNING OBJECTIVES

Day 1

- Describe the VHDL process statement syntax.

- State the role of the VHDL process statement

sensitivity list.

- Describe clock edges using VHDL signal attribute

syntax (name'event or name'stable).

- Describe clock edges using the VHDL IEEE

standard logic library macros rising_edge and falling_edge.

- Write a VHDL description of a 4-bit

register.

- Simulate the 4-bit register using Quartus.

- Describe the use of generics in VHDL.

- Write the VHDL description of an n-bit wide

register.

- Simulate the n-bit wide register in Quartus.

- Write the VHDL description of an n-bit wide

register with asynchronous reset and load control.

- Simulate the n-bit wide register with

asynchronous reset and load control in Quartus.

Day 2

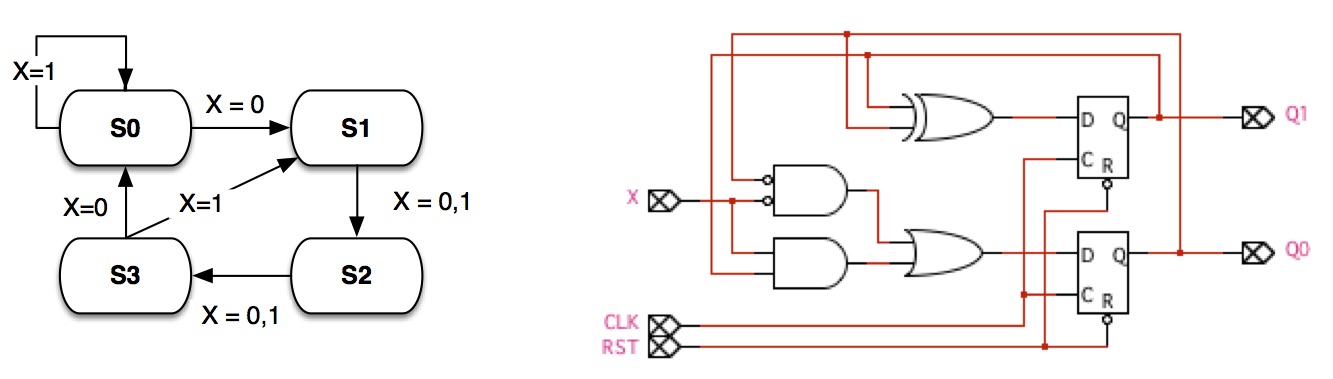

- Draw the state diagram for a Moore FSM to

be designed.

- Convert the design state diagram into a

design state table.

- Implement the design FSM using VHDL abstract

state types, when-else, and with-select statements.

- Simulate the state machine to verify correct

operation.

Day 3

- Draw the state diagram for a Moore FSM to

be designed.

- Convert the design state diagram into a

design state table.

- Implement the design FSM using VHDL abstract

state types and case statements.

- Simulate the state machine to verify correct

operation.