WEEK 4 LEARNING OBJECTIVES

Day 1

- Describe the one-hot state encoding.

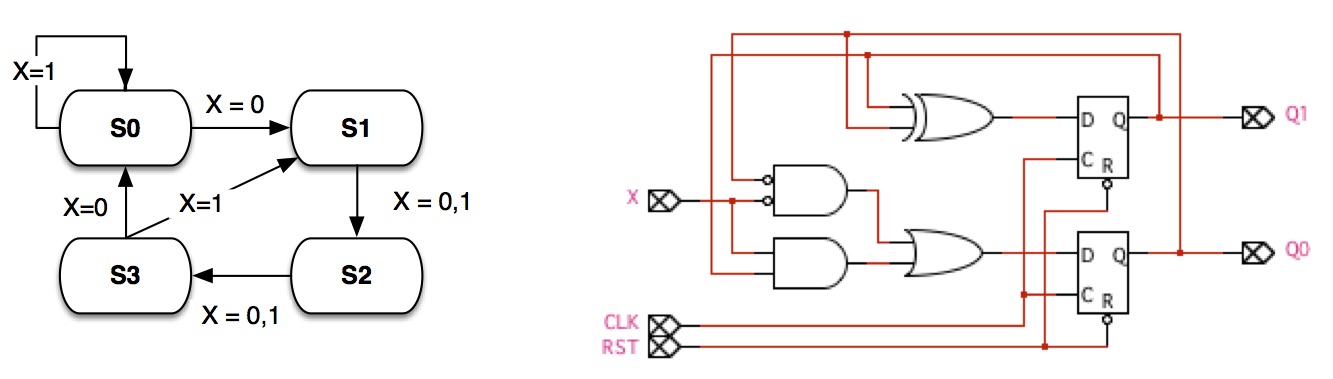

- Draw the state diagram for a Moore FSM to

be designed.

- Convert the design state diagram into a

design state table.

- Convert the design state table into a truth

table using one-hot encoding.

- Derive the next state and output

equations from the design truth table.

- Draw the state machine schematic using logic

symbols on paper.

- Draw a timing diagram that illustrates

asynchronous reset followed by operational FSM behavior as inputs

change.

- Draw the FSM as a 7400 logic family schematic.

Day 2

- Draw the state diagram for a Moore FSM to

be designed.

- Convert the design state diagram into a

design state table.

- Convert the design state table into a truth

table using one-hot encoding.

- Derive the next state and output

equations from the design truth table.

- Describe the FSM in VHDL using fixed numbers rather

than abstract state types.

- Simulate the FSM in Quartus.

- State why one-hot encoding has become a

dominant encoding scheme in FPGA synthesis tools like Quartus.

Day 3

- Describe Gray Code.

- Draw the state diagram for a Moore FSM to

be designed.

- Convert the design state diagram into a

design state table.

- Convert the design state table into a truth

table using Gray code.

- Derive the next state and output

equations from the design truth table.

- Describe the FSM in VHDL using fixed numbers rather

than abstract state types.

- Simulate the FSM in Quartus.

- State how Gray Code helps low-power design.