WEEK 5 LEARNING OBJECTIVES

Day 1

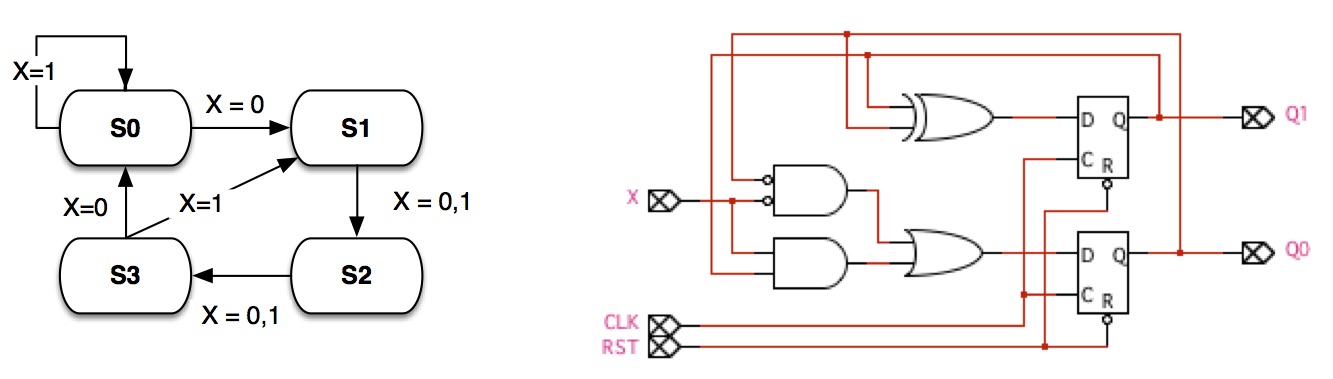

- Draw the state diagram for a Moore or Mealy FSM to be

designed.

- Convert the design state diagram into a

design state table.

- Describe the use of the VHDL keyword type to declare

a user enumerated list of abstract state names.

- Implement the state machine using when-else, process, and with-select

blocks for the next state, memory, and output signal logic blocks.

Use signals D and Q of abstract state type.

- Simulate the state machine to verify operation.

- Examine the Quartus state machine viewer to verify the generated FSM.

- Use the Quartus Advanced Synthesis Compiler Settings to control the

state machine encoding. Verify the encoding in the state machine viewer.

- Describe how the VHDL constant keyword can be used to declare

state encodings, seven-segment display encodings, etc.

Day 2

- Draw the state diagram for a Moore or Mealy FSM to be

designed.

- Convert the design state diagram into a

design state table.

- Implement the state machine using abstract state types and

a single state machine process based on the switch-case mechanism.

- Describe the VHDL switch-case mechanism (case-when, if-then-else, end case).

- Simulate the state machine to verify operation.

- Examine the Quartus state machine viewer to verify the generated FSM.

- Use the Quartus VHDL state encoding attribute to control the

state machine encoding. Verify the encoding in the state machine

viewer.

- Justify the use of the all keyword in the VHDL process

sensitivity list.

Day 3

- This day is reserved for review, expanded coverage, or mid-term exams for

instructors giving mid-terms.