WEEK 7 LEARNING OBJECTIVES

Day 1

- List the five classic counters.

- Describe the state diagrams of the five

classic counters.

- Draw timing diagrams illustrating the five

classic counters with asynchronous reset and load control.

- Compare and contrast

saturating and non-saturating counters.

- Draw saturating and non-saturating counter behaviors

on timing diagrams.

Day 2

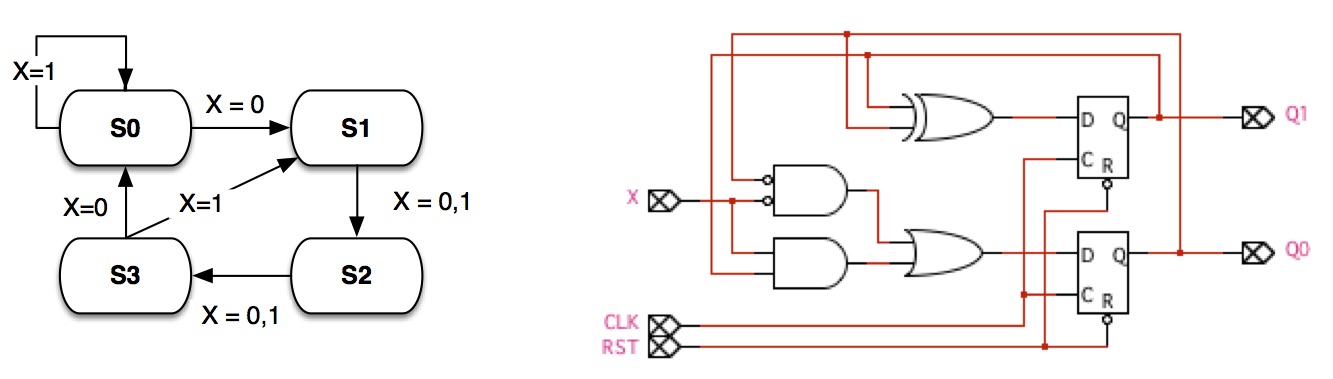

- Draw the state diagram for the FSM of a

counter to be designed.

- Convert the design state diagram into a

design state table.

- Derive the output and excitation

equations for the design FSM from the design state table.

- Draw the state machine using logic

symbols.

- Write the VHDL description using abstract

state types. Simulate to verify correct

operation.

- Write the VHDL description using fixed

numbers instead of abstract types. Simulate to

verify correct operation.

Day 3

- Examine the 74191 datasheet.

- Modify the 74191 standard counter using control

circuitry created with gates so that it counts a modulo-n or BCD sequence.

- Modify the 74191 standard counter using control

circuitry created with gates so that it acts as a saturating counter.

- Analyze a given 74191 counter circuit to determine

the count sequence.

- Draw timing diagrams of 74191 counter circuit

behavior including MAX/MIN and RCO outputs.